# The design of tunable photonic crystal biosensor with the integration of PN phase shifter using PIC design approach

Mohamad Hazwan Haron, Dilla Duryha Berhanuddin, Sahbudin Shaari, Burhanuddin Yeop Majlis, Ahmad Rifqi Md Zain.

Institute of Microengineering & Nanoelectronics (IMEN),

Universiti Kebangsaan Malaysia (UKM),

43000 Kajang, Selangor, MALAYSIA.

Email: rifqi@ukm.edu.my

**Abstract**—Silicon-based photonic integrated circuit (PIC) is a research focus in producing high-density photonics. One of the potential applications of silicon PIC is the sensing and measurement system. In this work, we use the one-dimensional photonic crystal (1D-PhC) cavity design which and utilize it at the PIC level design. The 1D PhC design used as the compact model has the same characteristics as experimentally demonstrated in previous works. The compact model is made from the S-parameter extraction of the 1D-PhC device which is done by using Lumerical FDTD software. The PIC design integrates the 1D-PhC device as a sensing component with a PN-phase shifter (PN-PS) to function as a refractive index (RI) sensor calibration or tuning circuit. A custom design of PN-PS device is used by simulating and extracting the bias voltage-effective index (bias-Neff) data by using Lumerical DEVICE and MODE into the circuit simulator. The circuit-level simulation is done by using Lumerical Interconnect software. Finally, we show the GDSII layout design of the 1D-PhC based photonic sensor calibration circuit with an analysis of generic silicon PIC design rules. The designed PIC is applicable for the bio-sensing applications and photonic SOC component. This work also shows the promise of PIC design approach for further PIC development.

**Keywords**— *Photonic compact model, silicon photonic integrated circuit (PIC), photonic crystal cavity refractive index sensor, tunable sensing circuit, photonic layout rules.*

## I. INTRODUCTION

Advanced biomedical trend such as personalized diagnosis requires the miniaturization of biomedical instruments. One of the technology to realize this is the integrated design such as CMOS and BiCMOS. However, for photonics-based design, traditional discreet photonics results in bulky and bigger instruments. The solution to this is the creation of the photonic integrated circuit (PIC) design approach. The idea of PIC is driven by the already successful development of high-density electronics, particularly CMOS VLSI and the need for high-speed optical communication systems and components [1], [2]. What makes this technology attractive is also because of the reusability of the CMOS fabrication infrastructure for the on-rising silicon photonic platform [2][3]. Thus, silicon photonics has the potential for high-density PIC and the development of photonic system-on-chip (P-SOC) [4].

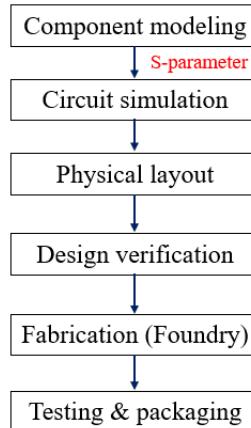

To realize this complex system requires a proper set of design tools and design methodology. There has been an effort to develop the Silicon PIC design flows and tools [5], [6]. The developed Silicon PIC design flow utilizes a design flow similar to ASIC design flows particularly analog ASIC, which utilizes the electronic design automation (EDA) tools consisting of three main levels: schematic design, layout design and design verification before it goes to tape-out. The complete silicon photonic design flow is shown in figure 1, which has been described in [5], [7]. In silicon photonics, a GDSII file format layout is usually made which is required for electron beam lithography (EBL) patterning process [8] during the fabrication phase.

**Fig. 1.** Silicon photonic system design flow [5].

In usual electronics and photonics design flow, there is a part of creating a custom compact model of a designed device for circuit-level simulation. The compact model can be made from the scattering parameter (S-parameter) extraction of the simulated device. In electronics, the S-parameter describes the response of an electrical or photonic device as a function of frequency. Experimentally, the S-parameter can be characterized by using an electrical network analyzer (ENA) for an electrical device and an optical network analyzer (ONA) for a photonic device [9].

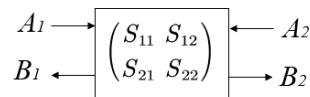

The S-parameter data is an array of matrices containing the scattering data at its ports. It can represent how a device behaves from a black-box point of view. A two ports device would have a  $2 \times 2$  matrix for its S-parameter as illustrated in figure 2.

**Fig. 2.** An illustration of a matrix for a two-ports network

The full equation of the transfer matrix is given as follows,

$$\begin{pmatrix} B_1 \\ B_2 \end{pmatrix} = \begin{pmatrix} S_{11} & S_{12} \\ S_{21} & S_{22} \end{pmatrix} \begin{pmatrix} A_1 \\ A_2 \end{pmatrix} = S \begin{pmatrix} A_1 \\ A_2 \end{pmatrix} \quad (1)$$

Where  $A_1$  is the input light into the device through port 1,  $B_1$  is the reflected light, and  $B_2$  is the transmitted light. A circuit simulator usually simply solves this kind of matrix equations from component to component to get results.

In silicon photonics research, there has been a lot of research done on device-level photonics. Two main classifications of photonic devices are passive and active devices. The usual passive devices used in PIC design are photonic waveguide (photonic wire) [10], 90° bent waveguide [11], directional coupler [12], Y-branch [13], Mach-Zehnder interferometer (MZI) [14], [15], ring resonator [16] and Bragg grating [17], [18]. Ring resonator and Bragg grating are conventionally used for filtering and peak generation. The usual active photonic devices are first the modulator or tuner are usually PN-phase shifter [19], [20], micro-ring modulator [21] and thermo-optic phase shifter [22], and other important active devices are photodetector and laser. The main material for silicon photonics is silicon-on-insulator (SOI).

Because there have been a lot of researches at the photonic device level [23], the photonic device research can be considered as matured at this time, although more new devices can be created as needed. The next step from the device level development is to go into the development of integrated-circuit level photonics that utilizes those developed photonic devices. This can be done by creating the compact model from any of the previously developed devices.

Although previous PIC works are mostly for the optical communication system, there is also another need for developing PIC blocks for optical measurement systems or SOC such as for bio-sensing systems [24]. This is because photonic sensors are very sensitive which makes them suitable for biosensor and micron-scale detection. This paper focuses on this application.

In our previous works, we have shown that the 1D-PhC sensor's output peak will shift on its wavelength when there is a change of its surrounding refractive index (RI) [25], [26]. The 1D-PhC device has the advantage of having a sharp single peak characteristic as compared to the conventional Mach-Zehnder interferometer (MZI) device which can be designed at c-band wavelength and also accurately at 1550 nm [27], [28]. The sharp peak characteristic can be used as the sensing signal. It is also possible to use 1D PhC as a one-port device, which utilizes the same path as the input and output [29].

However, biosensing measurement depends on a strict standard, so there is a need to calibrate the system for accurate measurement. The other factor that can disturb the accuracy of the measurement is the temperature influence. So, a tuner is one of the solutions that can be used for this issue.

In this work, we integrate the 1D-PhC biosensor with the PN phase shifter to make a tunable bio-sensing PIC. The 1D-PhC biosensor component can sense the different concentrations of an analyte by sensing the RI change around its surrounding. The transmitted light signal from the 1D-PhC goes through the PN-PS component before goes out to the output coupler. If the RI inside the PN-PS is changed, the phase of the light signal which goes through it will be changed. This effect can be used to tune the resonance wavelength. The effect of RI change in crystalline silicon due to biasing voltage and charge carriers was first predicted by Soref and Bennett in 1987 [30]. Previous researches have shown the tunability of the resonance wavelength either by thermo-optic or plasma dispersion effect. In this work, the plasma dispersion effect is used to control the RI inside the PN-PS by controlling the applied bias voltage of the PN-PS.

The PIC design flow is followed to build a functional PIC schematic and final GDSII layout. The result from the 1D-PhC design shows that the resonance peak's wavelength will change when there is a change in the surrounding RI of the 1D-PhC. The result from the integrated 1D-PhC with PN-PS shows the shift of resonance peak when the PN-PS reverse bias voltage is increased. The results show the success of this work to design a tunable biosensing PIC which gives a miniature solution to tune or calibrate the biosensor for measurement accuracy.

## II. METHODOLOGY

Referring to the general silicon photonic design flow shown in figure 1, only the component modeling until physical layout design will be shown in this work. The design verification is done by comparing to specific design rules. Here, an analysis of the layout design with generic silicon photonic design rules will be discussed.

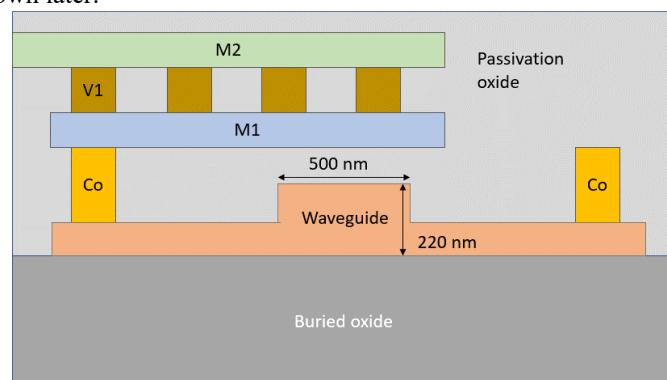

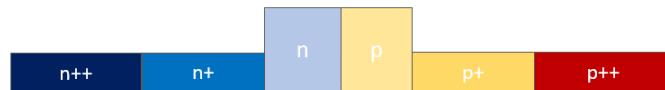

Before the design is started, the overall cross-section of the designed chip will be identified to understand the circuit and the implementation of the physical layout design. The main material of the wafer used in this design is silicon-on-insulator (SOI), which is the standard material for silicon photonics. The cross-section of the most complex component used in this design, which is the PN-PS will be identified first because it contains almost all physical layers used in the design. The cross-section of the PN-PS together with its interconnect components is shown in figure 3. Only PN-PS uses the rib waveguide in the circuit. The other photonic components in the designed circuit use strip waveguide.

All waveguides material is silicon. All waveguide's width is 500 nm. In the PN-PS design, the metal 2 (M2) connects the device from the outside, which is from the electrical pad. M2 is connected to metal 1 (M1) through via 1 (V1). M1 is used for the inside interconnect of the PN-PS and is connected to the Si rib waveguide through contact (CB). This cross-section is identical to the common CMOS IC design. By seeing this most complex device's cross-section, we have seen most physical layers used in the layout design except the electrical pad layer. Other additional layers in the layout design include the doping regions of the PN-PS. The doping regions of the PN-PS will be shown later.

**Fig. 3.** The cross-section's view at PN-phase shifter as the region of the most complex layer in the PIC chip.

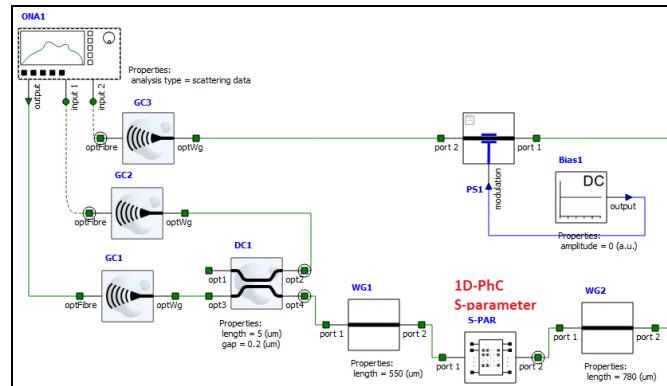

The objective of the design is to utilize the 1D-PhC device as the resonator and sensing element, then make the resonance wavelength-tunable for calibration purposes. This can be done by integrating the 1D-PhC with the PN-PS device. The schematic design of the PIC is shown in figure 4.

The circuit uses ONA as both the light source and signal analyzer. The grating couplers designated as GC1, GC2, and GC3 are used as the coupling components to couple light into and out of the chip. Other than grating couplers, an edge-coupler can also be used. Utilizing the flexibility of PIC design, a reference output can be added to the circuit by splitting the input light by using a directional coupler (DC1). The reference output goes out through GC2. It can be also used as a signal checker. Other than the directional coupler, a Y-splitter can also be used to split the light. However, a common Y-splitter will split the light equally into two directions, resulting in an unnecessary transmission loss for the main purpose. That is why a directional coupler is used here, which is only about 15% of the light would be coupled across the directional coupler and goes to the reference output.

The data of the extracted S-parameter of the 1D-PhC device will be uploaded to the S-PAR component to make the 1D-PhC compact model. The waveguides length between the 1D-PhC component is taken with the consideration of the final GDSII layout which will be shown later. Other than 1D-PhC S-parameter data, specific data for the PN-PS component (PS1) must also be uploaded, which is the voltage bias-RI response data, rather than using the generic data in the circuit simulator. This is because we are not using a pre-designed model of the PN-PS for the final GDSII layout, so a custom design needs a thorough simulation to make sure the accuracy of the results, and the objective to design a tunable sensing PIC with a manufacturing-ready layout is achieved. Because the PN-PS is the most complex component and acts as the controlling element in the circuit, it must be thoroughly designed and simulated. The PN-PS length is set to 1 mm, which is very long compared to the 1D-PhC device which is about 25 $\mu$ m long. The PN-PS will be connected to the electrical pads for biasing.

**Fig. 4.** The full PIC schematic for the tunable sensing circuit.

The design of the 1D-PhC which will be converted into the compact model is shown in figure 5. The 1D-PhC uses uniform holes of 50 nm radius ( $r$ ), with the periodicity ( $a$ ) of 400 nm, a cavity ( $c$ ) of the length of 490 nm and number of holes of 50. The design parameters are chosen by understanding how the parameters change will affect the 1D PhC output and have been shown in the previous work [31]. The 1D-PhC structure will be simulated by using Lumerical FDTD software and the S-parameter will be extracted and transferred to Lumerical Interconnect for circuit-level simulation.

**Fig. 5.** The design of 1D-PhC used to make the compact model.

Next, the PN-PS device will be designed and simulated. A specific PN-PS structure will exhibit a different characteristic in terms of the effective index response to the voltage bias (bias-Neff).

The width of the depletion region ( $W_d$ ) of a PN-PS is given by [7],

$$W_d = \sqrt{\frac{2\epsilon_0\epsilon_s(V_{bi} - V)(N_A + N_D)}{qN_A N_D}} \quad (2)$$

Where  $\epsilon_s$  is the relative permittivity,  $V_{bi}$  is the built-in potential at the junction,  $V$  is the voltage bias,  $N_A$  and  $N_D$  are the doping concentration of holes and electrons. Based on equation 2, two ways are known to increase the depletion width of a PN-PS can be which is by increasing the carriers' concentration by doping or increasing the

bias voltage. In this PN-PS design, the doping concentration will be fixed and the bias voltage will be varied to vary the depletion width. However, it should be noted that the change in voltage bias should change the carrier concentration at the PN-junction.

The change in RI at 1550 nm is described by the following equation [32],

$$\Delta RI = -5.4 \times 10^{-22} (\Delta N_D)^{1.011} - 1.53 \times 10^{-18} (\Delta N_A)^{0.838} \quad (3)$$

The doping region of the PN-PS rib waveguide is shown in figure 5. The doping concentration is  $1 \times 10^{18} \text{ cm}^{-3}$  for n and p region,  $1 \times 10^{19} \text{ cm}^{-3}$  for n+ and P+ region and  $1 \times 10^{20} \text{ cm}^{-3}$  for n++ and p++ region. The PN-PS structure will be simulated using Lumerical DEVICE's Charge solver. The voltage bias of the PN-PS device is set from 0 to -20V. 20V is considered a high voltage for a chip application, but to realize the tunable sensing circuit, it is a reasonable value to be used. Lumerical DEVICE simulates the charge profile of the device, to get the effective index response, Lumerical MODE will be used by uploading the charge simulation data from Lumerical DEVICE. This bias-Neff result is important information to show that the tunable circuit sensing will work as we want it to be. The specific bias-Neff response data will be transferred to Lumerical Interconnect.

**Fig. 5.** PN-PS structure and the doping regions used in the simulation.

After finishing the device-level design and simulations, all data which are the 1D-PhC S-parameter and bias-Neff data will be uploaded to the circuit schematic shown in figure 3, then the circuit will be simulated. The circuit simulation results should show that the tunable sensing PIC design objective is achieved, which output peak will shift when the bias voltage value is varied. Some of the components' value of the PIC schematic will be updated after the GDSII layout design is finished to make sure the accuracy of the results needed.

Finally, a GDSII format physical layout will be designed by using KLayout software. The designed GDSII layout will be made for fabrication-ready design. The designed GDSII layout in this work will be manually analyzed according to generic silicon photonic design rules as stated in [7] and some rules are based on device design. The waveguide routing will be done by using the open-source SiEPIC toolkit. The components or cells which will be used in the GDSII layout are the combinations of the pre-designed library from SiEPIC process design kits (PDKs) and custom-designed cells. The custom-designed cells here are the 1D-PhC and the PN-PS devices.

### III. RESULTS AND DISCUSSION

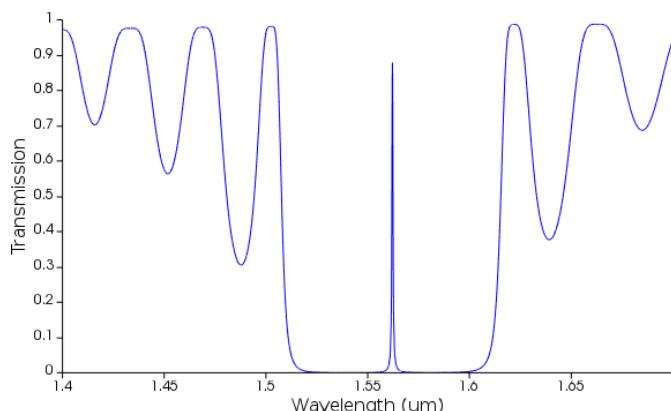

The 1D-PhC device shown in figure 4 is simulated in Lumerical FDTD by using 2D FDTD solver with an effective index value and S-parameter extraction setup. The transmission result of the 1D-PhC device is shown in figure 6, which shows a single peak output in the middle of a bandgap. The peak is at 1561.8 nm wavelength which is around the center of the targeted C-band wavelength. The normalized transmission value of the peak is 0.879, which means 12.1% of light loss at the peak and across the device. This amount of light loss should be considered for the final PIC design. The S-parameter data of the 1D-PhC is extracted and will be uploaded into Lumerical Interconnect for the PIC schematic simulation.

**Fig. 6.** The transmission of the 1D-PhC device simulated by using 2D FDTD solver with an effective index method.

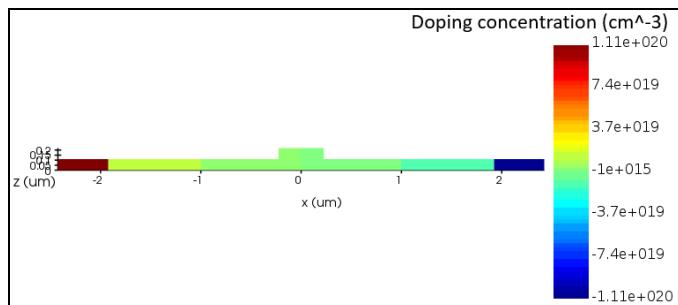

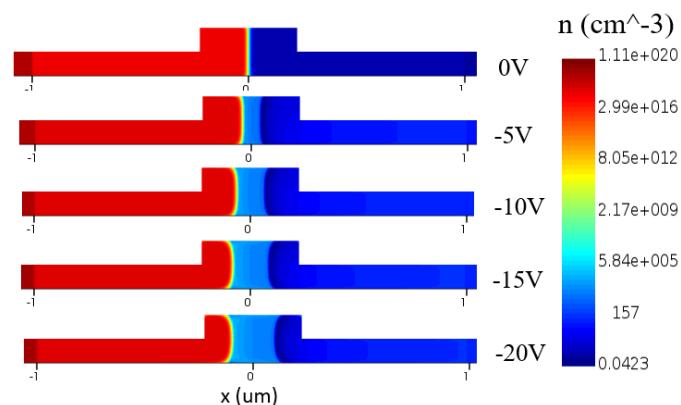

Next, the PN-PS is simulated in Lumerical DEVICE. The doping profile simulation is shown in figure 7. From the rib edge, the doping is gradually reduced from around  $1 \times 10^{20} \text{ cm}^{-3}$  to  $1 \times 10^{19} \text{ cm}^{-3}$  and  $1 \times 10^{18} \text{ cm}^{-3}$ . Then, the simulation of the charge by varying the bias voltage and its effect on the depletion region is shown in figure 8. The result shows that as the bias voltage is increased in reversed from 0V to -20V, the depletion region width keeps increasing. This is the reason a higher reversed bias voltage which is until -20V is considered so that there are more changes to the guiding region of light mode which should change the effective index of the PN-PS waveguide.

**Fig. 7.** The doping profile of the PN-PS.

**Fig. 8.** Charge profile focusing at the center of the PN-phase shifter. The depletion region at pn-junction increases as the bias voltage is increased.

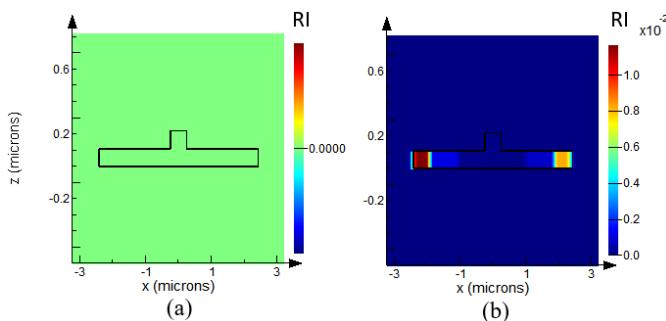

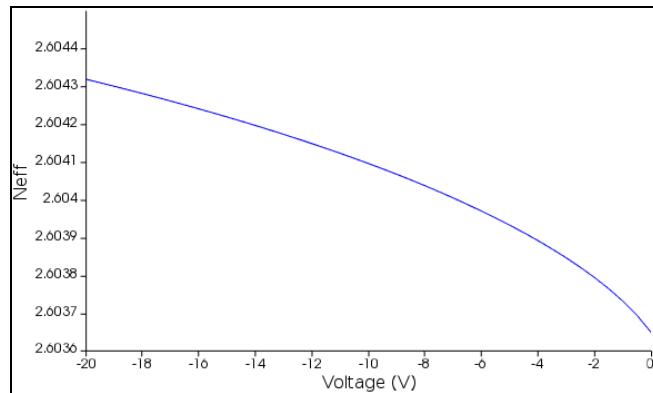

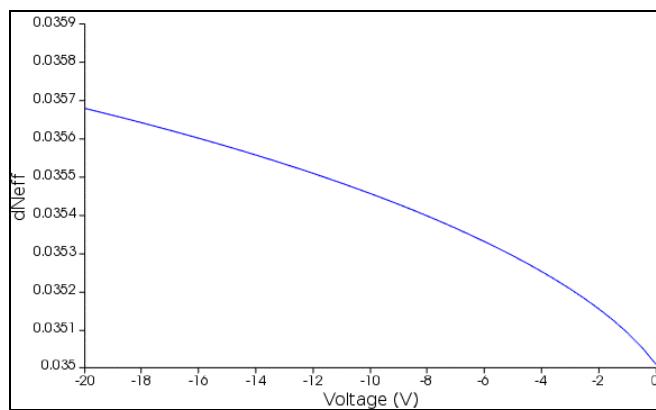

To see the effective index change, the simulated charge profile data is uploaded to Lumerical MODE to simulate the rib waveguide with charge. Running the modal analysis, the result of the refractive index profile can be seen. Figure 9 shows the comparison of the imaginary RI profile of the uncharged waveguide for the PN-PS device (9a) and charged waveguide (9b). The imaginary RI in the uncharged waveguide is zero while the imaginary RI in the charged waveguide has a value. It shows the charged waveguide will exhibit some optical loss due to absorption [32]. Next, running the bias voltage sweep, the result of bias-Neff is shown in figure 10. It shows that the Neff increases in square root relation with the voltage. The change of Neff between undoped and charged PN-PS rib waveguide with bias voltage variation is shown in figure 11.

**Fig. 9.** Imaginary RI (loss) of (a) undoped waveguide and (b) doped waveguide

**Fig. 10.** Effect of bias voltage variation to the effective index of the rib waveguide for the PN-PS device.

**Fig. 11.** The change of Neff between undoped and charged PN-PS rib waveguide with bias voltage variation.

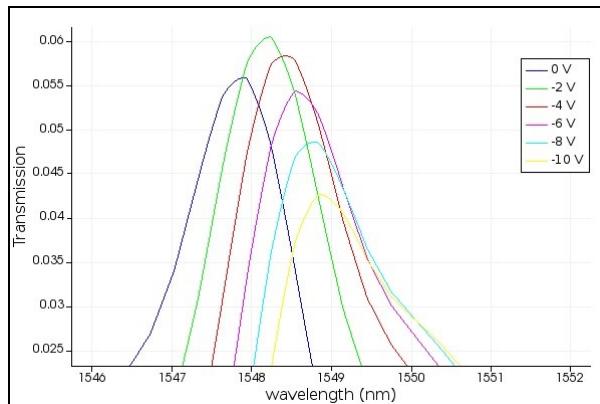

With the finished simulation at the device level, the 1D-PhC's S-parameter and PN-PS bias-Neff data are now ready to be transferred to Lumerical Interconnect for circuit level simulation. The PIC schematic shown previously in figure 3 is now simulated. The simulation result of the designed tunable sensing PIC is shown in figure 12. The result shows the shift of the peak with by varying the bias voltage from 0 to -10 V as expected. Increasing the reverse bias voltage, the peak shows the redshift effect, which is going to the longer wavelength. However, as the reverse bias voltage increases, the peak's amplitude reduces.

**Fig. 12.** The result of PIC schematic simulation shows that the wavelength of the peak signal can be tuned by varying the bias voltage of the PN-PS component.

The reducing amplitude of the peak is due to the absorption effect due to the changing concentration of charge carriers and has been described by the following equation. At 1550 nm, the change of the absorption ( $\alpha$ ) has been described by the following equation [7],

$$\Delta\alpha = 8.5 \times 10^{-18} \Delta N + 6 \times 10^{-18} \Delta P \quad (4)$$

The absorption effect shows that the PN-PS can also be used for amplitude modulation applications. However, since in this work only wavelength tuning is needed, the reducing amplitude of the peak is considered a trade-off for the wavelength tuning.

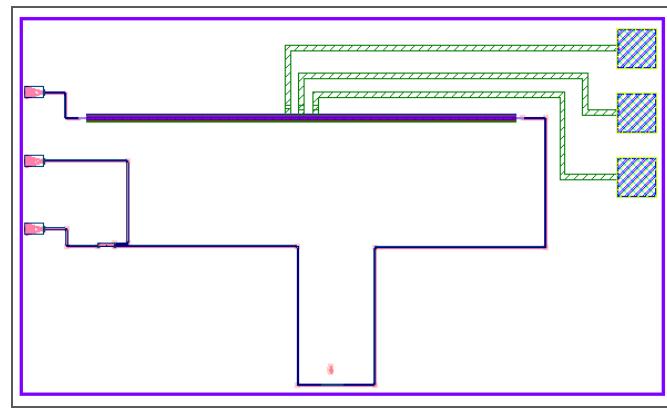

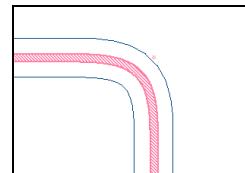

Finally, the illustration of the fabrication ready GDSII layout is drawn as shown in figure 14. The layout follows generic silicon PIC design rules. The main rule is about the spacing of the edge or grating coupler and the electrical pads which depends on the separation of the test probes. The grating couplers and the electrical pads in the layout are placed on different sides because of the size of the test probes that would make it impossible to put both input and output components on the same side. The next rule is that the Si waveguide routings cannot be overlap because they are on the same layer. Then, the waveguide must be accurately aligned with the component's input or output. The waveguide bend will be of 5  $\mu\text{m}$  radius as shown in figure 15 and as pre-set in routing setup. Finally, the metal wire routing requires that M2 layer be used. M2 layer is needed for device interconnection because using M1 alone would be tedious for a more complex PIC design.

**Fig. 14.** The final GDS layout illustration of the designed PIC for prototyping, following the common silicon photonics technology design rules.

**Fig. 15.** The layout of waveguide bend with 5  $\mu\text{m}$  bend radius. The waveguide is surrounded by block fills.

The results of this research show the success of designing and simulating a tunable sensing circuit utilizing a 1D-PhC custom compact model integrated with a PN-PS device which is done by following the silicon PIC design approach. The results also show the promise of PIC design approach to develop more circuits and blocks design to obtain a high-density PIC. Potential applications from PIC would be almost as same as electronics such as communications, sensing and measurement, computing, and others that are related. Right now, the combination of electronics and photonics chips to develop the SOCs is necessary. Using the same fabrication processes as CMOS, the co-design of CMOS-silicon PIC or the integration of it has huge potentials and more researches about this is needed.

#### IV. CONCLUSIONS

We have designed and simulated a tunable sensing PIC by employing a 1D-PhC custom compact model which is not yet utilized at PIC level design. The design follows the silicon photonic integrated circuit design methodology. The 1D-PhC compact model is made from the S-parameter extraction of the device level simulation by using 2D FDTD solver with the effective index value in Lumerical FDTD software. To realize the tunable sensing PIC, the PN-PS has been designed and simulated to extract the bias-Neff data by using the Lumerical DEVICE and MODE software and uploaded into the PN-PS compact model. The final PIC schematic with the uploaded data of 1D-PhC's S-parameter and PN-PS's bias-Neff has been simulated and the simulation result shows the shift of the peak signal as the bias voltage is varied. Finally, a GDSII layout has been designed analyzed by using generic silicon PIC design rules for fabrication purposes.

### ACKNOWLEDGEMENT

The authors would like to thank Ministry of Higher Education (MOHE) for the support of this work under the LRGS/2015/UKM-UKM/NANOMITE/04/01. We also would like to show our appreciation for all contributors of the open source silicon photonic SiEPIC toolkit and KLayout software.

### REFERENCES

- [1] P. P. Absil, P. Verheyen, P. De Heyn, M. Pantouvaki, and G. Lepage, “Silicon photonics integrated circuits : a manufacturing platform for high density, low power optical I / O ’ s,” *Opt. Express*, vol. 23, no. 7, pp. 9369–9378, 2015.

- [2] G. Koblmüller *et al.*, “Roadmap on silicon photonics,” *J. Opt.*, vol. 18, no. 7, 2016.

- [3] B.-J. Tom, T. Pinguet, patrick Lo Guo-qiang, S. Danziger, D. Prather, and M. Hochberg, “Myths and rumours of silicon photonics,” *Nat. Photonics*, vol. 6, no. August 2008, pp. 206–208, 2012.

- [4] F. Kish *et al.*, “System-On-Chip Photonic Integrated Circuits ( Invited ),” no. c, 2017.

- [5] L. Chrostowski *et al.*, “Design methodologies for silicon photonic integrated circuits,” in *Smart Photonic and Optoelectronic Integrated Circuits XVI*, 2014, vol. 8989, pp. 1–15.

- [6] W. Bogaerts and L. Chrostowski, “Silicon Photonics Circuit Design : Methods, Tools and Challenges,” *Laser Photonics Rev.*, vol. 1700237, pp. 1–29, 2018.

- [7] L. Chrostowski and M. Hochberg, *Silicon Photonics Design: From Devices to Systems*. Glasgow: Cambridge University Press, 2015.

- [8] L. Chrostowski *et al.*, “Silicon Photonic Circuit Design Using Rapid Prototyping Foundry Process Design Kits,” *IEEE J. Sel. Top. Quantum Electron.*, no. c, pp. 1–26, 2019.

- [9] S. S. Substrate, Y. Eo, W. R. Eisenstadt, S. Member, and J. Shim, “S -Parameter-Measurement-Based High-Speed Signal Transient Characterization of VLSI Interconnects on,” *IEEE Trans. Adv. Packag.*, vol. 23, no. 3, pp. 470–479, 2000.

- [10] E. Dulkeith, F. Xia, L. Schares, W. M. J. Green, and Y. A. Vlasov, “Group index and group velocity dispersion in silicon-on-insulator photonic wires,” *Opt. Express*, vol. 14, no. 9, pp. 1249–1251, 2006.

- [11] M. Cherchi, S. Ylinen, M. Harjanne, M. Kapulainen, and T. Aalto, “Dramatic size reduction of waveguide bends on a micron-scale silicon photonic platform,” *Opt. Express*, vol. 21, no. 15, pp. 819–821, 2013.

- [12] A. Prinzen, M. Waldow, and H. Kurz, “Fabrication tolerances of SOI based directional couplers and ring resonators,” *Opt. Express*, vol. 21, no. 14, pp. 21–26, 2013.

- [13] Y. Zhang *et al.*, “A compact and low loss Y-junction for submicron silicon waveguide,” *Opt. Express*, vol. 21, no. 1, pp. 1310–1316, 2013.

- [14] T. Mizuno, H. Takahashi, T. Kitoh, M. Oguma, T. Kominato, and T. Shibata, “Mach – Zehnder interferometer switch with a high extinction ratio over a wide wavelength range,” *Opt. Lett.*, vol. 30, no. 3, pp. 251–253, 2005.

- [15] X. Jiang *et al.*, “Wavelength and bandwidth-tunable silicon comb filter based on Sagnac loop mirrors with Mach- Zehnder interferometer couplers,” *Opt. Express*, vol. 24, no. 3, pp. 555–559, 2016.

- [16] V. Donzella, A. Sherwali, J. Flueckiger, S. M. Grist, S. T. Fard, and L. Chrostowski, “Design and fabrication of SOI micro-ring resonators based on sub-wavelength grating waveguides,” *Opt. Express*, vol. 23, no. 4, pp. 9103–9112, 2015.

- [17] P. Prabhathan, V. M. Murukeshan, and Z. Jing, “Compact SOI nanowire refractive index sensor using phase shifted Bragg grating,” *Opt. Express*, vol. 17, no. 17, pp. 1488–1490, 2009.

- [18] V. Donzella, A. Sherwali, J. Flueckiger, S. T. Fard, S. M. Grist, and L. Chrostowski, “Sub-wavelength grating components for integrated optics applications on SOI chips,” *Opt. Express*, vol. 22, no. 17, pp. 21037–21050, 2014.

- [19] Y. Maegami, G. Cong, M. Ohno, M. Okano, and K. Yamada, “Strip-loaded waveguide-based optical phase shifter for high-efficiency silicon optical modulators,” *Photon. Res.*, vol. 4, no. 6, pp. 222–226, 2016.

- [20] D. Mishra and R. K. Sonkar, “Analysis of germanium-doped silicon vertical PN junction optical phase shifter,” *J. Opt. Soc. Am. B*, vol. 36, no. 5, pp. 1348–1354, 2019.

- [21] J. Du *et al.*, “High speed and small footprint silicon micro- ring modulator assembly for space-division-multiplexed 100-Gbps optical interconnection,” *Opt. Express*, vol. 26, no. 11, pp. 13721–13729, 2018.

- [22] B. I. K. D. As, “Performance analysis of metal-microheater integrated silicon waveguide phase-shifters,” *OSA Contin.*, vol. 1, no. 2, pp. 703–714, 2018.

- [23] X. Chen, C. Li, and H. K. Tsang, “Device engineering for silicon photonics,” *NPG Asia Mater.*, vol. 3, no. January, pp. 34–40, 2011.

- [24] J. E. Bowers *et al.*, “Recent Advances in Silicon Photonic Integrated Circuits,” in *Next-Generation*

*Optical Communication: Components, Sub-Systems, and Systems V*, 2016, vol. 9774, pp. 1–18.

[25] M. H. Haron, A. R. Zain, and B. Y. Majlis, “Sensitivity Increment of One Dimensional Photonic Crystal Biosensor,” in *2017 IEEE Regional Symposium on Micro and Nanoelectronics (RSM)*, 2017.

[26] M. H. Haron, D. D. Berhanuddin, S. Shaari, B. Y. Majlis, and A. R. Md Zain, “Sensitivity enhancement of 1-D photonic crystal by waveguide width variation for biosensing application,” in *2018 7th IEEE International Conference on Photonics*, 2018, pp. 7–9. doi: [10.1109/ICP.2018.8533219](https://doi.org/10.1109/ICP.2018.8533219)

[27] A. R. Zain *et al.*, “Ultra high quality factor one dimensional photonic crystal / photonic wire micro-cavities in silicon-on-insulator (SOI),” *Opt. Express*, vol. 16, no. 16, pp. 12084–12089, 2008.

[28] A. R. Md Zain, M. Gnan, H. M. H. Chong, M. Sorel, and R. M. De La Rue, “Tapered photonic crystal microcavities embedded in photonic wire waveguides with large resonance quality-factor and high transmission,” *IEEE Photonics Technol. Lett.*, vol. 20, no. 1, pp. 6–8, 2008.

[29] M. H. Haron, B. Yeop Majlis, and A. R. Md Zain, “Increasing the Quality Factor (Q) of 1D Photonic Crystal Cavity with an End Loop-Mirror,” *Photonics*, vol. 8, no. 99, pp. 1–11, 2021. doi: [10.3390/photonics8040099](https://doi.org/10.3390/photonics8040099)

[30] R. A. Soref and B. R. Bennett, “Electrooptical Effects in Silicon,” *IEEE J. Quantum Electron.*, vol. QE-23, no. 1, pp. 123–129, 1987.

[31] M. H. Haron, D. D. Berhanuddin, B. Y. Majlis, and A. R. Md Zain, “Double-peak one-dimensional photonic crystal cavity in parallel configuration for temperature self-compensation in sensing,” *Appl. Opt.*, vol. 60, no. 6, pp. 13–16, 2021. doi: [10.1364/AO.418646](https://doi.org/10.1364/AO.418646)

[32] M. Nedeljkovic, R. Soref, and G. Z. Mashanovich, “Free-Carrier Electrorefraction and Electroabsorption Modulation Predictions for Silicon Over the 1–14-  $\mu$ m Infrared Wavelength Range.pdf,” *IEEE Photonics J.*, vol. 3, no. 6, pp. 1170–80, 2011.