1. Introduction

In the last decades, power electronics have been used in several applications, such as energy conversion and transmission, electrical traction, and storage systems. In all of these cases, the power converters have a key role, converting the energy of the source into a suitable one for the load, which are based on passive elements and switching devices such as MOSFETs or IGBTs [

1,

2]. For low and medium-voltage applications, MOSFETs and IGBTs are relatively fast and offer the advantage of controlling device turns on and off. However, these switching devices are limited for high power/voltage applications due to their voltage and current maximum value or switching time.

One solution for high power/voltage management is using Multi-Cellular Converters (MCC). The idea of MCCs is to

“divide and rule". These converters consist of an arrangement of several cells connected in parallel, in series, or in cascade, allowing the voltage or current distribution at the input or the output. There are many types of MCCs, such as the Flying Capacitor Multilevel Converter (FCMC) [

3,

4,

5,

6,

7], where the input voltage is distributed among the cell voltages; Cascaded Full Bridge Multilevel Converter (CFBMC) [

8,

9,

10,

11,

12,

13], where the total output voltage is the sum of the output voltage of each Full Bridge (FB); and Multiphase Buck Converter, where its output current is the sum of the leg current [

14,

15,

16]. In all these cases the energy is distributed among the cells, allowing the use of low or medium-power devices for high-power applications. This fact is a great advantage because, normally, low-power devices are faster and more efficient than high-power ones. Therefore, MCCs allow managing high power conversion with low power and fast switching devices. Another feature of the multi-cellular converters is that with suitable frequency modulation techniques [

17,

18,

19,

20] it is possible to obtain a much higher output frequency than the MOSFETs or IGBTs switching frequency.

MCCs offer many advantages, however, there are a lot of challenges to be solved for these topologies. One of them is the ability to balance one variable of the cells according to the application. In FCMC, it is very useful that the capacitor voltages are balanced. Well-balanced capacitor voltages produce the supplied power distributed equally in all the cells. Furthermore, it makes a suitable ripple output voltage [

3,

4,

21]. In the case of Multiphase Buck, balancing the leg current produces an appropriate distribution of the output current of the system [

16]. For the case of CFBMC, it is possible to balance the output voltages of each FB to maintain equalized the power delivered by each FB [

22,

23,

24,

25]. For the same converter, if the sources are batteries, balancing the input current of each FB maintaining well-balanced the charging or discharging of the batteries, making also possible to control their State Of Charge (SOC). All these cell-variables balancing strategies can turn very complicated if the number of cells increases significantly.

Another challenge for Multi-cellular converters is the ability to insert or remove cells during operation [

3,

15,

21,

23], allowing to increase the power of the converter or giving a fault tolerance ability.

There exist many controllers that satisfy all these specifications. In [

3,

21], a control structure is proposed applied for an FCMC, which balances the capacitor voltages, regulates the output current, and allows a cell insertion/removal ability, obtaining interesting results.

The present work applies in the CFBMC the controller proposed in [

3,

21], develops a mathematical approach of the controller used in this topology, and shows the simulation and experimental results.

Section two describes the topology of the CFBMC and models it. The next section presents a description of the decentralized controller. Then in the fourth section, an in-depth analysis of the controller applied to the CFBMC is shown, presenting the closed-loop and open-loop transfer function and analyzing the bandwidth of the system. In section five, the design of the controller is presented, based on the open loop transfer functions of the system, obtaining, theoretically, the eigenvalues of the system. Then, section six presents the simulation and experimental results with three tests: load step, input voltage step, and cell insertion tests. Finally, the conclusion and future works are presented in the seventh section.

2. Description of the system

This article proposes an adaptation of a decentralized control applied previously to FCMC in [

3,

21], now implemented in a CFBMC of

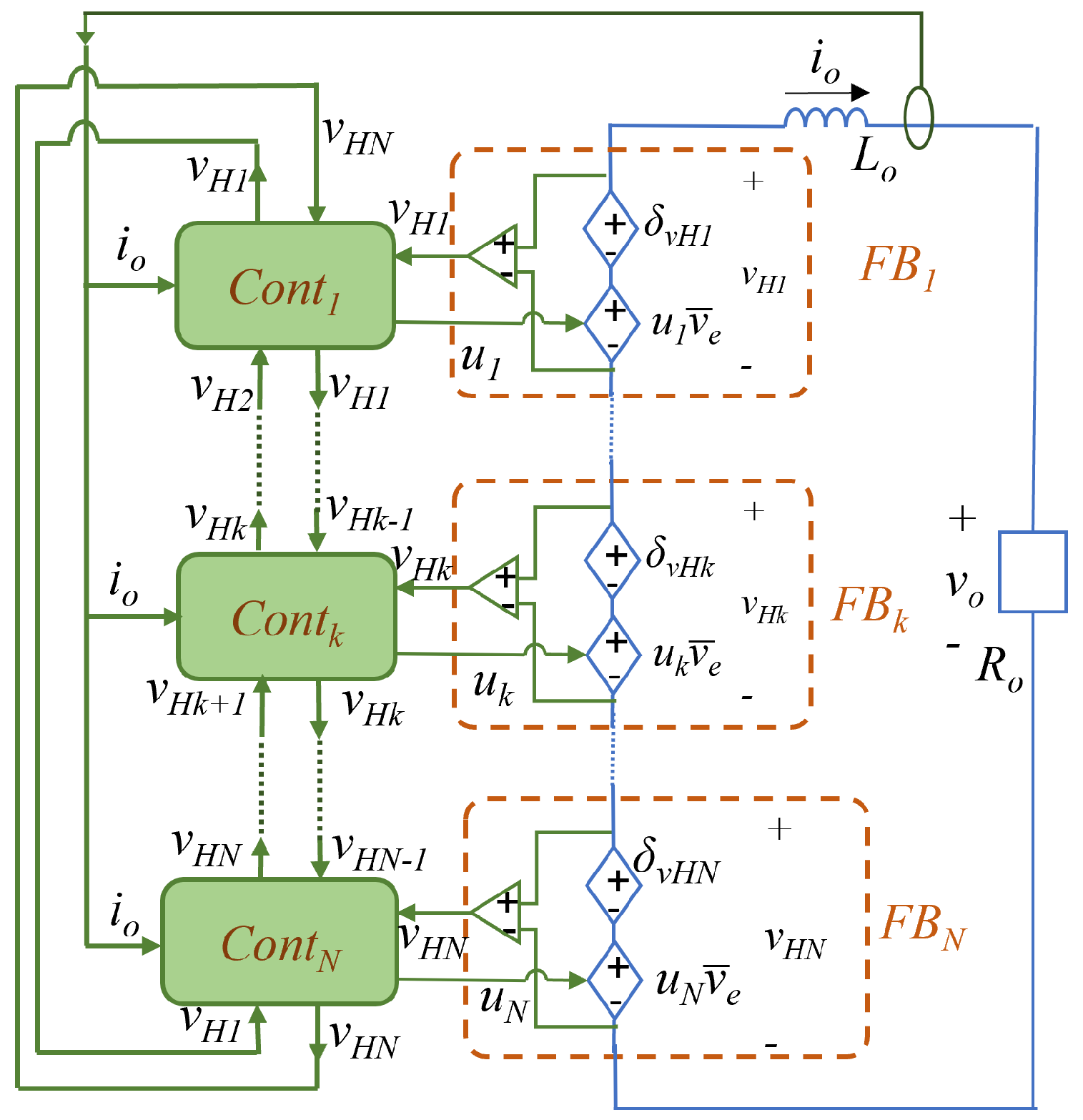

N Full-Bridges with inductive filter and resistive load.

Figure 1 shows the topology of the converter, using MOSFET as the switching device, where the control is implemented, where

, represents the position of the high-side switches, 1, if it is in ON state, and 0 if it is in OFF state, for the

Full-Bridge (FB),

,

for the left side branch of the

Full-Bridge and

for the right side.

is the complementary signal of

.

,

,

,

are: the input voltage, the switching output voltage, the switching FB cell input capacitor voltage and the switching FB cell input inductance current of the

FB, respectively, while

and

correspond to the output current and voltage of the inverter, respectively. Depending on the position of the switches, the value of

varies and also the internal cell signals. In order to simplify the equations, a slow variation assumption is made, compared to the switching frequency and an average model can be proposed, where the variable

x is the moving average of the

, and

x can be:

,

,

,

. In this work, the goal is to balance the moving average of the output voltage of the Full-Bridges,

, called the Cell Voltage (CV) and to regulate the output current,

, which is the Global Variable (GV) and to provide a means of easily inserting or removing an FB cell without adding complexity to the balancing control system.

Taking into account that the switching current through the output of each Full-Bridge is

, and the average is

for all the FB cells, balancing their output voltage is equivalent to balance the power delivered by each cell. According to

Figure 1, the dynamic equation of the moving average variable is:

where

,

is the duty cycle of

,

is the series resistance of the inductance

L, and

corresponds to

,

is the drain-source-ON resistance of the MOSFET and

is the series resistance of

. The dynamical model of the output voltage of the Full-Bridge,

is:

According to (1) and (2) the equivalent circuit of the converter is shown in

Figure 2:

Knowing that in the CFBMC all the input voltages have the same nominal value,

. Hence, according to [

12,

26], it is possible to simplify the model, considering the oscillation produced by the input filter and the variations in the input voltage as a disturbance. Therefore:

Based on (1c) and (

3), the converter follows the presented model:

where

.

Based on (4),

Figure 3 presents the equivalent linear circuit:

Equation (4) represents the linear model of the inverter. Hence, it is possible to express it in Laplace domain:

Then, expressing it as a matrix form:

where

,

,

, .

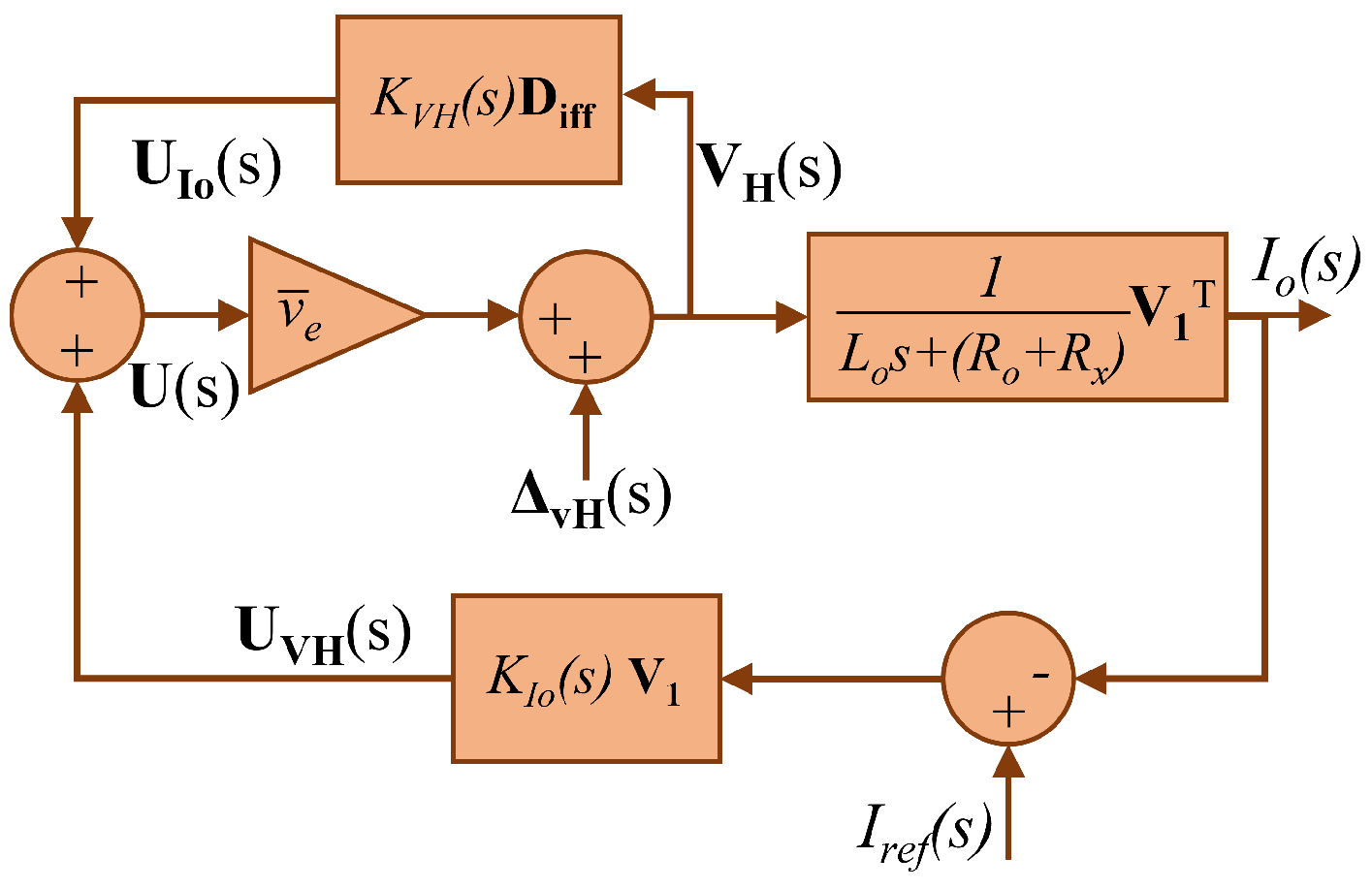

Figure 4 shows the block diagram of (6). Thanks to this model, a decentralized controller used to balance the output voltage of the cells

is proposed in the next chapter.

3. Description of the decentralized controller

The proposed control loop for this article is based on the controller found in [

3,

21] that is applied to a FCMC, which shows interesting results. Furthermore, [

23] shows a simulation of this controller applied in a grid-tied cascaded multilevel inverter. The presented paper implements the controller to an isolated Cascaded FB Multilevel Inverter, connected to a resistive load with an inductive filter.

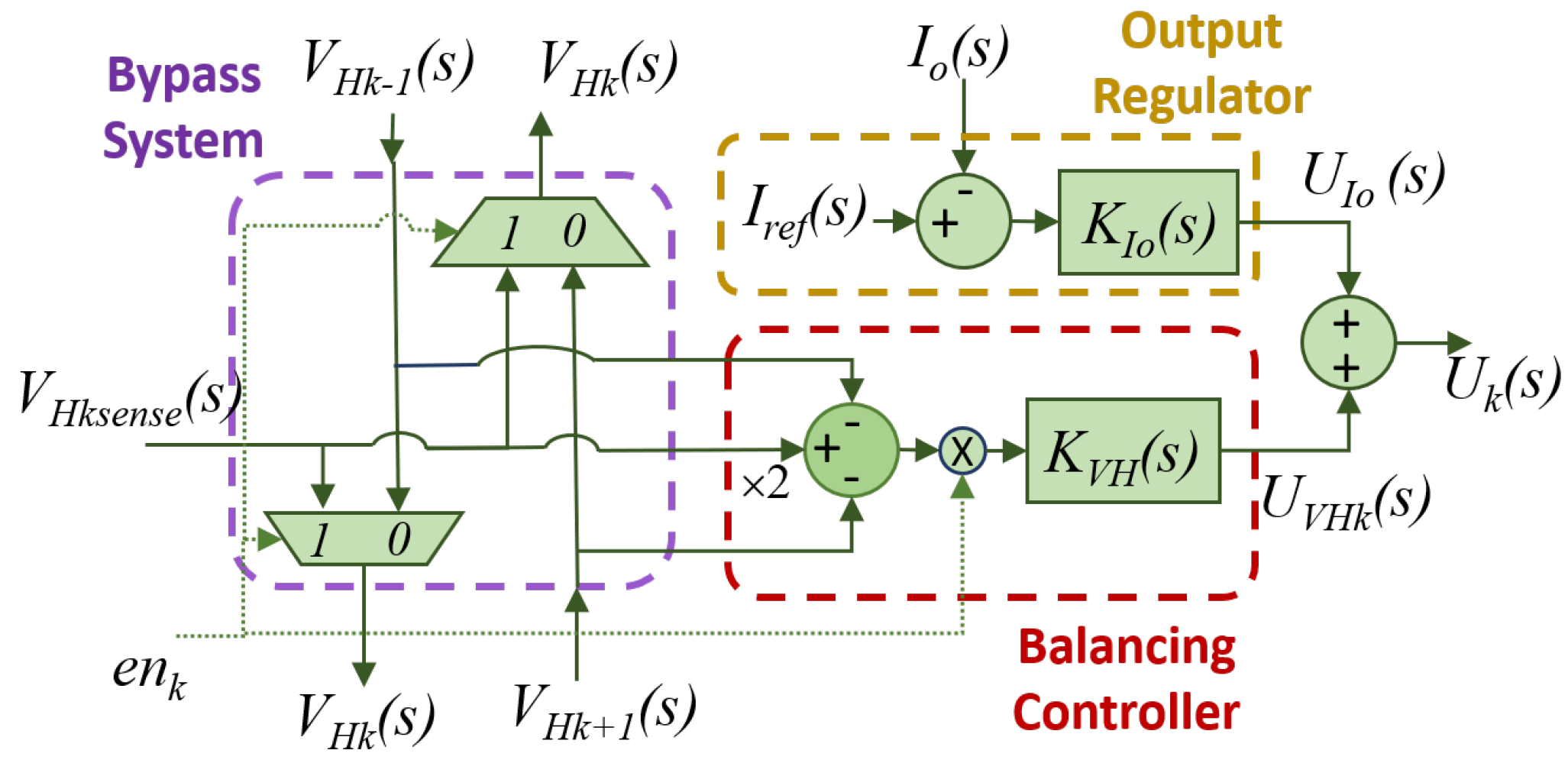

Figure 5 shows the proposed control structure.

As

Figure 5 shows, the control structure presents three stages: the Bypass system, the Balancing controller and the Output Current regulator.

3.1. The Bypass System

The main goal of this block is to manage the communication between the cells depending on its state (active or inactive, ON or OFF). According to

Figure 5, the cell controller receives an enable signal used to turn OFF or ON the FB cell. When the

FB cell is ON, the bypass system sends

to

, which is the signal that is sent to the cell

and

, respectively. When the

cell is OFF, the FB is skipped and the value of

is not sent anymore. Instead of that, the cells

and

receive the values of

and

, respectively. This part of the controller allows the insertion or removal of FB cells during operation. However, if a balancing controller is not implemented, each FB cell can supply different power, voltage, or current that could not be the desired one.

3.2. The Output Current Regulator

This part of the controller regulates the output current supplied to the load. It is a typical linear controller,

, that can be a PI or other regulator, based on the transfer function of the plant. According to

Figure 5, the output of the output regulator is defined as:

3.3. The Cell Power Balancing Controller

This stage of the control structure is the cell power balancing controller. It compares the values of its output voltage

with the average value of the output voltages of the neighboring actives FB cells,

and

. The error obtained is then canceled by a linear controller,

, that can be a PI or another type of compensator.

According to (

7), (

8) and

Figure 5, the output of the entire controller is defined as:

The control method illustrated in

Figure 5 is applied to each FB cell. Then the cells are connected together in a closed-loop chain of communications to exchange with their close neighbors the values of their output voltage, as shows

Figure 6.

Notice that the cell communicates with the 1st and cells, and the 1st cells are compared with the cell 2nd and , closing the chain of the system.

Expressing (9b) as a matrix form, it follows:

where

4. Closed-Loop System Analysis

This section shows the mathematical study of the closed-loop system using the proposed controller. The analysis of the transfer functions which comprise the output current regulator and the local balancing controller makes it possible to determine the nature and the parameters of the controllers used. Their design is discussed in the next chapter. The block diagram of the system, and the model of the converter with the controllers is shown in

Figure 7.

Thanks to

Figure 7, one can determine the open-loop transfer function and the closed-loop transfer function of the output regulator and the ones of the balancing controller.

4.1. Output Current Regulator Analysis

To design the output regulator it is necessary to perform an analyzes the output regulator loop. Hence, inserting the decentralized controller, proposed in (

10), into the model of the output current control loop of the inverter, and taking into account that

and

, (

6a) one obtains:

where

and

is the open-loop transfer function of the output current regulator.

Notice that the term related to the balancing control stage is removed in the transfer function because

represents the Laplacian of a graph. Indeed, according to [

3,

21,

23], the sum of the elements of the rows and the sum of the elements of the columns is zero. Because this matrix is post multiplied by

, the results are zero. Based on

, the design of

is provided in the next section.

In order to get a better understanding of the balancing control loop, it is necessary to analyze the closed-loop transfer function of the output regulator,

, which is defined below.

It shows that the resulting regulated output current is provided by the separate contribution of the current loop and a disturbance transfer function, , generated by the oscillations of the input voltage capacitors and the duty cycles of each cell FB.

For the next subsection it should be considered if the output regulator is well designed, when is a step, at , means that with , , producing that when .

4.2. Cell Power Balancing Control loop analysis

Now, the balancing control loop has to be analyzed Inserting (

10) in (6b), it follows:

Inserting (

12) in (

13), one obtains

Simplifying:

where

is the excitation signal. The controller

is defined based on the desired bandwidth of

, which is directly linked to the eigenvalues of the matrix

, then it is described in the next section.

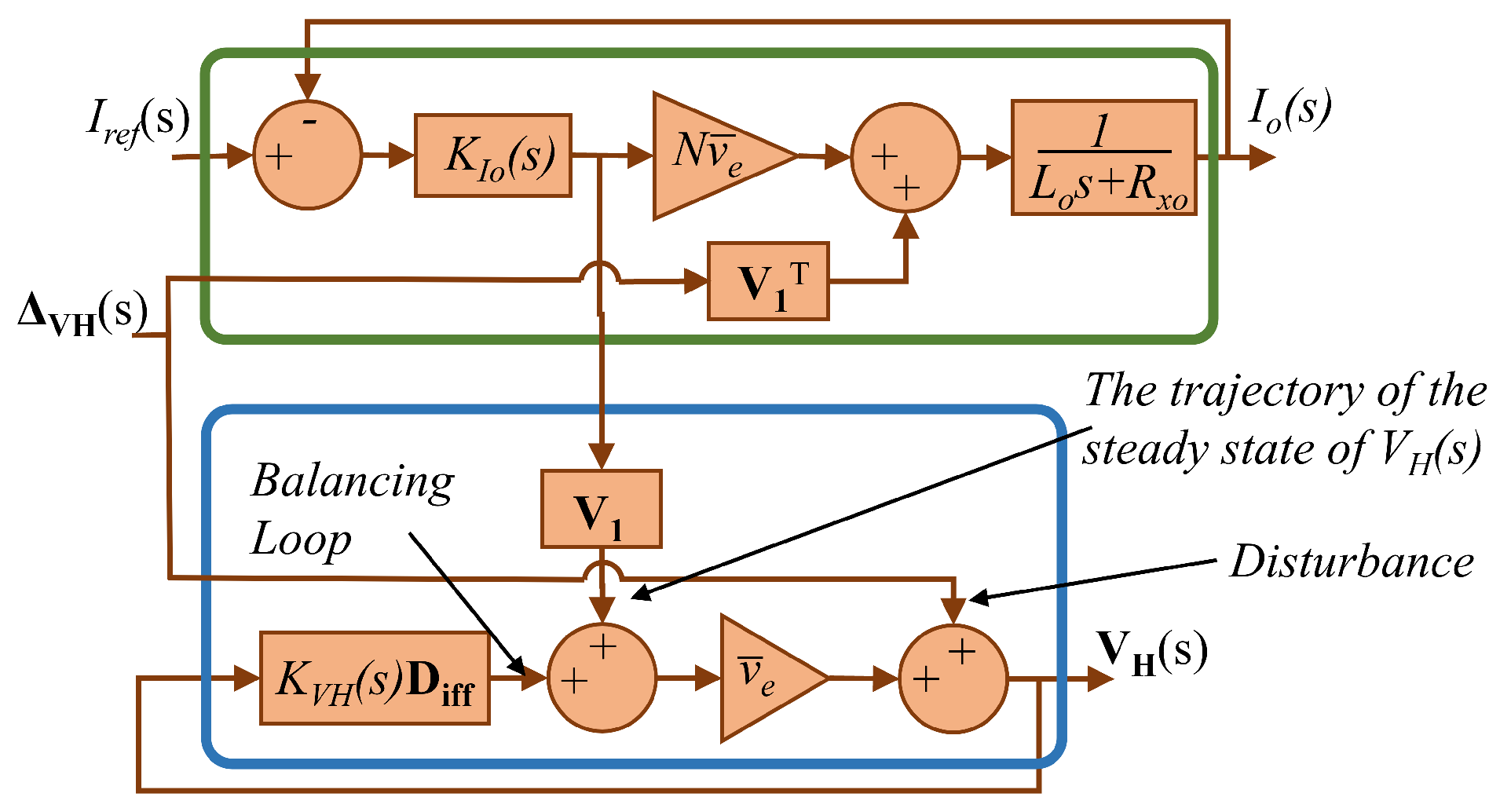

4.3. Global closed-loop analysis

According to (

11), and (

13),

Figure 8 shows the simplified closed-loop block diagram.

Notice that

depends on three inputs, one corresponds to the balancing controller, other depends on the disturbance,

, and the last one depends on the output current loop, which affects all the cell voltages at the same time. Analyzing in steady state, according to (

15), when

, if the controller is well designed,

, producing that the trajectory in steady states for

is

.

5. Design of the controllers

Now, both controllers have to be designed, taking into account some criteria, such as bandwidth of the loops and the correlation of Bode analysis between the two loops.

5.1. Design of the Output Current Regulator

Based on

, for a stable and low bandwidth system, an integral corrector can be proposed for

, and the chosen controller type for the output current regulator is an Integral (I) controller, hence:

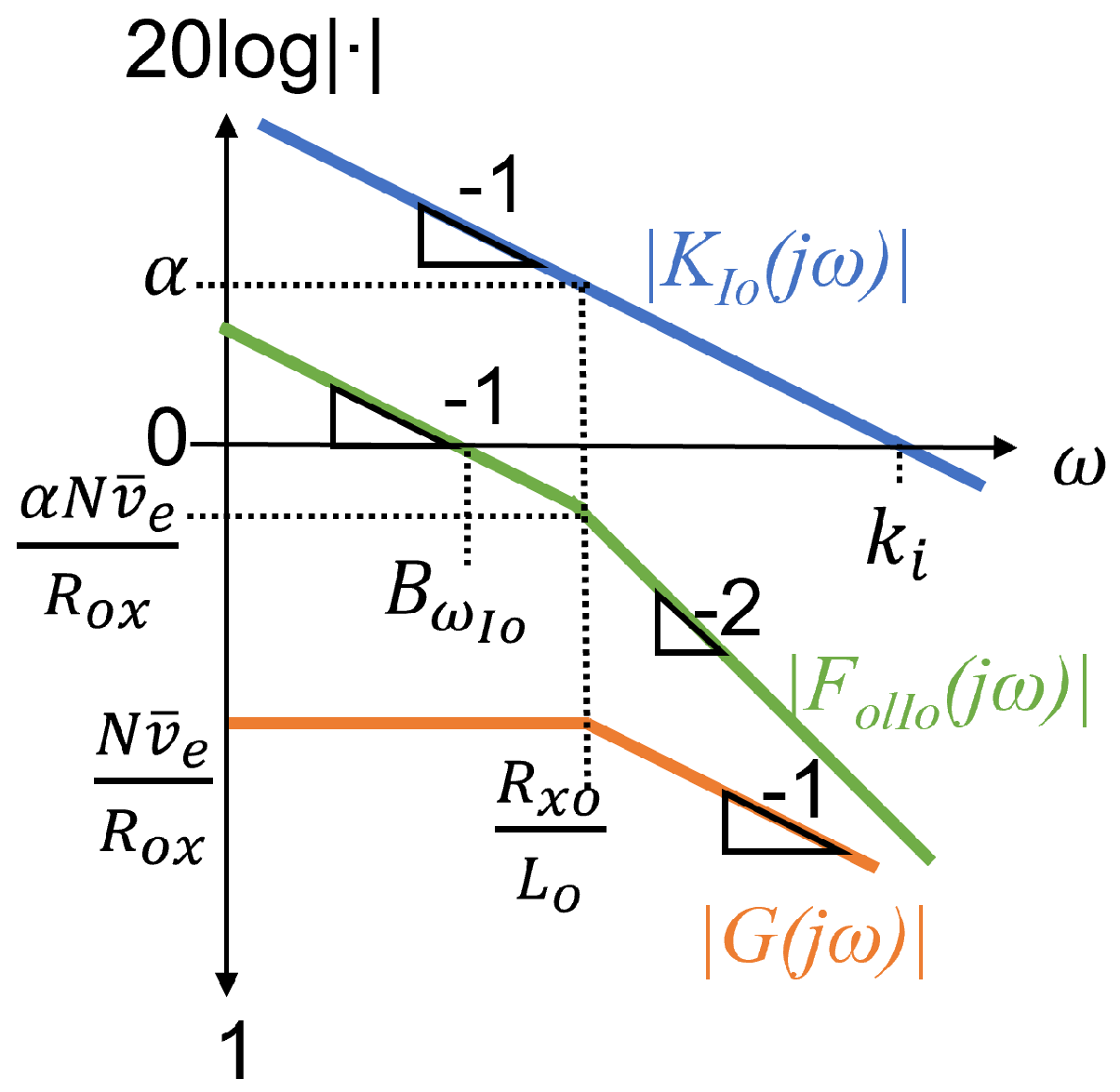

The Bode analysis of

,

and

are shown in

Figure 9:

According to

Figure 9, it follows:

where

is the bandwidth of the output regulator, which is fixed ten time less than the switching frequency of the MOSFETs,

.

5.2. Design of the cell power balancing controllers

The balancing controller is designed based on the

expression. According to (

15),

. Then, decomposing

in its modal and diagonal matrix,

follows to:

where

and

are the Diagonal and Modal matrix of

, respectively. It should be noted that one eigenvalue of

is equal to 0, because it is a Laplacian of a graph.

represents the transfer function of the modal response, defined as:

where

.

Hence the open-loop transfer function of the

mode is:

It should be mentioned that

corresponds to a circulant matrix

, which is described as:

Since

is a circulant matrix, it is possible to obtain an expression of its eigenvalues. According to [

27] the eigenvalues of a circulant matrix are:

where

.

It can be observed that for the case of the

, the coefficients,

s, are:

Therefore, according to (

23) and (

24), the eigenvalues of

are defined as:

Notice that the first eigenvalue, , is equal to 0, validating that it also represents the Laplacian of a graph. Furthermore, because of the symmetric property of the cosine, the eigenvalue is equal to the eigenvalue. Finally, the highest eigenvalue is obtained for when N is even, and when N is odd. The maximum case is produced when N is even, generating a . For odd values of N the highest eigenvalue tends to be 4 when N increases. The design of the balancing controller is based on the possible maximum eigenvalue, , and the minimum eigenvalue, , which values are 4 and 0, respectively.

means the system presents a pure integrator that theoretically is stable. However, because of numeric approximations in the implementation, the system may be unstable after a long lapse. For that reason, the selected controller corresponds to a low-pass filter that ensures the stability of the system, with a pole located at a very low frequency. Hence, the proposed controller is:

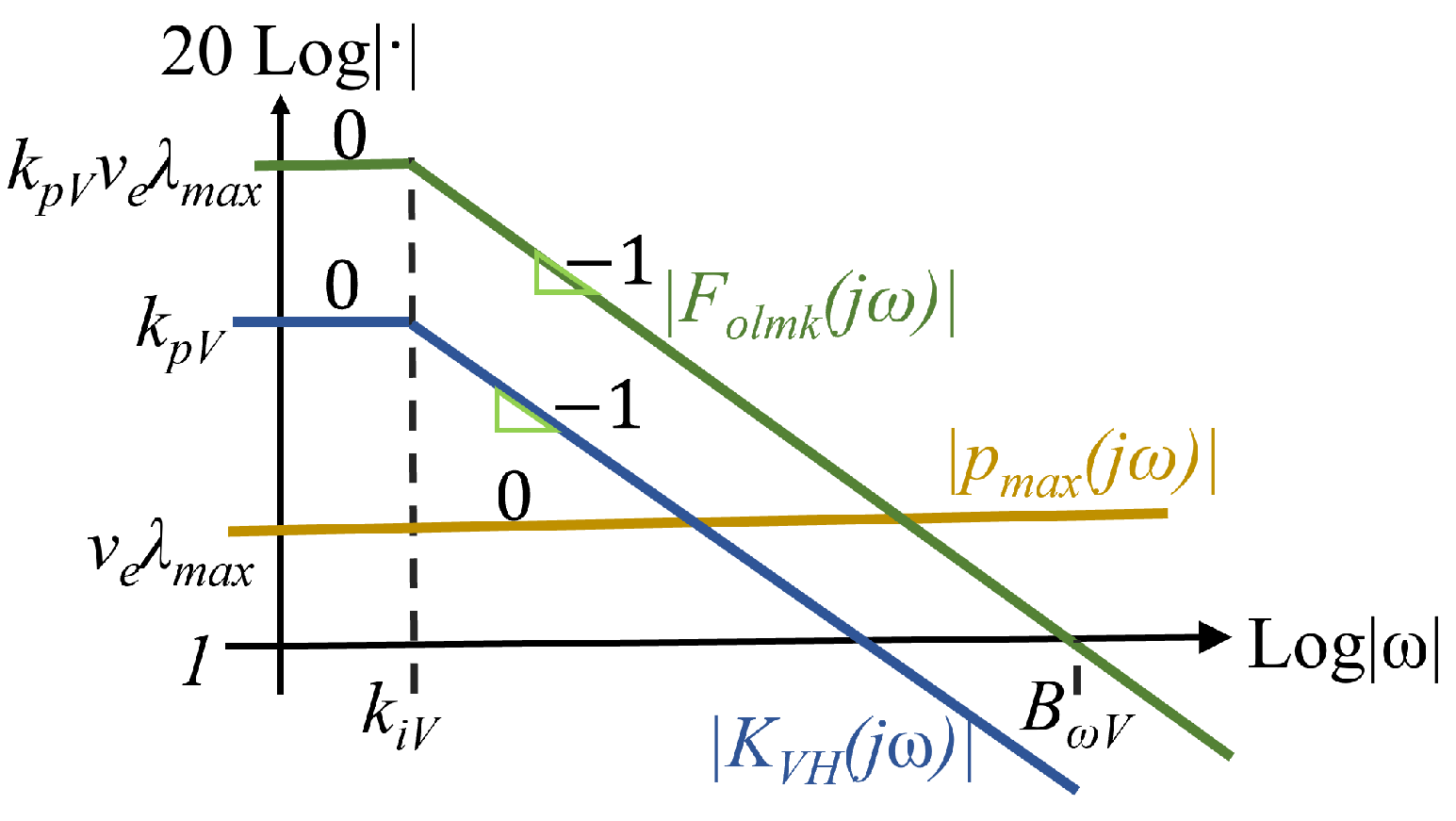

In order to determine the parameters of the controller,

Figure 10 shows the Bode diagram of

,

,

.

Based on the Bode diagram of

Figure 10, the bandwidth

is set using the

parameter:

The bandwidth, , must be ten times less than the switching frequency . Due to that, the converter can work either as an inverter, or as a DC/DC converter, the pole is selected ten times less than the operating frequency of the inverter.

6. Results

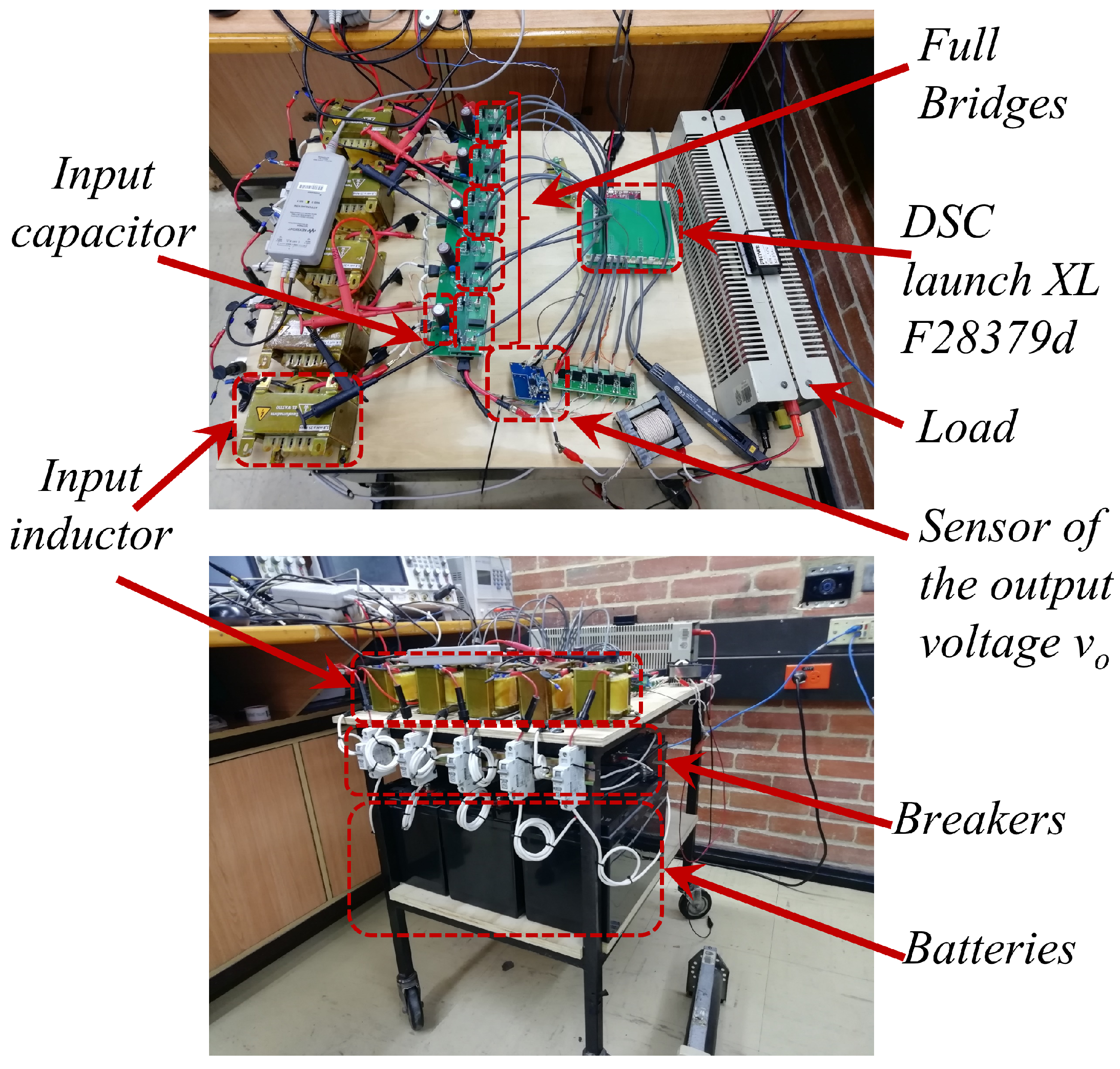

A prototype implements the proposed decentralized controller is now considered. It has been carried out in the laboratory for measurement purpose. The controllers are implemented in a Cascaded Multilevel Inverter of 5 FBs, as shown in

Figure 11.

Both simulation and experimental results, developed hereafter, are obtained with the converter working as a DC/AC converter, with three different tests: an input voltage step, a load step and a cell insertion during operation. Furthermore, a modal response simulation is also presented. The parameters of the controllers are shown in

Table 1:

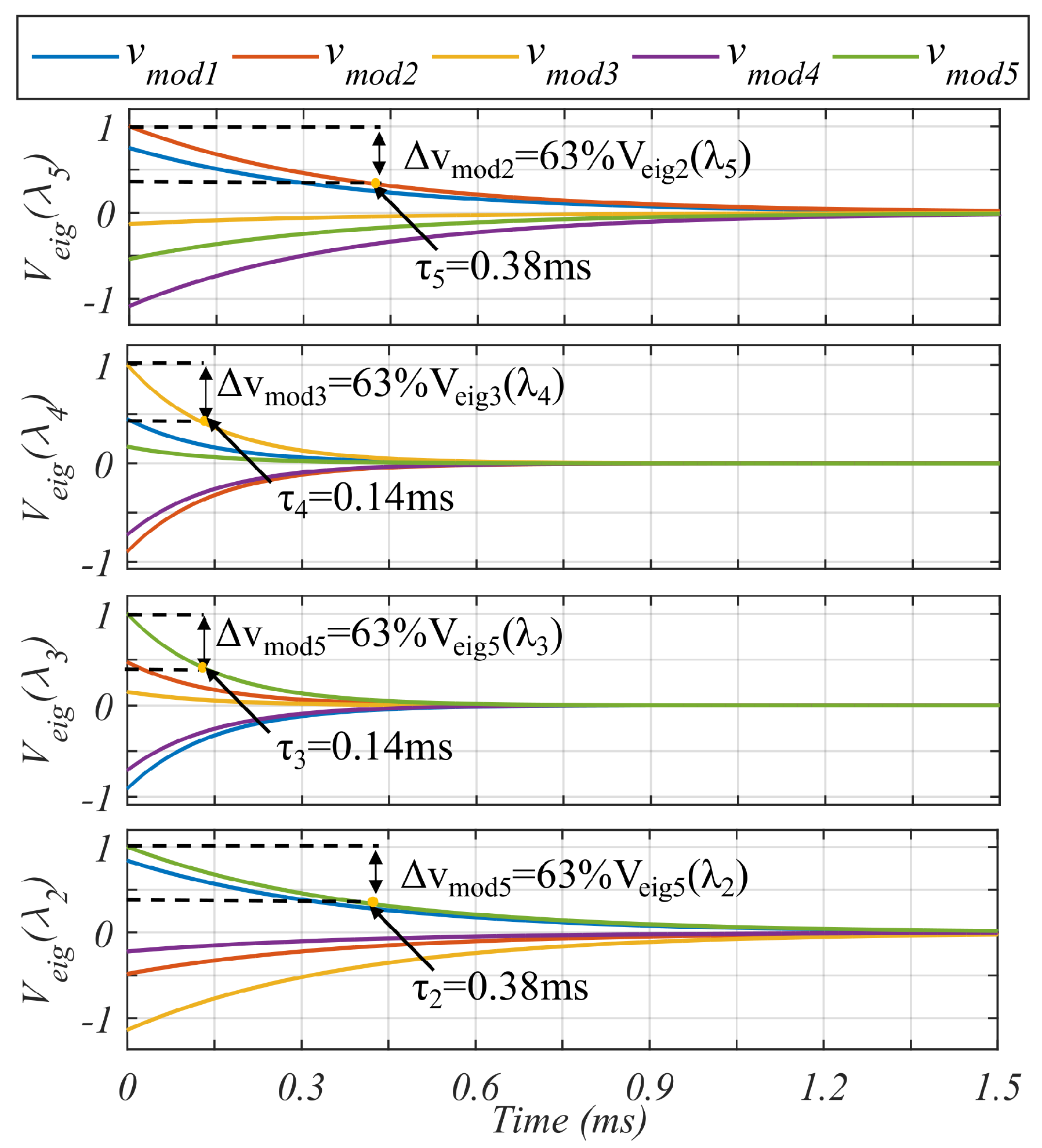

6.1. Modal Response Simulation

This simulation corresponds to the modal respond of the transfer function of the balancing loop. For

,

corresponds to:

Appendix 1 shows the demonstration of these values, which their numeric values are:

while the modal matrix,

, is:

Using the eigenvectors as the initial conditions,

Figure 12 shows the modal respond of the system.

It is clearly observed that the system is stable and the time response of the modes are very different. Depending on the parameter

of the decentralized controller, this time response can be adjusted.

Table 2 shows a comparison between the theoretical time constants and the ones obtained by simulation.

Notice that given that there are two pairs of similar eigenvalues, there are also two pairs of time constants, meaning that there are two double poles at these time constants. Furthermore, it can be observed that simulated and theoretical values are very similar, validating the performance of the controller.

6.2. Full System Simulation Results

The first simulation test corresponds to a load transient from 95

to 70

.

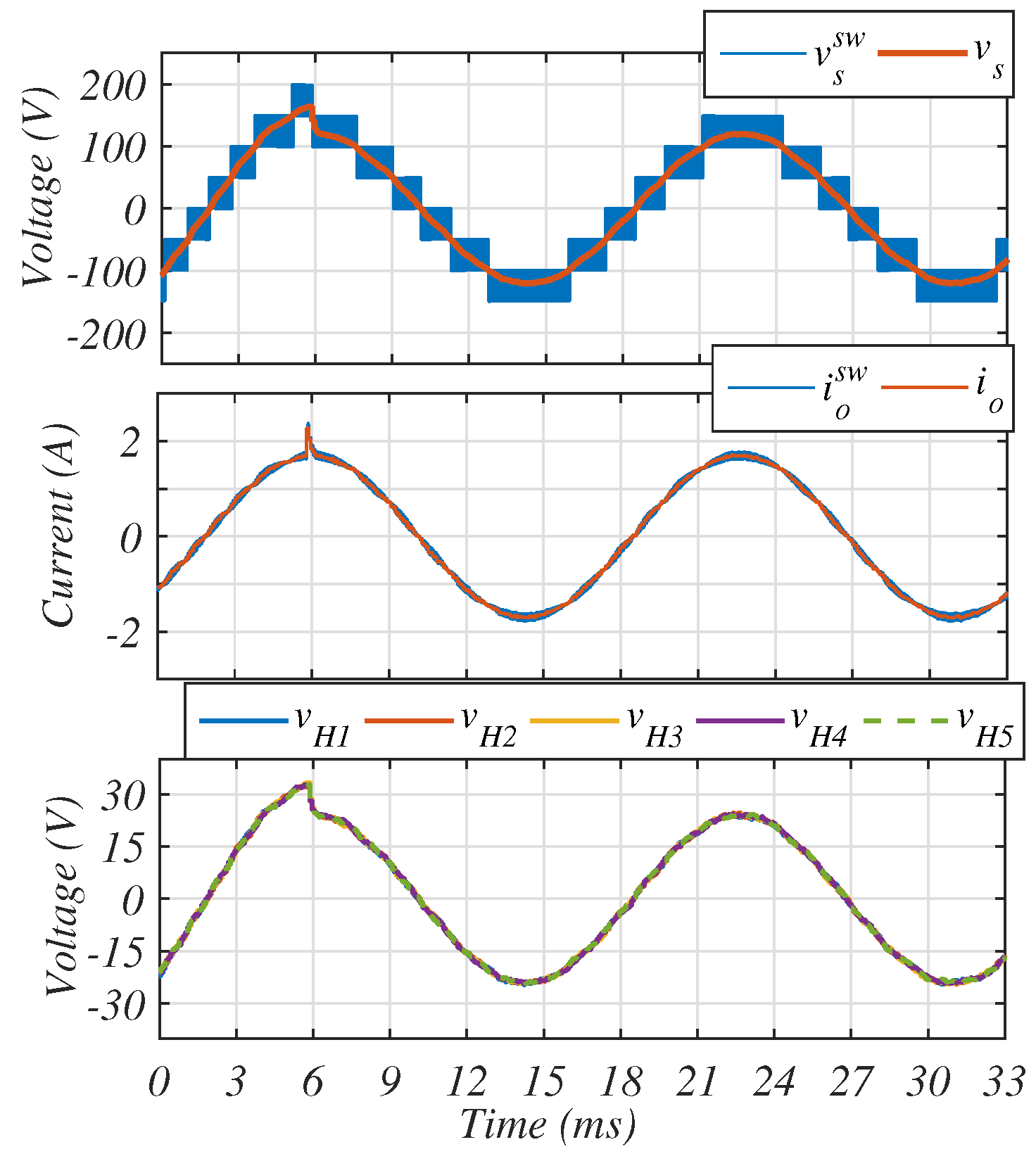

Figure 13 shows

and

when the converter works as a DC/AC converter.

It is observed that before the disturbance occurs, the multilevel converter uses 9 voltage levels. After the disturbance, only 7 levels are required to regulate the output current. Notice also that the CVs are balanced during all the simulation, before and after the disturbance, validating for DC/AC conversion that when a disturbance in the output current occurs, the CVs are not unbalanced, only their common average value are affected. Furthermore, the current is stabilized during a small transient, less than 1 ms.

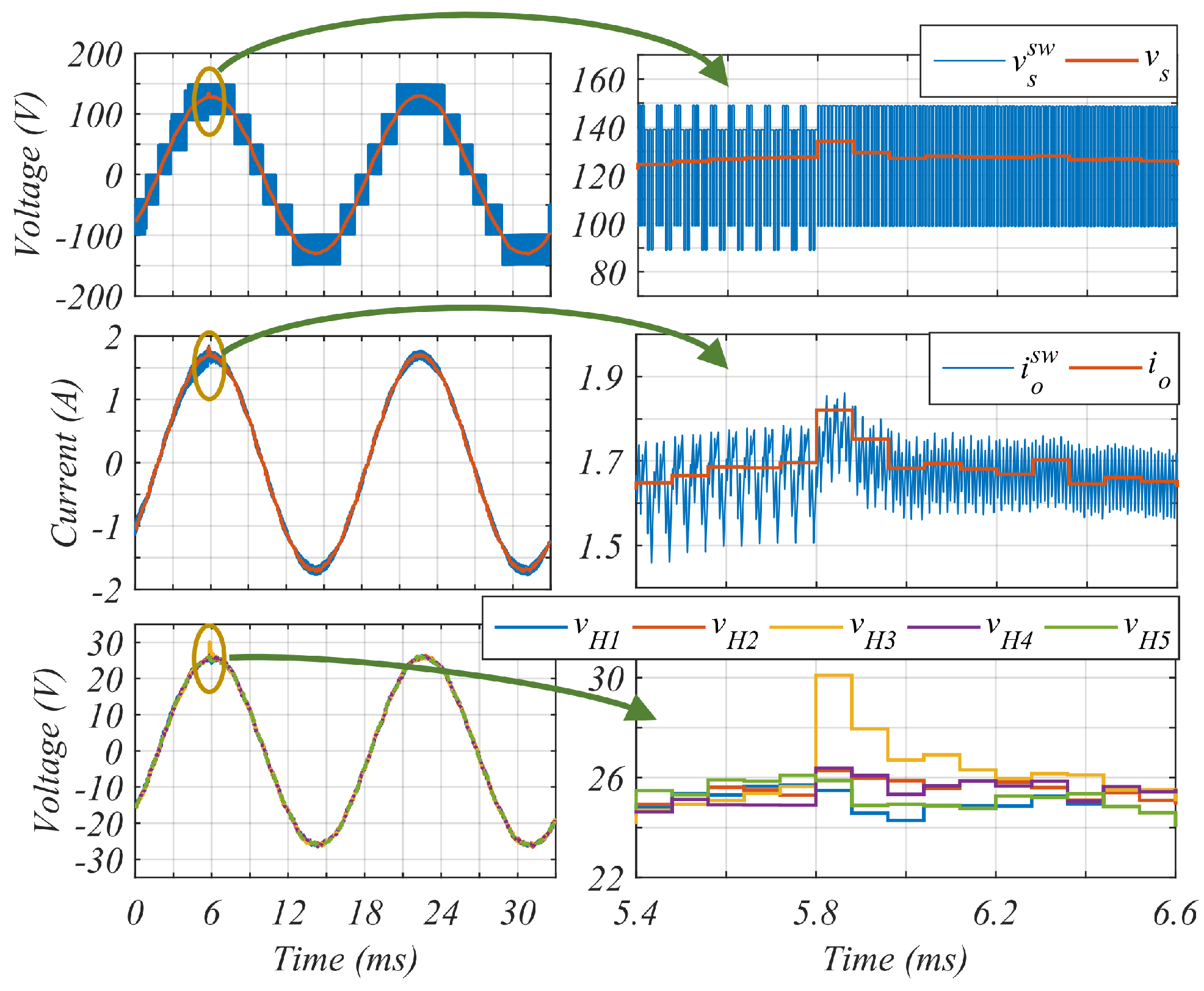

The next simulation result, shown in

Figure 14, corresponds to an input cell voltage disturbance, i.e. a step voltage from 40 to 50V for the inverter with a resistive load of 77

.

It should be noted that the voltage disturbance almost affects neither the output current

nor the output voltage

, while the CVs are automatically balanced thanks to the decentralized controllers in only 0.5 ms.

Figure 14 also shows that, by nature of the inverter, when one of the input voltages is 40 V, there exists an asymmetric ripple in

and

and when the input voltage is 50 V, the ripples are equalized. However, in both cases the average output current

and the

s are well regulated and balanced, respectively.

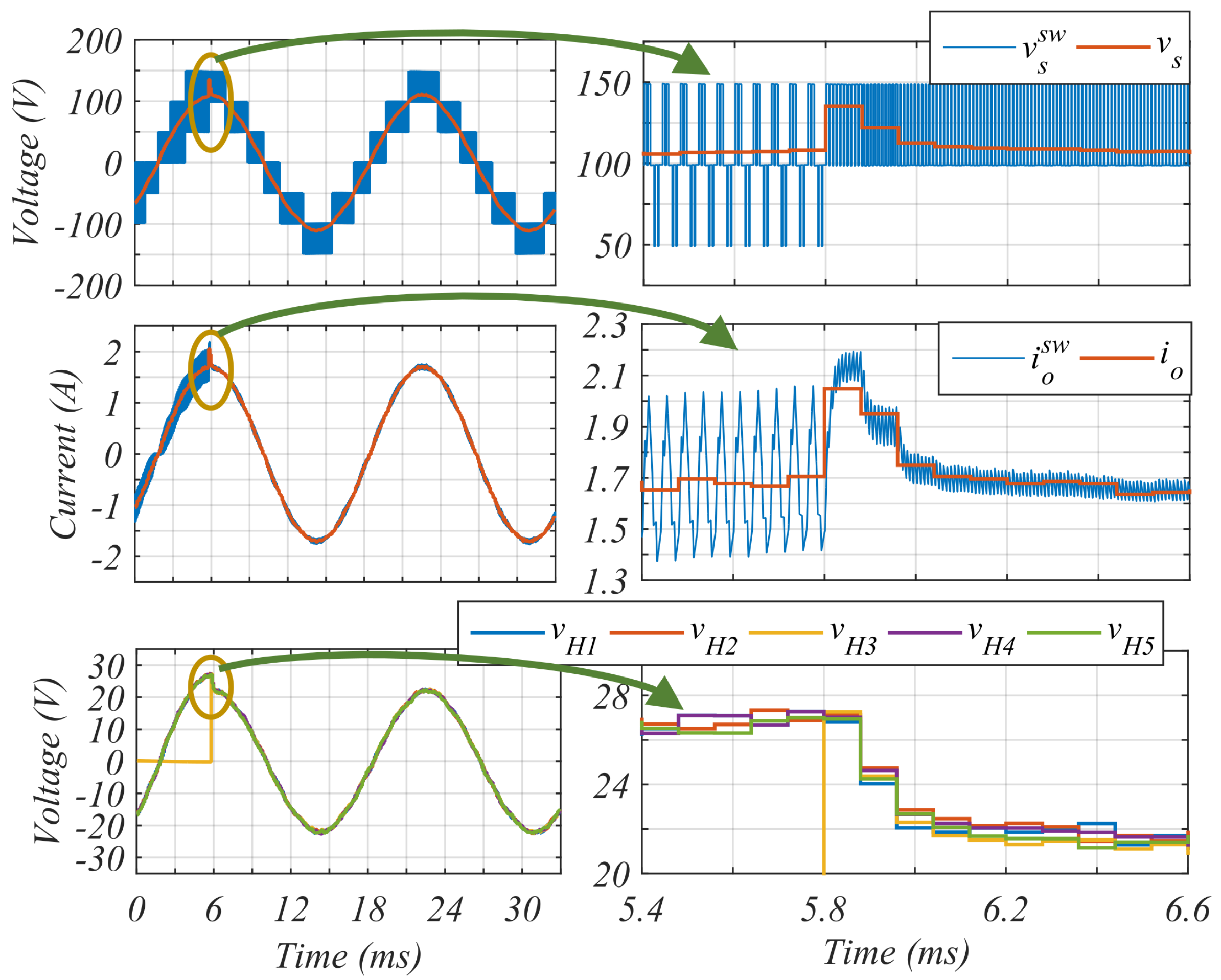

The next simulation corresponds to a cell insertion during operation, going from 4 FBs to 5 FBs, when the converter operates as an inverter.

Figure 15 shows the results obtained for the

s,

and

signals.

It should be noticed that before the cell insertion, and present both a high ripple, due to a constant control signal interleaving set for 5 cells, i.e. signal phase. Even if the ripple is high, the average value of the output current is regulated when only 4 cells are activated. When the fifth FB cell is inserted, presents an overshoot and then it is stabilized in less than 0.25 ms. s voltages are balanced when there are 4 FBs and then, when the 5th cell is inserted, there are auto balanced, reaching a new operation point in 0.25 ms approximately.

This test validates by simulation the three functions of the controller, the balancing of the CV, the regulation of the GV, and the bypass system activation. It can be inferred that all the simulation results are in concordance with the previous theoretical study, producing the expected behavior in terms of reconfigurability, bandwidth and stability for this multilevel converter topology.

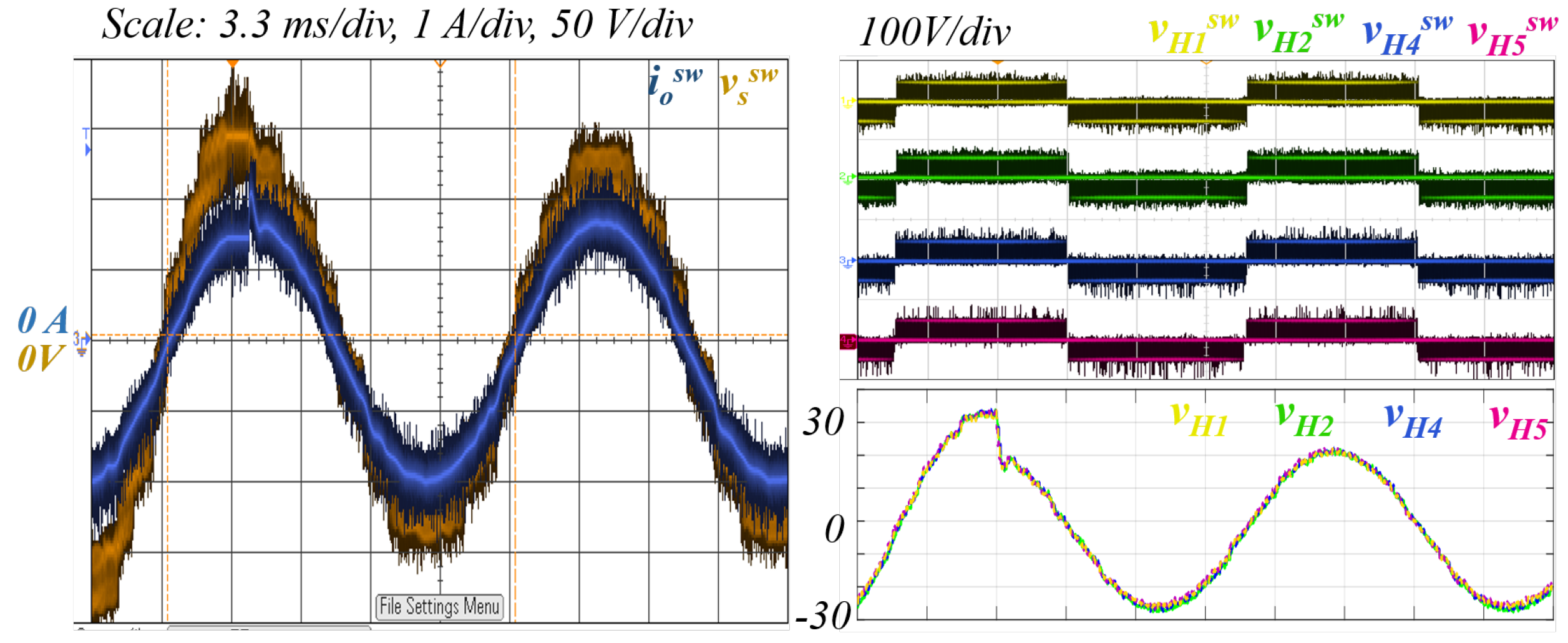

6.3. Experimental Results

The experimental results are developed with a prototype composed of a CFBMC of 5 FB, fed by Li-ion Batteries of 48 V, with the parameters described in

Table 1. More details related to the construction of the inverter is presented in [

28].

In order to compare the simulation and experimental results, the tests developed here are the same than the ones illustrated in the previous simulations.

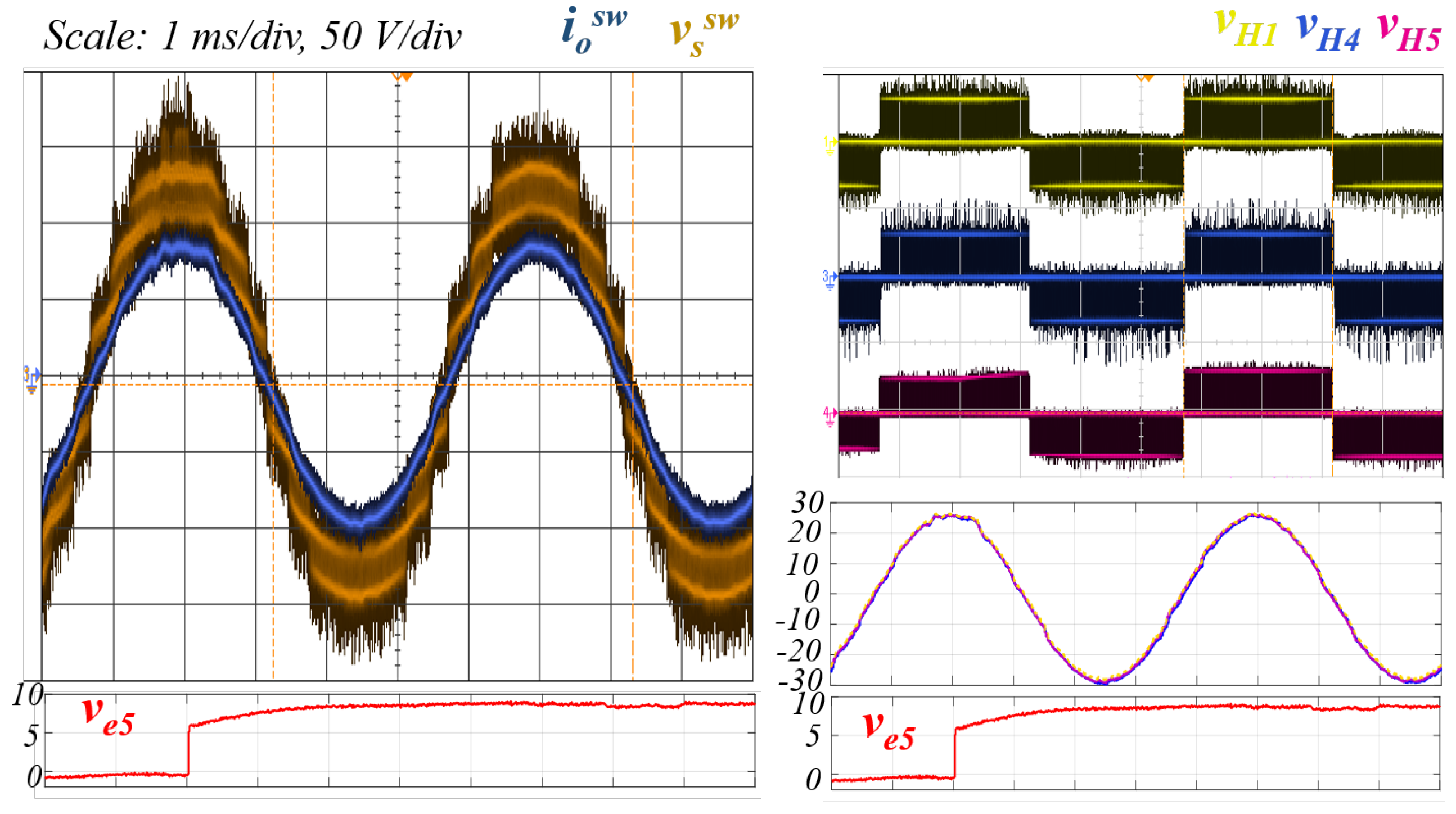

Figure 16 shows the experimental results of first test, corresponding to a load step (or load transient). It can be seen that there exists a concordance with the simulation result of this test, presenting similar overshoot in the current and similar settling time. Moreover, the switching levels of

are the same. Furthermore, as happened in the simulation, the operating points of

s change in 0.5 ms without any unbalance between them.

The next result corresponds to the disturbance in one input voltage FB cell.

Figure 17 shows the behavior of the output current

, the output voltage

, the switching output voltage of each FB 1, 4 and 5,

,

, and their respectively moving average,

s.

It should be noted that the step voltage is almost not detected in s. This is because the input filters presented in the converter smooth the effect of the voltage disturbance. Furthermore, it can be observed that during all the experiments s voltage are well balanced. This observation also validates the balancing controller, maintaining the same output voltage of each FB cell even when the input voltages change. Additionally, the output current is well regulated.

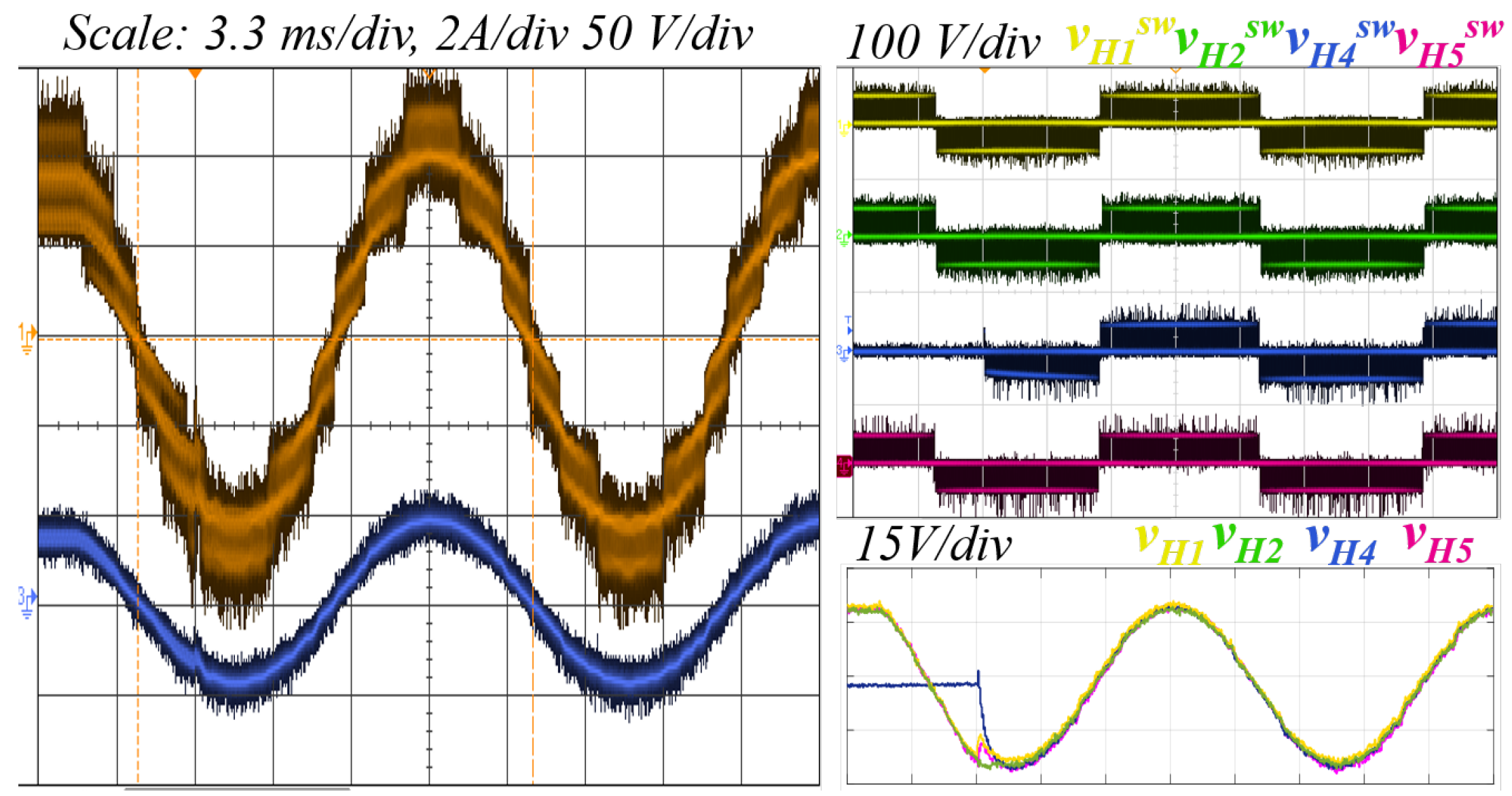

The next result, presented in

Figure 18, corresponds to a FB cell insertion during operation, starting with 4 FB cell and inserting the 5

th FB cell. It is important to note that the current follows the reference during all the experiments, presenting a small transient when the FB cell is inserted. Furthermore, it can be observed that the CVs are well balanced after the insertion, reaching a new operating point with a settling time of 0.6 ms, approximately. These values are in concordance with the predicted time constants of the system and show a strong similarity with the simulation results. This test validates the three stages of the controller, the balancing controller, the GV regulator, and the bypass system.

It can be inferred that all the experimental tests are in concordance with the simulation tests and the theoretical studies developed in this paper, demonstrating the good performance of the controller for this topology.

7. Conclusion

A decentralized control principle for the balancing of the power delivered by the FB cell of a multilevel converter has been shown in this paper.

The decentralized control is composed of several controllers, each associated with a cell of the inverter, which adjust their local control signal by comparing their sensed cell voltage with those of the closest neighbors.

This control method can handle a huge number of cells and makes it possible to obtain a robust system for the case of load transient and cell battery voltages variations.

Moreover, it allows to manage the number of active cells and to carry out reconfiguration during operation. These reconfiguration capability can be useful in case of a cell failure and address functional safety concerns.

Tests of a laboratory prototype help to demonstrate the robustness of the proposed method.

Two future works are in mind with this control method. The first one is the implementation of this controller for balancing the state of charge of the batteries that are the input sources of a CFBMC, and the second future work is the implementation of this control method in a multi-phase buck converter.

8. Appendix

Appendix 8.1. Appendice 1: Demonstration of the eigenvalues

For

, the eigenvalues are:

Using trigonometric identities, follows to:

assigning

, and using trigonometric identities follows:

Hence, obtaining

all the eigenvalues are found. Taking into account that

,

, hence:

Using the double and half angle formulas and taking into account that follows:

References

- Mohan, N.; Undeland, T.; Robbins, W.P. Power Electronics: Converters, Applications and Design. 1989.

- Rashid, M.H. Power electronics: devices, circuits and applications; Pearson, 2014. [Google Scholar]

- Vivert, M.; Cousineau, M.; Ladoux, P.; Fabre, J. Decentralized Controller for the Cell-Voltage Balancing of a Multilevel Flying Cap Converter. In Proceedings of the PCIM Europe 2019; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management; 2019; pp. 1–8. [Google Scholar]

- Fabre, J.; Ladoux, P.; Solano, E.; Gateau, G.; Blaquière, J. Full SiC multilevel chopper for three-wire supply systems in DC electric railways. In Proceedings of the 2016 International Conference on Electrical Systems for Aircraft, Railway, 2016, Ship Propulsion and Road Vehicles International Transportation Electrification Conference (ESARS-ITEC); pp. 1–7. [CrossRef]

- Fabre, J.; Ladoux, P.; Solano, E.; Gateau, G.; Blaquière, J. MVDC Three-Wire Supply Systems for Electric Railways: Design and Test of a Full SiC Multilevel Chopper. IEEE Transactions on Industry Applications 2017, 53, 5820–5830. [Google Scholar] [CrossRef]

- Meynard, T.A.; Foch, H. Multi-level conversion: high voltage choppers and voltage-source inverters. In Proceedings of the PESC ’92 Record. 23rd Annual IEEE Power Electronics Specialists Conference; 1992; pp. 397–403. [Google Scholar] [CrossRef]

- Meynard, T.A.; Fadel, M.; Aouda, N. Modeling of multilevel converters. IEEE Transactions on Industrial Electronics 1997, 44, 356–364. [Google Scholar] [CrossRef]

- Negash, M.F.; Manthati, U.B. Development of 7-level cascaded H-bridge inverter topology for PV applications. In Proceedings of the International Conference on Electrical, Electronics, and Optimization Techniques, ICEEOT 2016; IEEE: Chennai, Tamil Nadu, India, 2016; pp. 1847–1852. [Google Scholar] [CrossRef]

- Vivert, M.; Diez, R.; Cousineau, M.; Bernal Cobaleda, D.; Patino, D.; Ladoux, P. Real-Time Adaptive Selective Harmonic Elimination for Cascaded Full-Bridge Multilevel Inverter. Energies 2022, 15. [Google Scholar] [CrossRef]

- Luo, F.L.; Ye, H. Multilevel DC/AC Inverters. In Advanced DC/AC Inverters: Aplications in Renewable Energy; chapter 8; CRC Press: Boca Raton, FL, 2013; pp. 137–154. [Google Scholar]

- Luo, F.L.; Ye, H. Trinary Hybrid Multilevel Inverters. In Advanced DC/AC Inverters: Aplications in Renewable Energy; chapter 9; CRC Press: Boca Raton, FL, 2013; pp. 155–205. [Google Scholar]

- Vivert, M.; Patino, D.; Diez, R. Modulation Strategy and Controller for Grid-Tied Trinary Hybrid Multilevel Inverter. IEEE Journal of Emerging and Selected Topics in Power Electronics. [CrossRef]

- Liu Yu, F.L. Trinary hybrid 81-level multilevel inverter for motor drive with zero common-mode voltage. IEEE Transactions on Industrial Electronics 2008, 55, 1014–1021. [Google Scholar] [CrossRef]

- Cousineau, M.; Cougo, B. Interleaved converter with massive parallelization of high frequency GaN switching-cells using decentralized modular analog controller. In Proceedings of the 2015 IEEE Energy Conversion Congress and Exposition (ECCE); 2015; pp. 4343–4350. [Google Scholar] [CrossRef]

- Le Bolloch, M.; Cousineai, M.; Meynard, T. New Masterless Modular Current-Sharing technique for DC/DC Parallel converters. In Proceedings of the Proceedings of 14th International Power Electronics and Motion Control Conference EPE-PEMC 2010 2010, T3–73–T3–80. [Google Scholar] [CrossRef]

- Fabre, J.; Ladoux, P. Parallel Connection of 1200-V/100-A SiC-MOSFET Half-Bridge Modules. IEEE Transactions on Industry Applications 2016, 52, 1669–1676. [Google Scholar] [CrossRef]

- Sahoo, S.K.; Bhattacharya, T. Phase-Shifted Carrier-Based Synchronized Sinusoidal PWM Techniques for a Cascaded H-Bridge Multilevel Inverter. IEEE Transactions on Power Electronics 2018, 33, 513–524. [Google Scholar] [CrossRef]

- Huang, Q.; Huang, A.Q. Feedforward Proportional Carrier-Based PWM for Cascaded H-Bridge PV Inverter. IEEE Journal of Emerging and Selected Topics in Power Electronics 2018, 6, 2192–2205. [Google Scholar] [CrossRef]

- Tengfei Wang.; Yongqiang Zhu. Analysis and comparison of multicarrier PWM schemes applied in H-bridge cascaded multi-level inverters. In Proceedings of the 2010 5th IEEE Conference on Industrial Electronics and Applications, 2010, pp. 1379–1383. [CrossRef]

- Arazm, S.; Vahedi, H.; Al-Haddad, K. Phase-shift modulation technique for 5-level packed U-cell (PUC5) inverter. In Proceedings of the 2018 IEEE 12th International Conference on Compatibility, Power Electronics and Power Engineering (CPE-POWERENG 2018); 2018; pp. 1–6. [Google Scholar] [CrossRef]

- Vivert, M.; Cousineau, M.; Ladoux, P.; Fabre, J.; Mannes-Hillesheim, M.; Diez, R.; Patino, D. Decentralized Control for Balancing the Cell Voltages of a High Conversion Ratio Flying Capacitor Multilevel Converter. IEEE Journal of Emerging and Selected Topics in Industrial Electronics 2022, 3, 635–646. [Google Scholar] [CrossRef]

- Xu, B.; Tu, H.; Du, Y.; Yu, H.; Liang, H.; Lukic, S. A Distributed Control Architecture for Cascaded H-Bridge Converter. In Proceedings of the 2019 IEEE Applied Power Electronics Conference and Exposition (APEC); 2019; pp. 3032–3038. [Google Scholar] [CrossRef]

- Vivert, M.; Patino, D.; Diez, R.; Cobaleda, D.B.; Cousineau, M. Decentralized Controller for a Grid Tied Cascade Multilevel Invert. In Proceedings of the IEEE 3rd Colombian Conference on Automatic Control (CCAC); 2019. [Google Scholar]

- Achanta, P.K.; Maksimovic, D.; Ilic, M. Decentralized control of series stacked bidirectional DC-AC modules. In Proceedings of the 2018 IEEE Applied Power Electronics Conference and Exposition (APEC); 2018; pp. 1008–1013. [Google Scholar] [CrossRef]

- He, J.; Li, Y.; Liang, B.; Wang, C. Inverse Power Factor Droop Control for Decentralized Power Sharing in Series-Connected-Microconverters-Based Islanding Microgrids. IEEE Transactions on Industrial Electronics 2017, 64, 7444–7454. [Google Scholar] [CrossRef]

- Vivert, M.; Patino, D.; Diez, R. Variation of a sliding mode control applied to a trinary hybrid multilevel inverter. In Proceedings of the 2017 IEEE 3rd Colombian Conference on Automatic Control (CCAC); 2017; pp. 1–6. [Google Scholar] [CrossRef]

- Gray, R.M. Toeplitz and circulant matrices: a review; Now Publishers, 2006. [Google Scholar]

- Diego Bernal Cobaleda, Miguel Vivert, R.D.G.P. Low-Voltage Cascade Multilevel Inverter with GaN Devices for Energy Storage System. In Proceedings of the 13th IEEE International Conference on Power Electronics and Drive Systems (PEDS 2019), 2019.

Figure 1.

Cascaded Full-Bridge Multilevel Converter of N FBs

Figure 1.

Cascaded Full-Bridge Multilevel Converter of N FBs

Figure 2.

Equivalent circuit of the average model of the Cascaded Multilevel Converter of N FBs

Figure 2.

Equivalent circuit of the average model of the Cascaded Multilevel Converter of N FBs

Figure 3.

Equivalent circuit of the linear model of the Cascaded Multilevel Converter of N levels

Figure 3.

Equivalent circuit of the linear model of the Cascaded Multilevel Converter of N levels

Figure 4.

Block diagram of the linear model of the cascaded FB multilevel converter

Figure 4.

Block diagram of the linear model of the cascaded FB multilevel converter

Figure 5.

Block diagram of the control system computing the local duty-cycle of the cell.

Figure 5.

Block diagram of the control system computing the local duty-cycle of the cell.

Figure 6.

Block diagram of the linear model of the cascaded FB multilevel converter with the proposed controller in closed-loop chain of communication

Figure 6.

Block diagram of the linear model of the cascaded FB multilevel converter with the proposed controller in closed-loop chain of communication

Figure 7.

Block diagram of the Closed-Loop system with the proposed controller

Figure 7.

Block diagram of the Closed-Loop system with the proposed controller

Figure 8.

Simplified closed-loop transfer function of the system

Figure 8.

Simplified closed-loop transfer function of the system

Figure 9.

Bode diagram of , and

Figure 9.

Bode diagram of , and

Figure 10.

Bode diagram of , and of the CFBC

Figure 10.

Bode diagram of , and of the CFBC

Figure 11.

Setup of the Cascaded Full-Bridge Multilevel Inverter

Figure 11.

Setup of the Cascaded Full-Bridge Multilevel Inverter

Figure 12.

Modal response of the of the CFBMC with the decentralized controller

Figure 12.

Modal response of the of the CFBMC with the decentralized controller

Figure 13.

Load transient test as a DC/AC converter

Figure 13.

Load transient test as a DC/AC converter

Figure 14.

Input cell voltage step response simulation for the inverter case

Figure 14.

Input cell voltage step response simulation for the inverter case

Figure 15.

FB insertion simulation for blue the inverter case

Figure 15.

FB insertion simulation for blue the inverter case

Figure 16.

Load transient experimental test in DC/AC mode

Figure 16.

Load transient experimental test in DC/AC mode

Figure 17.

Input cell voltage disturbance experimental test.

Figure 17.

Input cell voltage disturbance experimental test.

Figure 18.

FB cell insertion experimental test in DC/AC mode

Figure 18.

FB cell insertion experimental test in DC/AC mode

Table 1.

Parameters of the CFBMC

Table 1.

Parameters of the CFBMC

| Parameter |

Value |

| Number of FBs N

|

5 |

| Input Voltage () |

|

| Input Inductance (L) |

|

| ESR of L (R) |

|

| Input Capacitance (C) |

|

| Drain-Source ON Resistance () |

|

| Frequency of the inverter (f) |

60 Hz |

|

as an inverter |

|

|

as a DC/DC converter |

|

| Switching frequency () |

12.5 kHz |

| Load Resistance () |

|

|

1884

|

|

39

|

|

37.7

|

Table 2.

Time constants of the CFBMC

Table 2.

Time constants of the CFBMC

|

Theoretical (ms) |

Simulated (ms) |

|

0.384 |

0.38 |

|

0.146 |

0.14 |

|

0.146 |

0.14 |

|

0.384 |

0.38 |

|

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).