1. Introduction

With the development of the Internet of Things (IoT) and smart living, our lives are increasingly convenient with the help of artificial intelligence and various sensors. As one of the most important sensing technologies, photodetectors that can accurately convert incident light into electrical signals are receiving more attention. Broadband photodetectors, ranging from ultraviolet to mid-infrared, have been widely applied in spectroscopic analysis, environmental monitoring, communication, imaging, and display. Traditional indicators used to evaluate photodetectors include stability, signal-to-noise ratio, sensitivity, speed, and selectivity. However, with the rapid advancement of miniaturized smart devices, new types of photodetectors require additional compatibility with integrated circuits to provide higher-level computational analysis functions such as logic analysis.

High-performance broadband photodetectors predominantly utilize costly III-V materials [

1,

2,

3] or two-dimensional materials [

4]. For instance, in the case of III-V materials like InAs/InAsSb superlattices, these detectors consist of a superlattice contact layer and an absorbing layer with an intermediate electron-blocking layer [

5]. The detection wavelength range is tailored by adjusting the periodicity of the superlattice in the absorbing layer. However, integrating III-V materials with other substances presents challenges due to lattice mismatch, leading to the formation of dislocations that significantly degrade device performance [

6,

7,

8]. Consequently, the materials employed in such detectors require specialized epitaxial techniques or additional electronic components for integration with silicon ICs, thereby complicating the direct realization of miniaturized smart devices and limiting their suitability to conventional applications. In contrast, silicon IC-compatible photodetectors enable the fabrication of silicon electronic devices and optical components on a single chip. This facilitates the creation of monolithic photon-electron systems with inherent capabilities for logic computation, storage, and interconnectivity, which assume significant importance in the present scenario.

Based on mature silicon-based processing technology, the material selection for silicon-based photodetectors has greatly benefited from p-type or n-type doping. The p-i-n type silicon photodetectors [

6,

7,

8] are widely used for visible light applications, including optical imaging and spectroscopic analysis. Additionally, metal-silicon and metal-oxide-silicon photodiodes offer improved electrical properties. However, silicon materials also exhibit limitations in terms of photosensitivity. The indirect bandgap of silicon makes it an incomplete optoelectronic material, as its material bandgap of 1.1 eV leads to reduced absorption beyond 800 nm, with a cutoff wavelength of around 1100 nm [

9,

10]. Consequently, silicon is not considered an ideal optoelectronic material beyond the visible light range. Furthermore, the non-direct bandgap characteristic of silicon results in decreased photodetection performance and introduces thermal noise. Overcoming these challenges and striving for higher-performance silicon-compatible photodetectors remains of utmost importance.

In recent years, the development of hot carrier technology at metal/silicon interface has attracted considerable attention and brought new concepts and approaches to silicon-based infrared sensing [

11,

12,

13]. Material selection plays an important role in achieving photoinduced hot carriers that are able to absorb infrared light on the silicon photonics system. Metal materials, due to their zero bandgap properties, have the potential to achieve broadband photon absorption [

14,

15,

16,

17] and are promising for infrared sensing. Material selection plays an important role in achieving photoinduced hot carriers that are able to absorb infrared light on the silicon photonics system. Metal materials, due to their zero bandgap properties, have the potential to achieve broadband photon absorption [

14,

15,

16,

17] and are promising for infrared sensing. Considering the special hot-carrier behaviors in nanoscale metals, increasing research has shown interest in developing infrared Schottky detectors using metals with nanometer features. In 2017, Zhiyang et al. proposed an efficient and low-cost plasmonic hot electron NIR (1200-1475 nm) photodetector based on an Au nanoparticle [

15]. In 2020, Yusheng et al. demonstrated that the enhanced responsivity is related to the location of the field enhancement, the responsivity of the nanoscale-Au film device was 1.8 mA/W at 1310 nm[

16]. These results already break the detection cutoff wavelength (1.1 μm) of the silicon material.

Nanoscale metals' potential to achieve infrared photodetector have already been demonstrated. However, in metal/silicon interface photodetectors, the presence of Fermi level pinning limits the barrier height and further restricts the detectable wavelength range of nanoscale-metal/silicon interface infrared photodetectors. Since Fermi levels of two materials must align with each other at the interface, there exist gap states that decay deeper into the semiconductor, known as metal-induced gap states (MIGS) responsible for a pinning of the surface energy state regardless of the metal used, namely the Fermi-level pinning. The dominant characteristic of these interface states changes from acceptor-like to donor-like, resulting in charge transfer across the interface and the formation of a dipole that tends to align the band edges at the zero-charge level, effectively pinning the metal Fermi level at the center of the semiconductor bandgap [

18,

19,

20,

21,

22]. Consequently, regardless of the metal used, there exists a barrier height of about 1/2 the semiconductor bandgap. It is known that inserting an insulating layer between the semiconductor and the metal can reduce the effect of Fermi level pinning [

23,

24,

25,

26,

27]. The purpose of the insulating layer is to weaken the penetration of metal wave functions into the semiconductor, reducing MIGS and thus reducing the pinning effect. However, the presence of the insulating layer also introduces high tunneling resistance, requiring a trade-off between reducing pinning and increasing tunneling in practical implementations.

Until now, most research efforts on Fermi level pinning have focused on optimizing electrode contacts in solar cells [

28,

29,

30] and gate characteristics in field-effect transistors [

31,

32,

33,

34,

35]. Research on Fermi level pinning in the hot carrier detection devices has mainly focused on enhancing the photoelectric response in the visible to near-infrared wavelength range [

15,

16,

17]. There has been relatively less discussion on using metal-insulator-semiconductor (MIS) structures to alleviate Fermi level pinning, reduce the effective barrier height, and improve the device response in the infrared wavelength range. In this work, we experimentally demonstrate that the barrier height variation at the Schottky junction strongly influences the detection capability of infrared photodetectors. By striking a balance between reducing pinning and increasing tunneling, the metal-silicon dioxide-silicon photodetector exhibits a response rate of 2.34×10

2 μA/W at 2 μm and 1.75 μA/W at 6 μm.

2. Materials and Methods

2.1. Device Fabrication

In the fabrication experiment, a (100) n-type silicon wafer with a resistivity of 2-7 Ω-cm, a thickness of 650 μm, and a phosphorus doping concentration of 7×10

14 cm

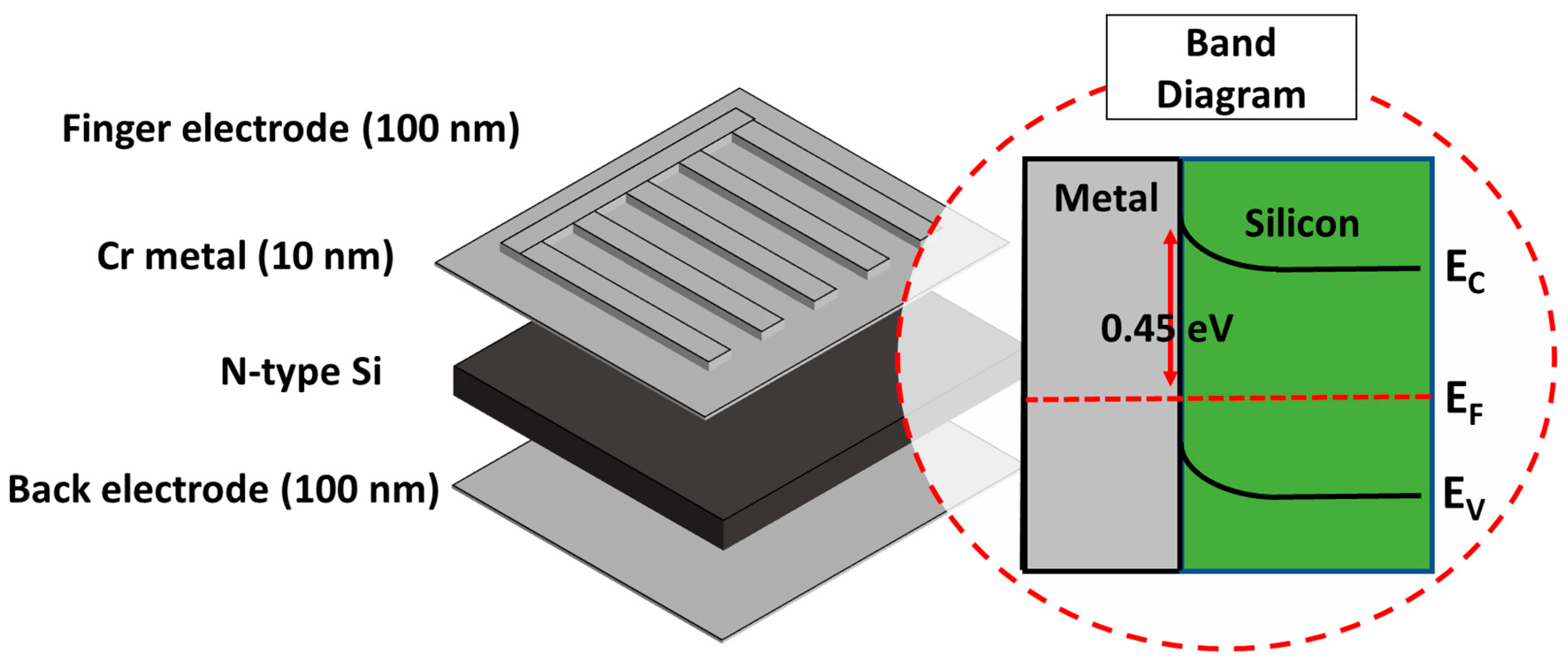

-3 was used. Initially, organic materials and the surface oxide layer were removed using organic solvents and buffered oxide etchant (BOE), respectively. Then, the cleaned wafer was loaded into an electron beam evaporation system (e-gun) to deposit a metal film. To form the Schottky contact, a 10 nm thick chromium layer was deposited on the substrate, followed by the deposition of a finger-shaped electrode with a thickness of 90 nm, resulting in a total thickness of 100 nm in the region with the finger-shaped electrode. Finally, a conductive layer was deposited on the backside as the back electrode to complete the device fabrication. The complete device structure is shown in

Figure 1. After the formation of the chromium-silicon Schottky contact, the Fermi levels of the metal and the semiconductor align, creating a barrier at the interface. Using the work function of the metal and the electron affinity of the semiconductor, the ideal chromium/silicon interface has a barrier height of 0.45 eV. However, due to the presence of Fermi level pinning, the Fermi level after junction formation is mostly pinned near the middle of the silicon bandgap. This can result in a high Schottky barrier, hindering carrier transport and reducing the detected photocurrent. Since silicon can form a silicon dioxide protective layer on the surface by oxidation in a high-temperature environment or in suitable chemical solutions, which is hard and insulated, it is possible to directly oxidize a silicon dioxide insulating layer on the silicon substrate surface through thermal oxidation or chemical oxidation. The modification of the interface dielectric of the silicon semiconductor were test whether it could reduce the Fermi level pinning effect and further enhance the photoelectric response in next chapter.

2.2. Device Characterization

The thermionic emission theory was utilized to fit and analyze the voltage-current characteristic curves of Schottky devices in many research [

36,

37,

38,

39]. There are many important physical parameters at the Schottky interface in thermionic emission theory, including the Schottky barrier height, series resistance, and quality factor [

39], which is able to affect the response. In order to discuss the relationship between optical response and the barrier height, series resistance and quality factor, it needs a more accurate way to estimate. The methods of directly fitting the characteristic curves and approximate estimation methods ignoring the series resistance that may have estimation errors were excluded. Instead, we adopt the approach of introducing additional adjustable physical variables and validating through repeated fitting to find the most accurate fitting results. If the adjusted values are consistent with the variations in the corresponding analysis factors, it indicates the accuracy of the analysis results. The fitting equation of the thermionic emission theory for Schottky devices is shown below [

39]:

In the Equation (1), V and I represent the applied bias voltage and the measured current of the device, respectively. A, A*, k, and q are known parameters representing the area of device, Richardson constant, Boltzmann constant, and electron charge, respectively. The analysis parameters include Rs (series resistance), B (barrier height), T (temperature), and n (ideality factor). For Schottky devices, an equivalent circuit with a series resistance can be utilized. Introducing an additional controllable series resistance as an experimental variable facilitates easy modification and adjustment of the circuit for testing purposes. The measurement system for the device's external resistance involves direct series connection with the device, while the IV characteristic curves are recorded using a Keithley 2400 source meter. The additive nature of resistance values in series allows the fitting result of the series resistance to validate the overall reference capability of the complete set of fitting parameters. By evaluating the numerical error rate between the fitted and actual added resistance, we can determine the most reliable parameter combination among the different fitting results.

3. Results

The metal/silicon interface, as a thermal carrier technology, is primarily determined by three key processes in its optoelectronic response: light absorption, the hot carrier generation, and the hot carrier transport and collection. When the metal/silicon interface is excited by light, plasmonic excitations are generated and decay, transferring energy to hot electrons. Due to the relaxation process of hot carriers, the hot electrons dissipate energy in the form of heat. However, through the formation of Schottky contacts between metal nanostructures and semiconductors, hot electrons with enough energy are able to be injected into the semiconductor and collected before their energy is lost.

In this study, we focus on discussing how the Schottky barrier height affects the injection efficiency of hot carriers. Since the parameters of the metal material and fabrication are fixed, and to verify the optical response of the device in the infrared wavelength range, a stable and adjustable infrared light source is required. A monochromator (CM110) controlled by LabVIEW software was used to control the detection wavelength for device measurements. Broadband infrared light ranging from 1.5 to 20 micrometers was separated into single-wavelength monochromatic light from 2 to 6 μm. The switching of the light signal was controlled by a chopper operating with a 10-second switching period. By analyzing the variation in the current levels of the device with and without infrared light illumination, the optical response of the device could be calculated. As a control group for the experiment, we fabricated devices with an active layer metal thickness of 10 nm and measured their response and absorption spectra.

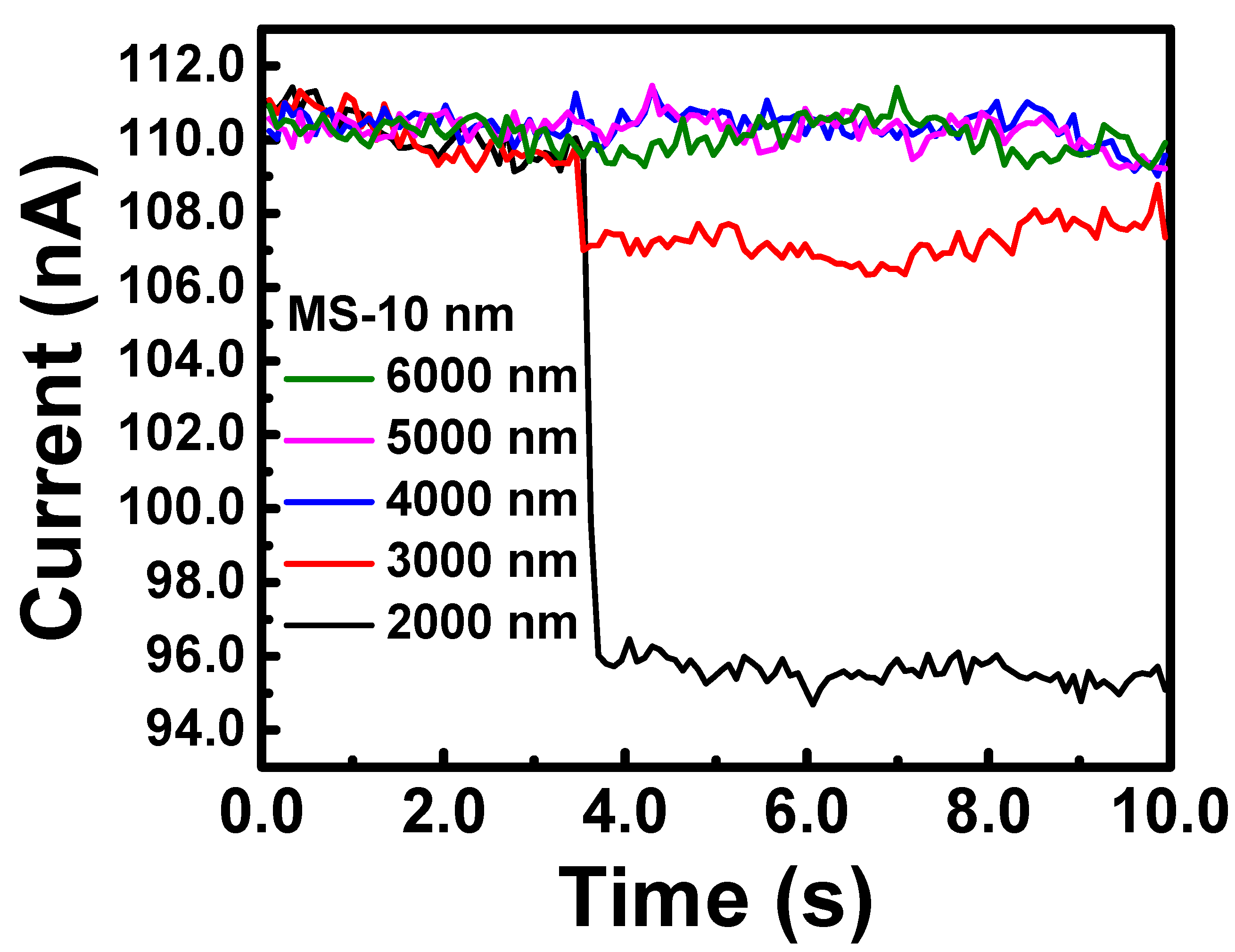

Figure 2 shows the variation in current levels for the device in the wavelength range of 2 to 6 μm.

The data of the infrared light source measurements for the device in

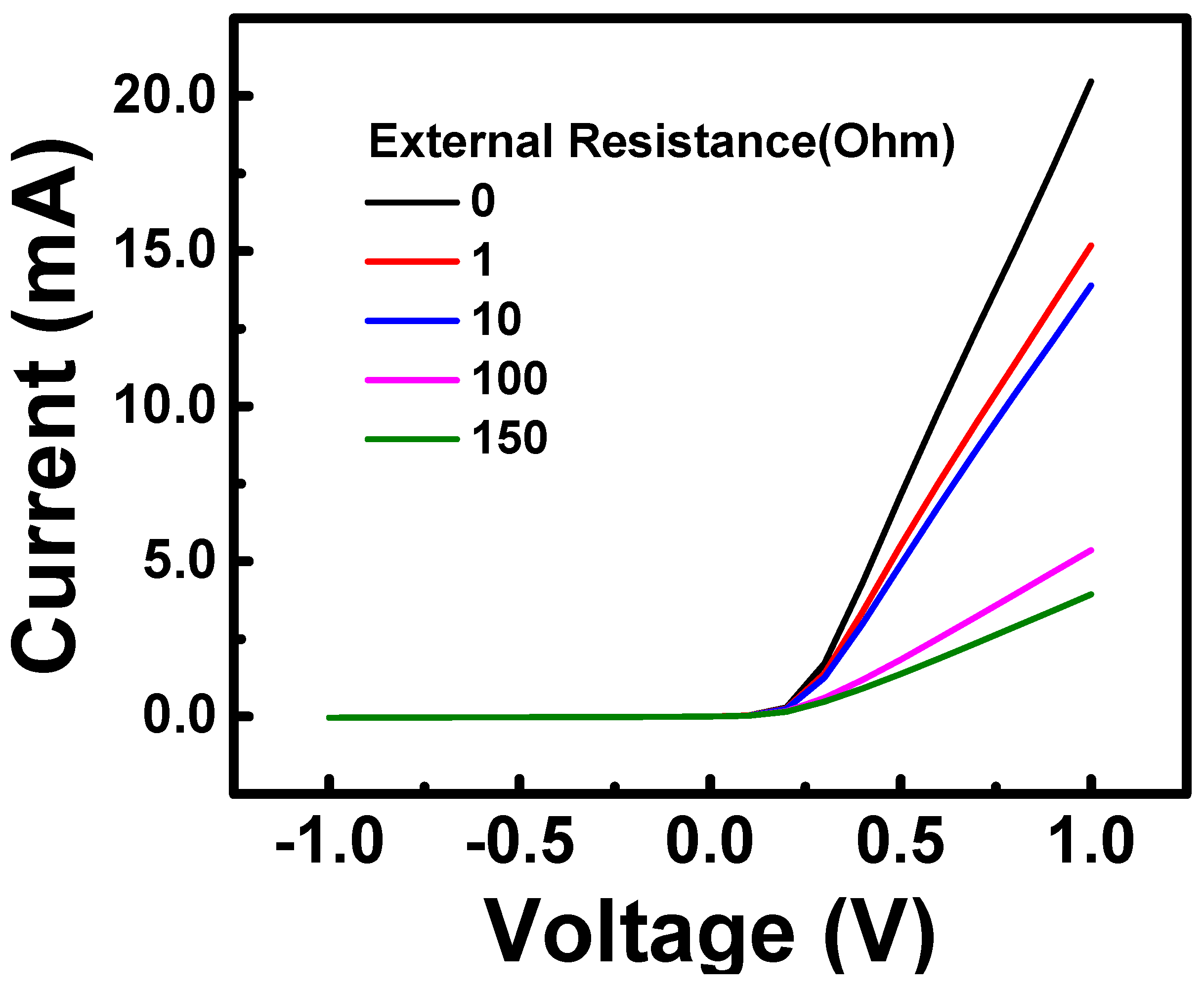

Figure 2 were quantitatively analyzed. First, the response current was calculated by subtracting the current level without light illumination from the current level during light illumination. The device with an active layer metal thickness of 10 nm with a response current of 14 nA at a wavelength of 2 μm. Although the response was smaller at the 3 μm wavelength, there was still a response current of 2.9 nA. Next, the dark current variation the barrier height was further measured and analyzed. In order to discuss the relationship between optical response and the barrier height, the current-voltage characteristic curves for different external resistances ranging from 0 to 150 Ω were measured, and the results are shown in

Figure 3. For the Schottky barrier device, the circuit can be equivalently represented as a circuit with a series resistance. Therefore, if the fitting result is accurate, the value of the additional series resistance will only be reflected in the change of the fitting resistance value. The equation (1) was used in this analysis.

Table 1 records the results of the analysis for Rs, n, barrier height, and temperature. To estimate the error rate, ΔRs is defined as the difference between the fitting results with and without an external resistance. The relative error is defined as the difference between ΔRs and Rex divided by Rex. Since the error rate of the resistance meter used is 5%, a 5% standard was also adopted when evaluating the fitting results. Under the evaluation standard of an error rate <5%, the series resistance, ideality factor, and barrier height of the chromium metal/n-Si device we fabricated were determined to be 29.9 Ω, 1.49, and 0.56 eV, respectively. From these results, it can be observed that the device exhibits a significant Fermi level pinning effect, with a value very close to the midpoint of the silicon bandgap (0.55 eV), showing a deviation of 0.11 eV from the ideal chromium/n-Si barrier of 0.45 eV. If the barrier can be further reduced, there is a chance to measure signals at longer wavelengths.

To reduce the Fermi level pinning effect, we incorporated an oxidation process on the surface of the fabrication. A piranha solution of sulfuric acid and hydrogen peroxide was utilized to generating a uniform and stable oxide layer on the silicon substrate surface, while remove organic materials. This oxide layer provides good insulation and chemical stability, effectively suppressing background noise in the Schottky barrier device. The oxidation times were set at 30, 60, 120, and 180 seconds, while the metal thickness was chosen to be 10 nm.

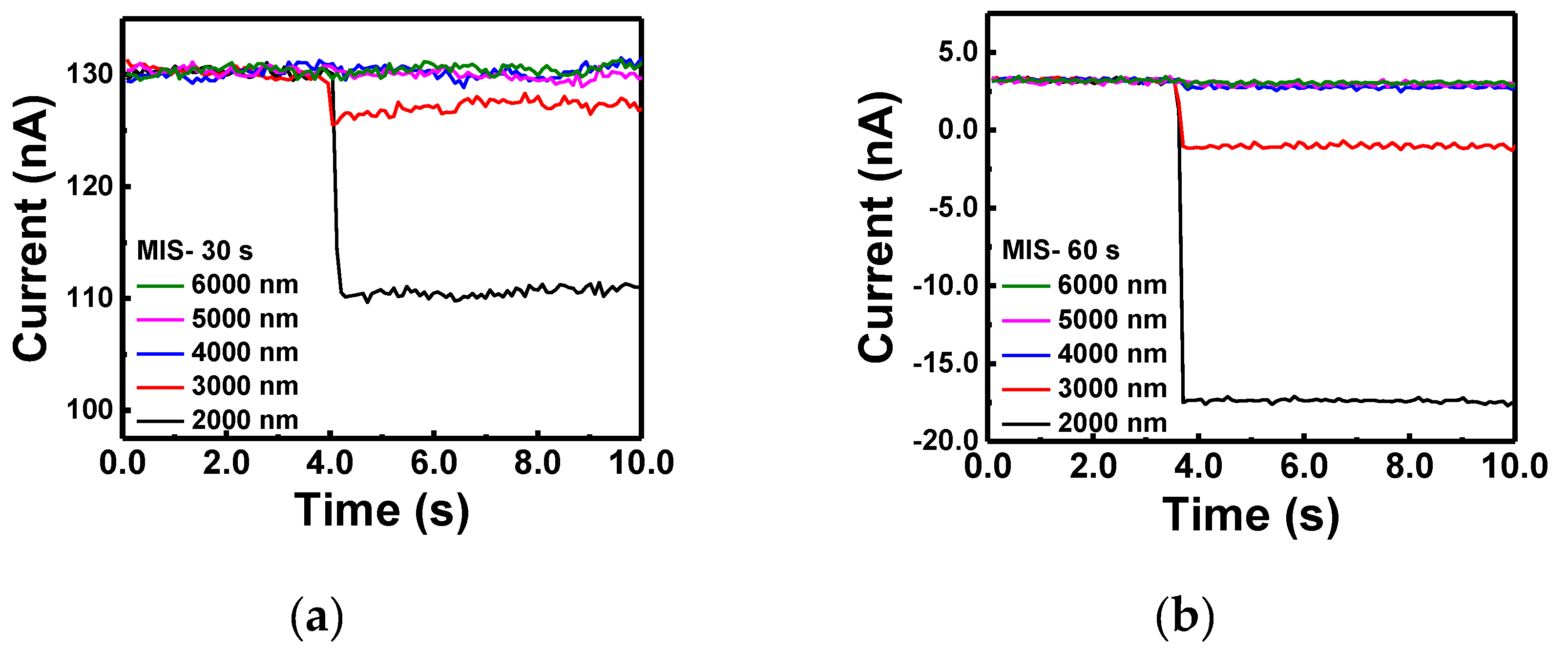

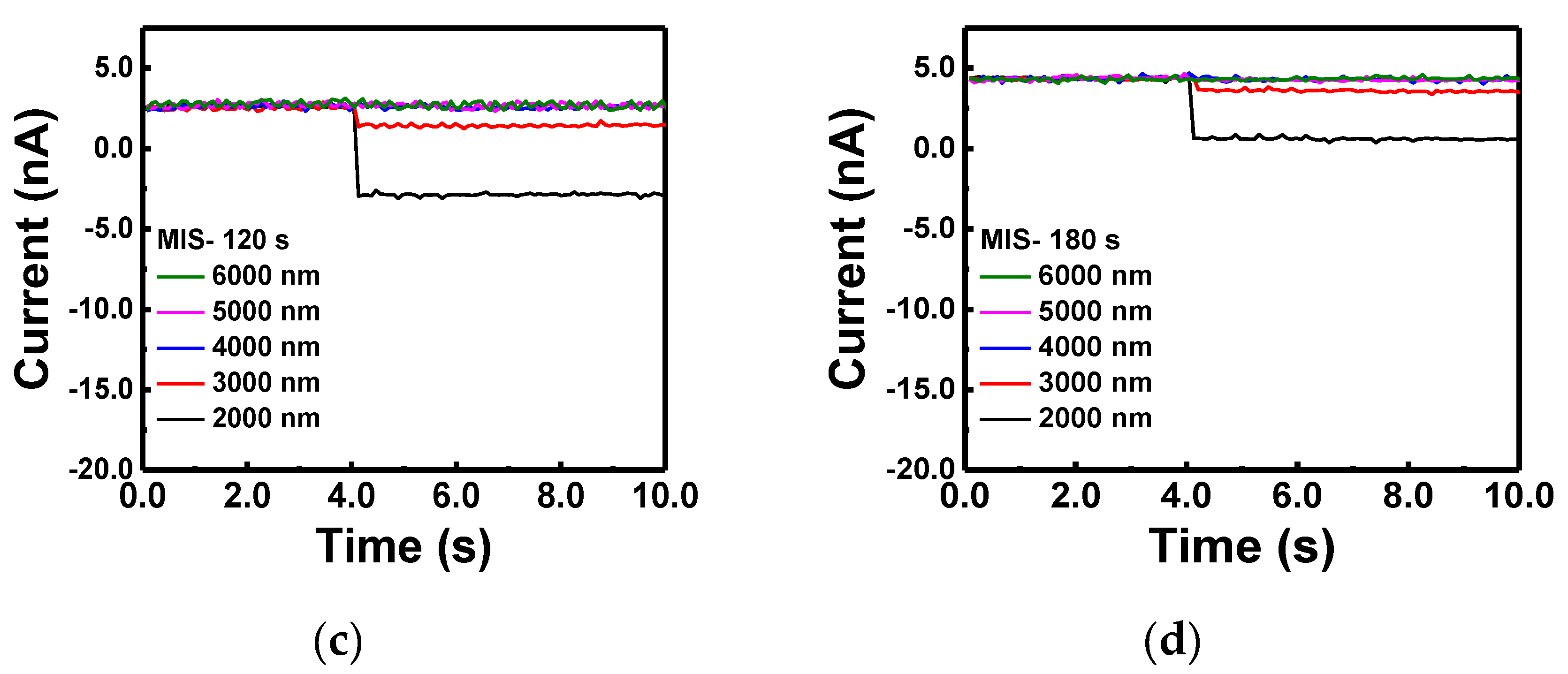

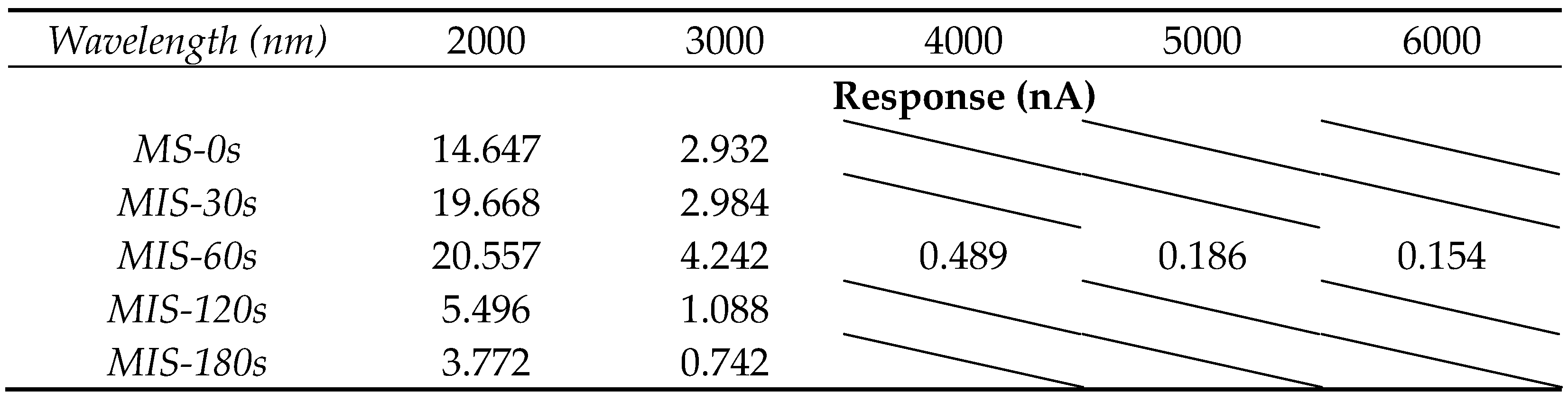

Figure 4a–d show the variation of current levels with time at wavelengths of 2 to 6 μm for devices subjected to oxidation times of 30, 60, 120, and 180 seconds, respectively. For comparison, we also quantitatively analyzed the data of the infrared light source measurements for each parameterized device in

Figure 4 and compiled the results in

Table 2.

4. Discussion

After optimizing the silicon surface through the oxidation passivation process, the response of the fabricated devices showed an initial increase followed by a decrease as the oxidation time parameter increased. The device with an oxidation time of 60 seconds exhibited the best response measurement, with a 145% improvement compared to the device without an oxide layer. Additionally, the devices with the oxide layer showed a significant reduction in background noise. In the devices without the oxide layer, the root mean square (RMS) value of the noise was approximately 0.43 nA, which decreased to 0.09 nA after the addition of the oxidation process. This indicates that the presence of the oxide layer has a certain impact on the metal/semiconductor contact interface. To estimate the variation of the barrier height in devices with different process parameters, we also measured and analyzed the I-V characteristics of different devices, as shown in

Figure 5. The results of the analysis for Rs, n, barrier height, and temperature are recorded in

Table 3. The barrier height gradually approaches the ideal barrier height (0.45 eV) with the addition of the oxide layer, decreasing from the originally pinned position of 0.56 eV to 0.49 and 0.47 eV. Therefore, in devices with an oxidation time of less than 60 seconds, the response is optimized with the addition of the oxide layer. Furthermore, from the fitting results of the ideality factor, the ideality factor value continuously increases with the increase in oxidation time. This indicates that the device characteristics deviate further from the ideal metal/semiconductor structure. A reasonable ideality factor value generally falls between 1 and 2, and the device with an oxidation time of 60 seconds already meets the acceptable minimum standard for a diode. The thicker oxide layer would make it difficult for carriers to tunnel from the metal into the semiconductor, resulting in additional decay during measurements. This explains why the response decreases in devices with oxidation times of 120 and 180 seconds.

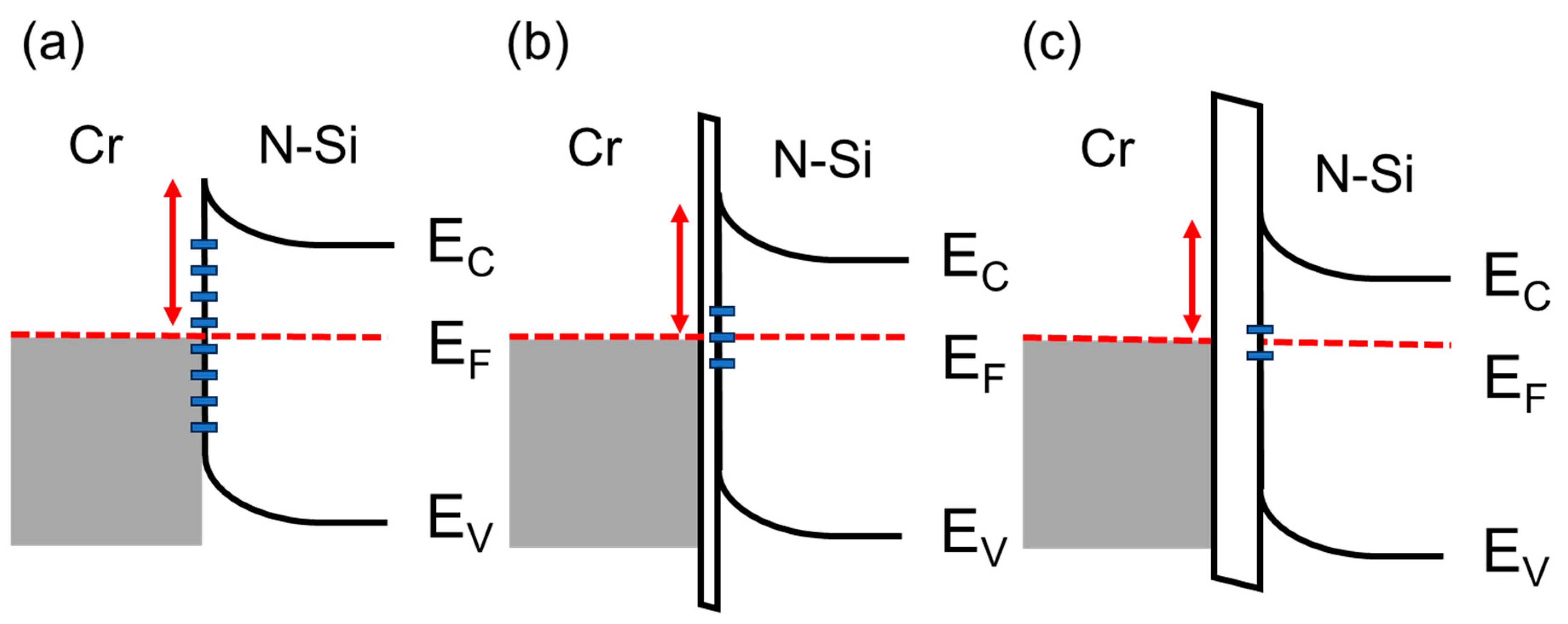

The above discussion addressed the influence of Schottky interface parameters (barrier height, ideality factor) on current. Based on this, we can summarize in a more comprehensive manner how the experimental procedures step by step affect the interface physics and the physical significance represented by the ideality factor. In

Figure 6a–c, we illustrate the band diagrams of the metal/semiconductor and metal/oxide/semiconductor structures. Due to the stronger Fermi level pinning effect, the metal/semiconductor structure exhibits a higher pinned barrier of 0.56 eV and noise value of 0.43 nA, and the smallest ideality factor of 1.492. As the oxide structure is introduced, a very thin oxide layer appears at the interface. The Schottky barrier (0.49 eV) in this case is between the pinned barrier and the ideal barrier. On the other hand, the insulating layer effectively suppresses dark current (0.09 nA) and enhances device signal performance. However, with the addition of the oxide layer, the structure deviates from the ideal Schottky structure, resulting in an increase in the ideality factor value. When the oxidation time increases further, a thicker oxide layer exists between the metal and the semiconductor, significantly reducing the chance of carrier tunneling. In addition to further reducing background noise, the photocurrent also decreases accordingly. At this stage, even though the interface exhibits a barrier height (0.47 eV) closest to the theoretical value, the optical response is greatly reduced due to the inability of carriers to tunnel through.

Detectivity (D*) is widely recognized as the ultimate parameter for evaluating the performance of photodetectors [

40,

41,

42,

43]. A crucial aspect of detectivity is that higher values correspond to superior detector performance. It can be defined as the ratio of the signal-to-noise (SNR) generated in a photodetector operating under specific conditions: an incident power of 1 W, an area of 1 cm2, and a noise bandwidth of 1 Hz. The utilization of the square root of the area of photodetector in the calculation of detectivity plays a significant role. This factor effectively neutralizes the influence of the size of detector, allowing for a more objective evaluation of the device's performance. The equation of detectivity is shown below [

40]:

where A is the effective area of the detector (6.25 cm

2) and Δf is the bandwidth. When the Inoise is dominated by the background noise. And the 1Hz noise spectrum component is taken as the value of the Inoise.

Table 4 presents the optical responsivity and detectivity of the MIS-60s device. The responsivity and the detectivity are obtained by dividing the response currents by the power at each wavelength and equation (2), respectively. This device exhibits a responsivity in the μA/W range for the 2-6 μm wavelength band, and a detectivity exceeding 10

6 for the 2-5 μm wavelength band.

5. Conclusions

In conclusion, the nanoscale-Cr/n-Si Schottky photodetector has been demonstrated that the enhanced responsivity is related to the Fermi-level pinning effect of Schottky interface. Firstly, by analyzing the I-V curve and the thermionic emission equation of the 10 nm thick Cr/n-Si Schottky device, the Schottky barrier height was determined to be 0.56 eV, which is close to the bandgap of the silicon material. This indicates the presence of a significant Fermi level pinning effect at the Cr/n-Si interface. Under illumination conditions with a 2 μm light source, the responsivity of the Cr/n-Si device is 167 μA/W. After surface passivation of the silicon material, the initially fixed barrier height gradually decreases to 0.49 eV and 0.47 eV, closer to the theoretical Cr/n-Si barrier height of 0.45 eV. Also, the noise decreases from 0.43 nA to 0.09 nA and the responsivity exhibits a 45% improvement. Under illumination conditions with a 2 μm light source, the responsivity of the Cr/SiO2/n-Si device is 234 μA/W. Furthermore, the barrier height engineering allows the devices to exhibit responsivity to light at wavelengths of 4, 5, and 6 μm, which are 5.56, 2.11, and 1.75 μA/W, respectively. Traditionally, the limitation of silicon bandgap has restricted silicon photonics system’s applications in fields such as optical communication and optical sensing. However, sensors with less Fermi-level pinning effect are able to extend the sensing wavelength range, offering the opportunity for silicon-based sensing to operate in a broader spectrum. This advancement can help expand the range and functionality of silicon photonics systems.

Author Contributions

Conceptualization, Z.-C.S. and C.-F.L.; methodology, Z.-C.S.; software, Z.-C.S.; validation, Z.-C.S. and C.-F.L.; formal analysis, Z.-C.S. and C.-F.L.; investigation, Z.-C.S.; resources, C.-F.L.; data curation, Z.-C.S.; writing—original draft preparation, Z.-C.S.; writing—review and editing, C.-F.L.; funding acquisition, C.-F.L. All authors have read and agreed to the published version of the manuscript.

Funding

This work was financially supported by Ministry of Science and Technology (MOST 108-2221-E-002-145-MY3/ MOST 108-2218-E-002-032-MBK/ MOST 111-2221-E-002-080-MY3)/ MOST 111-2218-E-002-019-MBK in Taiwan.

Data Availability Statement

The data presented in this study are available on request from the corresponding author. The data are not publicly available due to privacy concerns.

Acknowledgments

Instrumentation Center of National Taiwan University, Taipei, Taiwan; Department of Chemical Engineering, National Taiwan University, Taipei, Taiwan; Center for Condensed Matter Sciences, National Taiwan University, Taipei, Taiwan

Conflicts of Interest

The authors declare no conflict of interest.

References

- Huang, T.; et al. Single-crystalline InGaAs nanowires for room-temperature high-performance near-infrared photodetectors. Nano-Micro Lett. 2016, 8, 29–35. [Google Scholar] [CrossRef]

- Miao, J.; Hu, W.; Guo, N.; Lu, Z.; Zou, X.; Liao, L.; Shi, S.; Chen, P.; Fan, Z.; Ho, J.C.; et al. Single InAs Nanowire Room-Temperature Near-Infrared Photodetectors. ACS Nano 2014, 8, 3628–3635. [Google Scholar] [CrossRef] [PubMed]

- Kuo, C.-H.; Wu, J.-M.; Lin, S.-J.; Chang, W.-C. High sensitivity of middle-wavelength infrared photodetectors based on an individual InSb nanowire. Nanoscale Res. Lett. 2013, 8, 327–327. [Google Scholar] [CrossRef] [PubMed]

- Shen, Y.; Li, Y.; Chen, W.; Jiang, S.; Li, C.; Cheng, Q. High-Performance Graphene Nanowalls/Si Self-Powered Photodetectors with HfO2 as an Interfacial Layer. Nanomaterials 2023, 13, 1681. [Google Scholar] [CrossRef]

- Huang, T.; et al. Single-crystalline InGaAs nanowires for room-temperature high-performance near-infrared photodetectors. Nano-Micro Lett. 2016, 8, 29–35. [Google Scholar] [CrossRef]

- Li, G.; Maekita, K.; Mitsuno, H.; Maruyama, T.; Iiyama, K. Over 10 GHz lateral silicon photodetector fabricated on silicon-on-insulator substrate by CMOS-compatible process. Jpn. J. Appl. Phys. 2015, 54, 04DG06. [Google Scholar] [CrossRef]

- Liu, J.; Zhu, K.-M.; Zaslavsky, A.; Cristoloveanu, S.; Arsalan, M.; Wan, J. Photodiode with low dark current built in silicon-on-insulator using electrostatic doping. Solid-state Electron. 2019, 168, 107733. [Google Scholar] [CrossRef]

- Ghioni, M.; Zappa, F.; Kesan, V.; Warnock, J. A VLSI-compatible high-speed silicon photodetector for optical data link applications. IEEE Trans. Electron Devices 1996, 43, 1054–1060. [Google Scholar] [CrossRef]

- Liu, A.; Liao, L.; Rubin, D.; Nguyen, H.; Ciftcioglu, B.; Chetrit, Y.; Izhaky, N.; Paniccia, M. High-speed optical modulation based on carrier depletion in a silicon waveguide. Opt. Express 2007, 15, 660–668. [Google Scholar] [CrossRef]

- Casalino, M.; Coppola, G.; Iodice, M.; Rendina, I.; Sirleto, L. Near-Infrared Sub-Bandgap All-Silicon Photodetectors: State of the Art and Perspectives. Sensors 2010, 10, 10571–10600. [Google Scholar] [CrossRef]

- Jalabert, R.; Das Sarma, S. Inelastic scattering in a doped polar semiconductor. Phys. Rev. B 1990, 41, 3651–3654. [Google Scholar] [CrossRef] [PubMed]

- Petersen, C.L.; Lyon, S.A. Observation of hot-electron energy loss through the emission of phonon–plasmon coupled modes in GaAs. Phys. Rev. Lett. 1990, 65, 760. [Google Scholar] [CrossRef] [PubMed]

- Sicault, D.; et al. Experimental study of hot-electron inelastic scattering rate in p-type InGaAs. Phys. Rev. B 2002, 65, 121301. [Google Scholar] [CrossRef]

- Hilsum, C. Infrared Absorption of Thin Metal Films. J. Opt. Soc. Am. 1954, 44, 188–191. [Google Scholar] [CrossRef]

- Qi, Z.; Zhai, Y.; Wen, L.; Wang, Q.; Chen, Q.; Iqbal, S.; Chen, G.; Xu, J.; Tu, Y. Au nanoparticle-decorated silicon pyramids for plasmon-enhanced hot electron near-infrared photodetection. Nanotechnology 2017, 28, 275202. [Google Scholar] [CrossRef]

- Zhai, Y.; Li, Y.; Ji, J.; Wu, Z.; Wang, Q. Hot Electron Generation in Silicon Micropyramids Covered with Nanometer-Thick Gold Films for Near-Infrared Photodetectors. ACS Appl. Nano Mater. 2020, 3, 149–155. [Google Scholar] [CrossRef]

- Su, Z.-C.; Li, Y.-H.; Lin, C.-F. Mid-Infrared Response from Cr/n-Si Schottky Junction with an Ultra-Thin Cr Metal. Nanomaterials 2022, 12, 1750. [Google Scholar] [CrossRef]

- Sotthewes, K.; Van Bremen, R.; Dollekamp, E.; Boulogne, T.; Nowakowski, K.; Kas, D. Universal Fermi-level pinning in transition-metal dichalcogenides. J. Phys. Chem. C 2019, 123, 5411–5420. [Google Scholar] [CrossRef]

- Yuan, H.; Cheng, G.; You, L.; Li, H.; Zhu, H.; Li, W.; Kopanski, J.J.; Obeng, Y.S.; Walker, A.R.H.; Gundlach, D.J. Influence of Metal-MoS2 Interface on MoS2 Transistor Performance: Comparison of Ag and Ti Contacts. ACS Appl. Mater. Interfaces 2015, 7, 1180–1187. [Google Scholar] [CrossRef]

- Kim, C.; Moon, I.; Lee, D.; Choi, M.S.; Ahmed, F.; Nam, S.; Cho, Y.; Shin, H.-J.; Park, S.; Yoo, W.J. Fermi Level Pinning at Electrical Metal Contacts of Monolayer Molybdenum Dichalcogenides. ACS Nano 2017, 11, 1588–1596. [Google Scholar] [CrossRef]

- Zhang, Y.; Chen, X.; Zhang, H.; Wei, X.; Guan, X.; Wu, Y.; Hu, S.; Zheng, J.; Wang, G.; Qiu, J.; et al. Fermi-Level Pinning Mechanism in MoS2 Field-Effect Transistors Developed by Thermionic Emission Theory. Appl. Sci. 2020, 10, 2754. [Google Scholar] [CrossRef]

- Sankey, O.F.; Allen, R.E.; Dow, J.D. Si/transition-metal Schottky barriers: Fermi-level pinning by Si dangling bonds at interfacial vacancies. Solid State Commun. 1984, 49, 1–5. [Google Scholar] [CrossRef]

- Khakbaz, P.; Driussi, F.; Giannozzi, P.; Gambi, A.; Lizzit, D.; Esseni, D. Engineering of metal-MoS2 contacts to overcome Fermi level pinning. Solid-State Electron. 2022, 194, 108378. [Google Scholar] [CrossRef]

- Connelly, D.; Faulkner, C.; Clifton, P.A.; Grupp, D.E. Fermi-level depinning for low-barrier Schottky source/drain transistors. Appl. Phys. Lett. 2006, 88, 012105. [Google Scholar] [CrossRef]

- Islam, R.; Shine, G.; Saraswat, K.C. Schottky barrier height reduction for holes by Fermi level depinning using metal/nickel oxide/silicon contacts. Appl. Phys. Lett. 2014, 105, 182103. [Google Scholar] [CrossRef]

- Kang, J.; Liu, W.; Sarkar, D.; Jena, D.; Banerjee, K. Computational Study of Metal Contacts to Monolayer Transition-Metal Dichalcogenide Semiconductors. Phys. Rev. X 2014, 4, 031005. [Google Scholar] [CrossRef]

- Park, I.; Lee, D.; Jin, B.; Kim, J.; Lee, J.-S. Improvement of Fermi-Level Pinning and Contact Resistivity in Ti/Ge Contact Using Carbon Implantation. Micromachines 2022, 13, 108. [Google Scholar] [CrossRef]

- Nazif, K.N.; Daus, A.; Hong, J.; Lee, N.; Vaziri, S.; Kumar, A.; Nitta, F.; Chen, M.E.; Kananian, S.; Islam, R.; et al. High-specific-power flexible transition metal dichalcogenide solar cells. Nat. Commun. 2021, 12, 1–9. [Google Scholar] [CrossRef]

- Elsmani, M.I.; Fatima, N.; Jallorina, M.P.A.; Sepeai, S.; Su’ait, M.S.; Ludin, N.A.; Teridi, M.A.M.; Sopian, K.; Ibrahim, M.A. Recent Issues and Configuration Factors in Perovskite-Silicon Tandem Solar Cells towards Large Scaling Production. Nanomaterials 2021, 11, 3186. [Google Scholar] [CrossRef]

- Miao, J.; Zhang, X.; Tian, Y.; Zhao, Y. Recent Progress in Contact Engineering of Field-Effect Transistor Based on Two-Dimensional Materials. Nanomaterials 2022, 12, 3845. [Google Scholar] [CrossRef]

- Richstein, B.; Hellmich, L.; Knoch, J. Silicon Nitride Interface Engineering for Fermi Level Depinning and Realization of Dopant-Free MOSFETs. Micro 2021, 1, 228–241. [Google Scholar] [CrossRef]

- Yang, J.-C.; Huang, H.-F.; Li, J.-H.; Lee, Y.-J.; Wang, Y.-H. Nitrogen plasma treatment of a TiO2 layer for MIS ohmic contact on n-type Ge substrate. Vacuum 2020, 171, 108996. [Google Scholar] [CrossRef]

- Shine, G.; Saraswat, K.C. Analysis of Atomistic Dopant Variation and Fermi Level Depinning in Nanoscale Contacts. IEEE Trans. Electron Devices 2017, 64, 3768–3774. [Google Scholar] [CrossRef]

- Agrawal, A.; Lin, J.; Zheng, B.; Sharma, S.; Chopra, S.; Wang, K.; Datta, S. Barrier height reduction to 0.15 eV and contact resistivity reduction to 9.1 × 10−9 Ω-cm2 using ultrathin TiO2−x interlayer between metal and silicon. In Proceedings of the 2013 Symposium on VLSI Technology, Kyoto, Japan, 11–13 June 2013. [Google Scholar]

- Dev, S.; Meena, M.; Vardhan, P.H.; Lodha, S. Statistical Simulation Study of Metal Grain-Orientation-Induced MS and MIS Contact Resistivity Variability for 7-nm FinFETs. IEEE Trans. Electron Devices 2018, 65, 3104–3111. [Google Scholar] [CrossRef]

- Zhang, T.; et al. Measure and analysis of 4H-SiC Schottky barrier height with Mo contacts. Eur. Phys. J. Appl. Phys. 2019, 85, 10102. [Google Scholar] [CrossRef]

- Orak, I.; et al. The analysis of the electrical and photovoltaic properties of Cr/p-Si structures using current-voltage measurements. Silicon 2018, 10, 2109–2116. [Google Scholar] [CrossRef]

- Bozhkov, V.G.; Torkhov, N.A.; Shmargunov, A.V. About the determination of the Schottky barrier height with the C-V method. J. Appl. Phys. 2011, 109, 073714. [Google Scholar] [CrossRef]

- Raynaud, C.; Isoird, K.; Lazar, M.; Johnson, C.M.; Wright, N. Barrier height determination of SiC Schottky diodes by capacitance and current–voltage measurements. J. Appl. Phys. 2002, 91, 9841–9847. [Google Scholar] [CrossRef]

- Ji, C.H.; Kim, K.T.; Oh, S.Y. High-detectivity perovskite-based photodetector using a Zr-doped TiOx cathode interlayer. RSC Adv. 2018, 8, 8302–8309. [Google Scholar] [CrossRef]

- Wu, D.; et al. Ultrabroadband and high-detectivity photodetector based on WS2/Ge heterojunction through defect engineering and interface passivation. ACS Nano 2021, 15, 10119–10129. [Google Scholar] [CrossRef]

- Dou, L.; You, J.; Hong, Z.; Chang, W.-H.; Li, G.; Yang, Y. Solution-processed hybrid perovskite photodetectors with high detectivity. Nat. Commun. 2014, 5, 5404–5404. [Google Scholar] [CrossRef] [PubMed]

- Yu, Y.Y.; Peng, Y.C.; Chiu, Y.C.; Liu, S.J.; Chen, C.P. Realizing Broadband NIR Photodetection and Ultrahigh Responsivity with Ternary Blend Organic Photodetector. Nanomaterials 2022, 12, 1378. [Google Scholar] [CrossRef] [PubMed]

|

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).