1. Introduction

In the last two decades, tremendous and rapid technological advancement has been observed in the world of electronics. The shrinking of feature size (i.e., channel length of a transistor) is a testament to this advancement. Although digital circuits has already been working on technology nodes (interchangeable with channel length) lower than 5nm[

1,

2], their analog circuit counterparts did not advance at the same pace. For the past two decades, most of the analog circuits has been developed using 180 nm node or above [

3,

4,

5,

6,

7,

8,

9,

10,

11,

12,

13,

14,

15,

16] because of some benefits enjoyed by the larger technology nodes, for example, ease of design, larger amplification etc. However, in mixed-signal circuits, analog circuits need to be fabricated with the digital circuits on the same chip to meet various purposes[

17]. One such analog circuit is an operational amplifier (OPAMP), which usually has two inputs and a single output.

OPAMPs are versatile integrated circuits (ICs) widely used in various applications, including small-signal amplification, filtering, wave generations, arithmetic operations, and analog-to-digital (ADC) and digital-to-analog (DAC) conversion. In recent years, novel OPAMP architectures have emerged [

18,

19,

20,

21] aiming to enhance their functionality for specific domains. One such critical domain is biomedical electronics, where OPAMPs play a crucial role[

22] and serve as fundamental building blocks. In biomedical electronic circuits, OPAMPs need to address the unique features demanded by bio-potential signals (i.e. ECG), which include high amplification (as these signals are inherently weak), low noise levels (to ensure accurate signal acquisition and subsequent processing), and low power consumption. These features become indispensable for portable medical devices such as ECG monitors, where OPAMPs are commonly used for acquiring ECG signals generated by heart [

23] to enable precise monitoring and diagnosis. OPAMPs are also extensively employed in other medical platforms, including diagnostics, therapy, imaging, and instrumentation. The versatility and adaptability of OPAMPs continue to drive innovation in healthcare technology [

24].

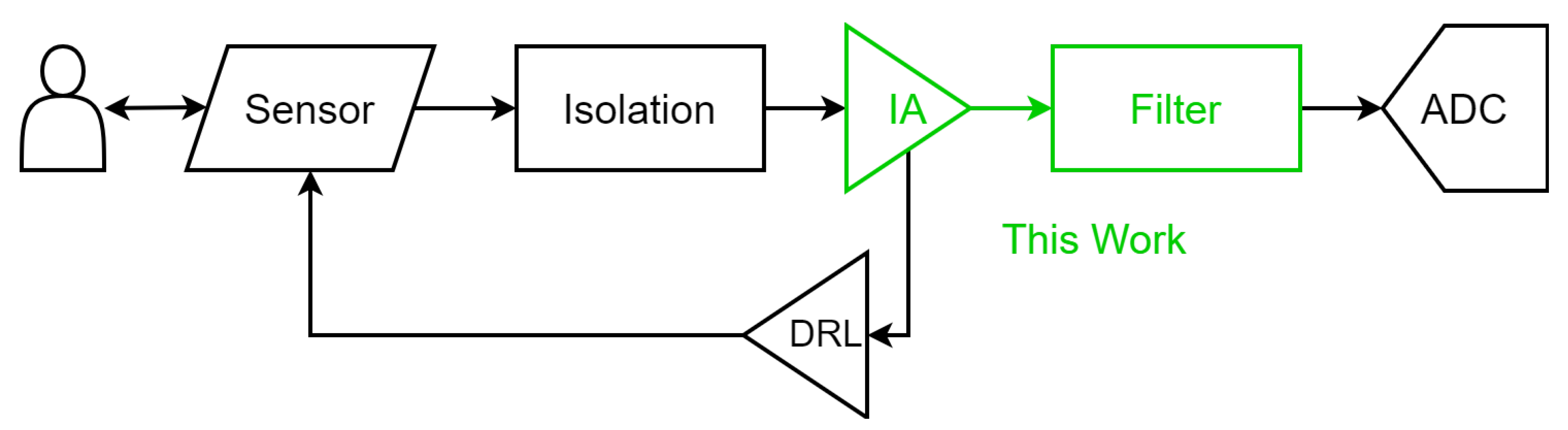

Figure 1 shows a typical block diagram of an Analog Front End (AFE) for an ECG acquisition system. This work focuses on the blocks highlighted in this figure.

In comparison with analog circuits, designing digital circuits requires less effort as the input signals are limited to only two voltage levels- logic 1 (HIGH) and logic 0 (LOW). Indeed, digital circuit design principle utilizes the switching (ON or OFF) concept which can be easily realized by transistors, like MOSFET or BJT. But on the other hand, analog circuits deal with continuous signals, comprising of infinite voltage levels. This increases complexity in design. Analog circuits mostly use transistors to amplify signals. Multiple transistors are used to design a circuit that can implement mathematical functions on signals, known as OPAMP. Most of the studies focus on design of OPAMP in larger nodes : on the likes of 180nm or more. Very few study can be found for design in 90nm[

25] and 45nm[

26,

27]. It is due to the fact that below 180nm channel length the transistors suffer greatly from short channel effects. This effect is not accounted for, in widely used long channel model (also known as Ideal or Shockley model). This adds to the design complexity. But lower technology nodes (smaller channel length) can offer great benefits in terms of performance parameters. The long channel model, which is widely used for analog circuit design, is not very accurate for lower nodes. There are other models, such as EKV, BSIM, etc., that can better predict the transistor behavior in lower nodes, but they are too complex to use for analog circuit design, as they involve too many variables and also lacks well established design flow.

The

method can simplify the design process for the designers [

28], as

parameter is not dependent on any model equation and is applicable in all regions of operation. For this semi-empirical approach, the necessary curves are generated directly from the simulator, which closely matches the actual measurement. In [

29], design and analysis of different OPAMP architectures are discussed, where long-channel MOSFET models are used. It is very difficult to design circuits in low technology nodes (channel length ≤ 180 nm) using the long-channel model. The

method explained in [

28] provides various examples of design with MATLAB scripts. The method utilizes Look-Up Table (LUT), but it lacks the analysis of circuit to meet multiple specifications such as power, Gain-Bandwidth product (GBW), Power Supply Rejection Ratio (PSRR), Common Mode Rejection Ratio (CMRR) etc. Also, no specific design methodology is discussed in this work and searching values from a table can become tedious and time consuming. The work in [

30] describes the use of a licensed software called ‘Analog Designer’s Toolbox’ in short ADT. To use the toolbox, the user needs to provide MOSFET model parameters in written form. The integrated circuit designer’s usually have access to realistic models provided by manufacturing companies (such as TSMC). Deriving necessary parameters from these realistic models for the ADT toolbox adds more design complexity. The authors in [

31], discuss the design of differential amplifier circuit using

methodology. This work assumes some specifications. The design process involves solving a number of equations using the specifications. In solving these equations, a lot of the unknown variable values are required. In finding those variable values, the authors needed more characteristic curves. The work of [

32] focuses on design of CMOS Telescopic OTA. The authors only mentioned a design flow using

but didn’t explain the flow. The selection of design parameters from

curves or LUT were not demonstrated. All the cited works except [

32] lack usage of realistic MOSFET models of various technology nodes (such as 45 nm, 90 nm, 180 nm etc. models from TSMC) resulting in inaccuracy in design to some extent.

In this work, the characteristic curves generated from the simulator (Cadence) using realistic MOSFET model from TSMC (45 nm) are used. ‘SPICE’ simulators can also be used to generate the curves. An efficient script which can be used to generate all the necessary curves at once is developed. This script can be used inside the simulator. We have developed a design methodology which involves analysis of the selected circuit (2 stage OTA) to meet multiple specifications (Power, GBW, CMRR, PSRR, Noise etc.) through a step-by-step design process using the

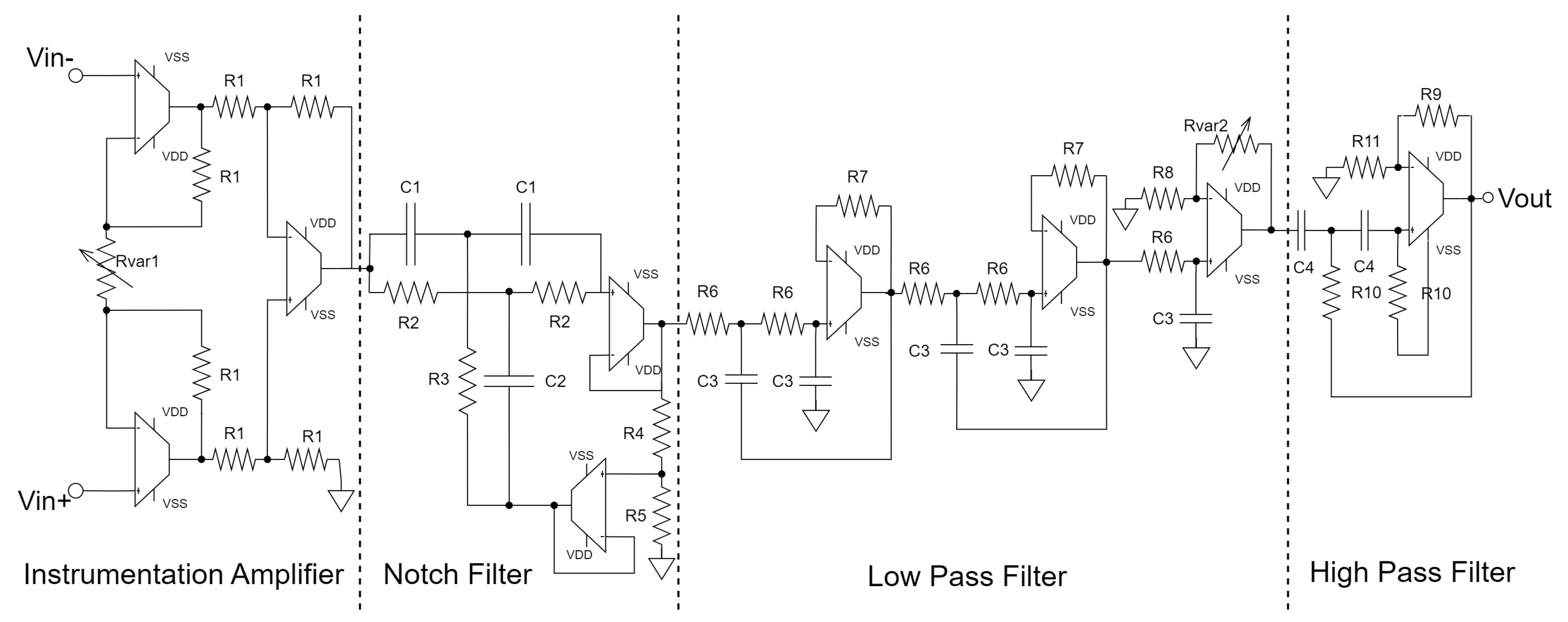

curves and optimization approaches. In the proposed design flow, the usage of design equations is minimized, which eliminates the determination of unknown variable values from characteristic curves. As a result, the number of the necessary characteristic curves are minimized. The proposed design flow is presented through a flow chart for better understanding. Using this systematic design process flow, an OTA (interchangeable with OPAMP) in 45 nm technology node is designed, which is used to implement the various blocks - an instrumentation amplifier, a notch filter, a low-pas filter, and a high-pass filter of the proposed ECG acquisition system as shown in

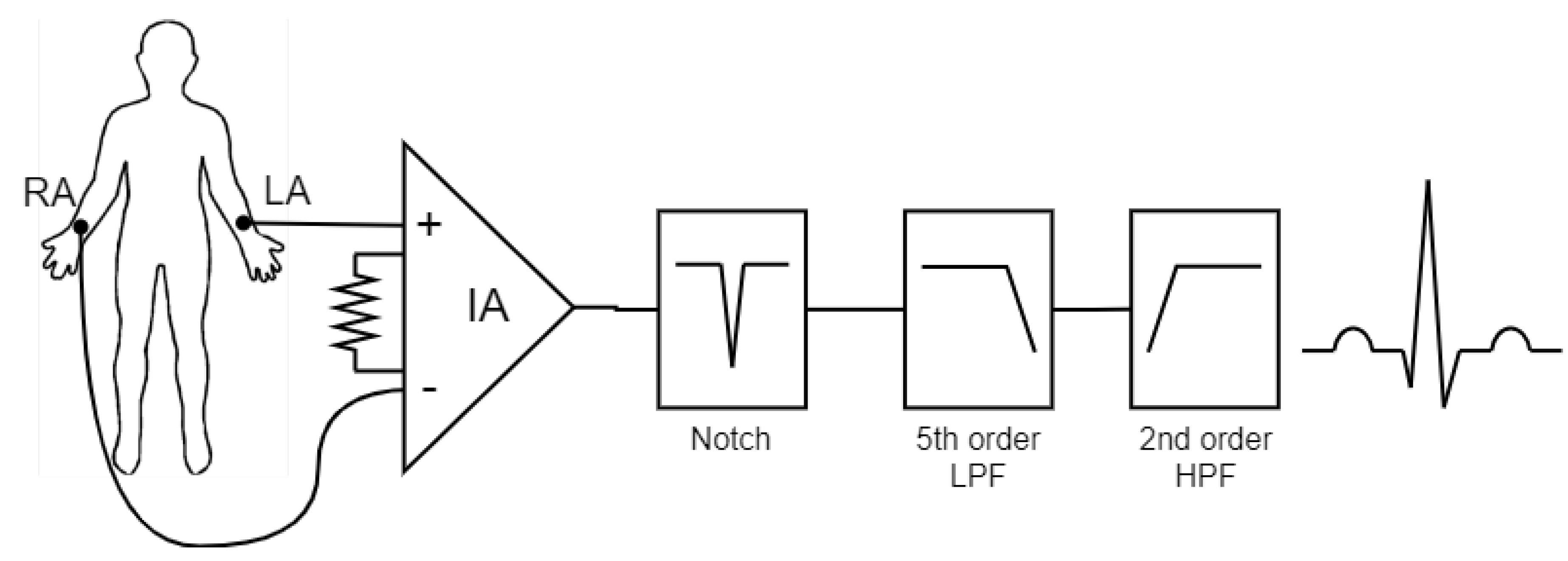

Figure 2. The target performance metrics are verified through various simulations which includes transient, ac, stability, noise, common-mode rejection ratio (CMRR), power-supply rejection ratio (PSRR), total harmonic distortion (THD) etc.

The paper is structured as follows.

Section 2 presents the detail explanation of the developed methodology which includes analysis and design of the OTA. Design constraints and design of ECG acquisition system is explained in

Section 3. A simple and brief review on various types of analyses required for analog integrated circuits are mentioned in

Section 4.1.

Section 4.2.1 explains the schematic level simulations of the designed OTA and compares the result with contemporary designs. ECG acquisition system simulations are shown and analysed in

Section 4.2.2.

Section 4.3 presents the layout implementation and also demonstrates the post-layout simulations of both the OTA and the whole ECG acquisition system. Conclusions of the work are drawn in

Section 5. This section includes the comparison with recent reported works.

4. Simulation and Results

The section portrays the various simulation results and discusses the findings. A brief introduction to various ‘analyses’ is given first in

Section 4.1. Then pre-layout simulations of the OTA and the proposed ECG acquisition system are shown in

Section 4.2, followed by the post-layout simulations in

Section 4.3. A comparison with the recent works is stated in

Section 4.4. Here, all the simulations were carried out in Cadence virtuoso software using the 45 nm MOSFET model by TSMC.

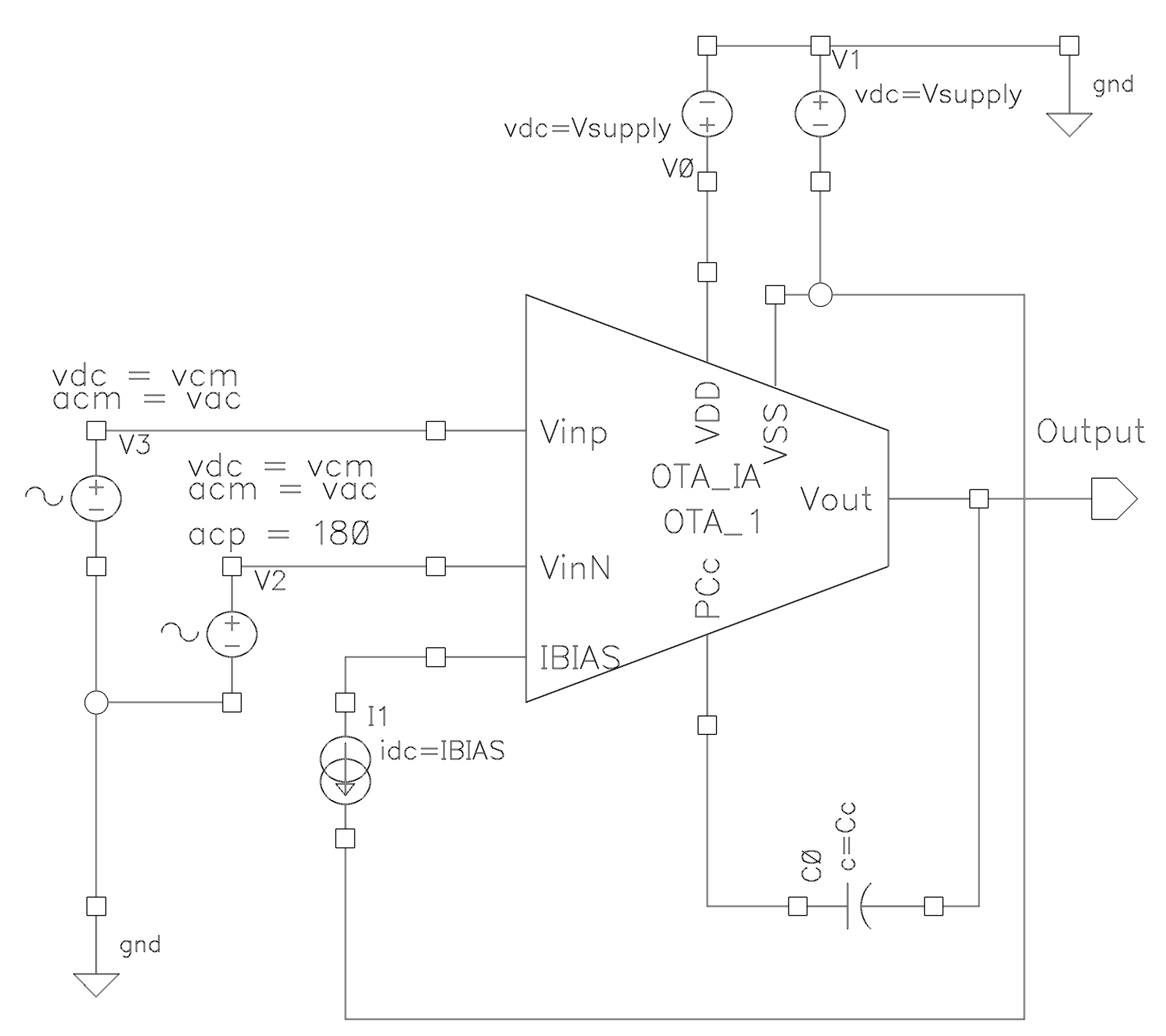

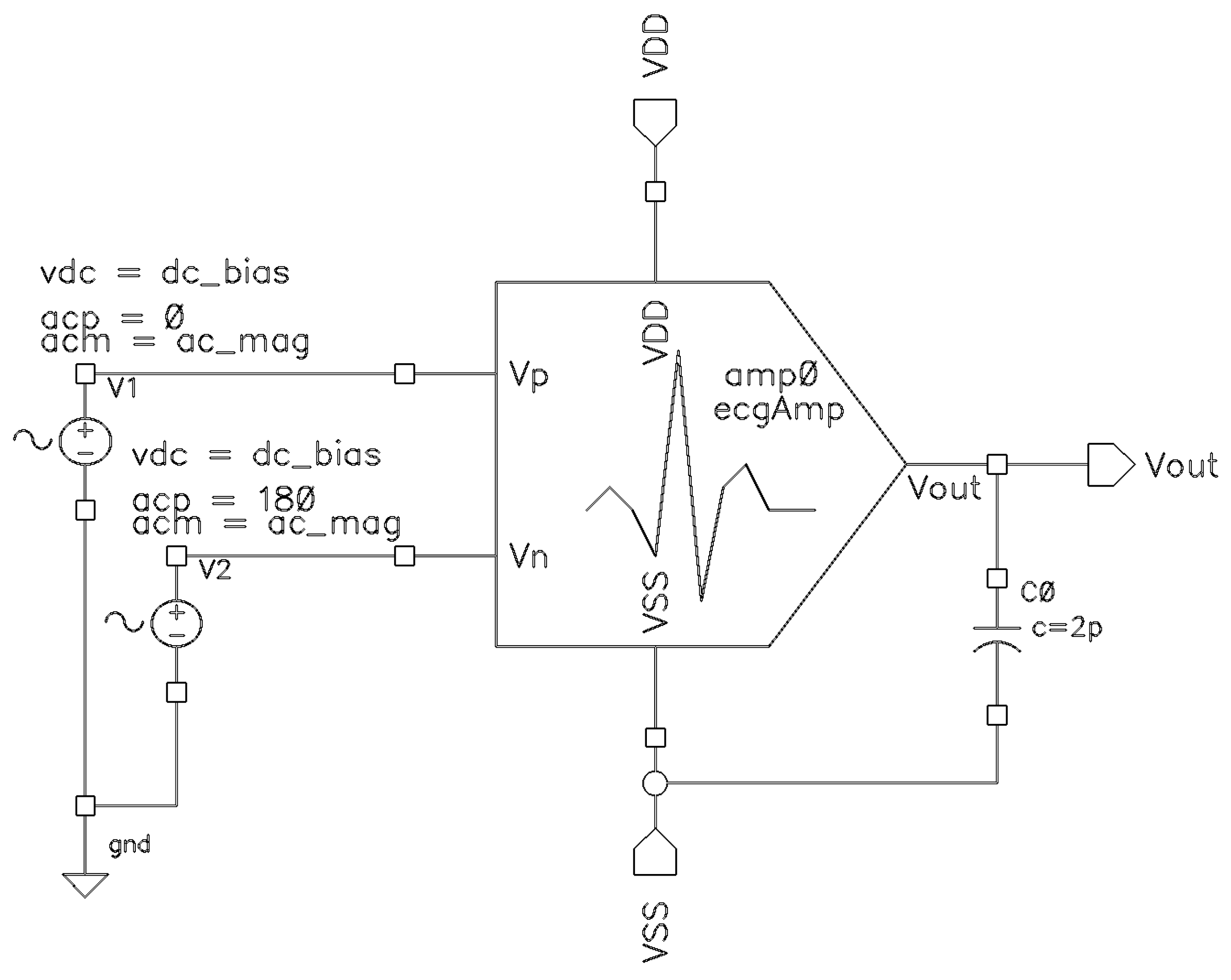

4.1. Analyses and Test-Bench

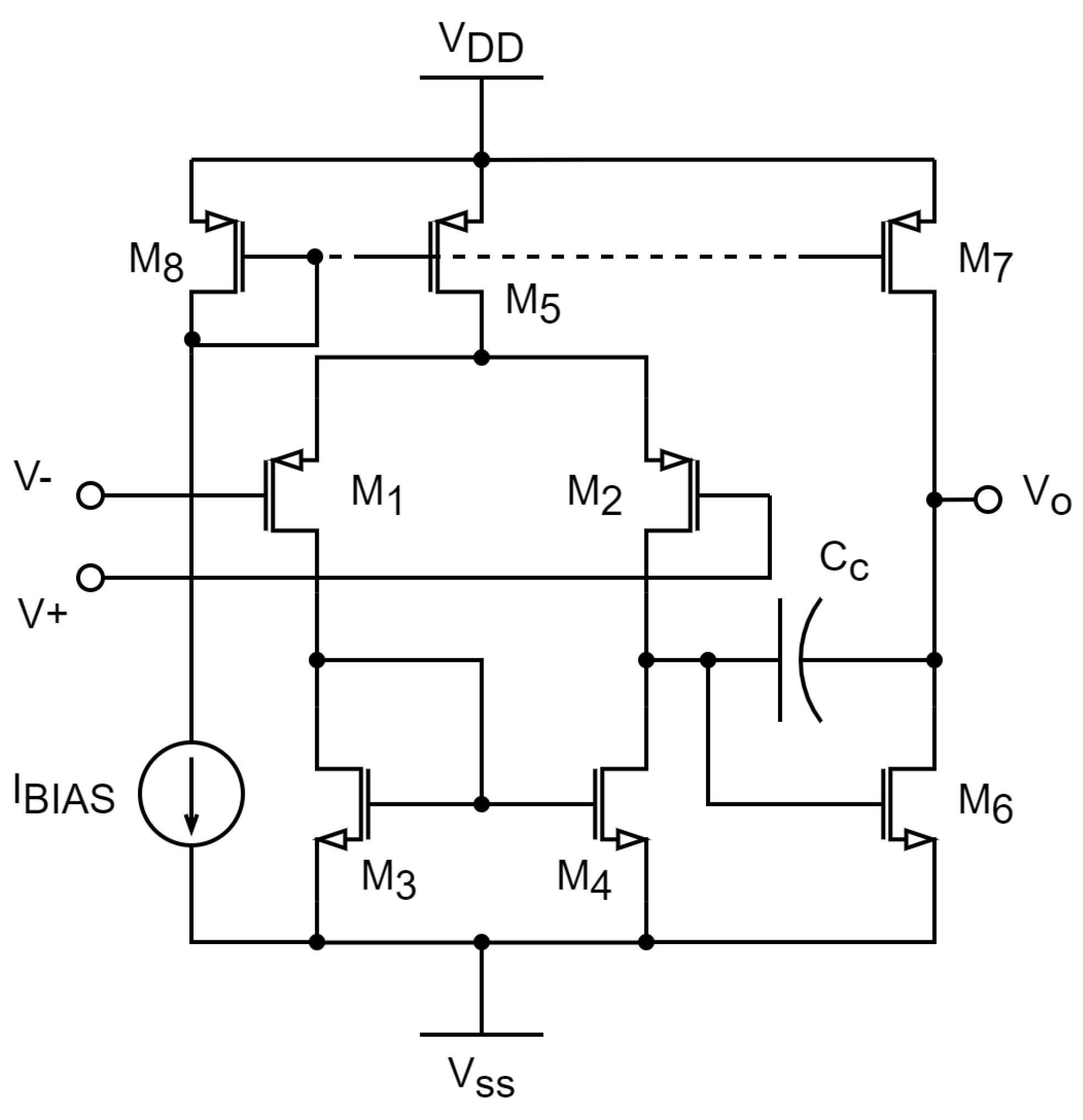

A ‘symbol’ view is given to the schematic of

Figure 3. The ‘symbol’ view contains 7 pins. The view is used to prepare a test-bench schematic (as shown in

Figure 18) for various analyses i.e. dc, ac, noise, pole-zero etc.

DC analysis: The dc analysis reveal the biasing (operating) condition of all the MOSFET devices. By this we will be able to verify whether a device is operating in cut-off or, triode or saturation region. Variable ‘vdc’ is set to common-mode voltage while ‘acm’ variable is set to 0. Proper biasing current is applied using ‘IBIAS’ variable. Using ‘Vsupply’ variable supply voltage is provided. ‘Cc’ variable sets the coupling capacitor value. These parameter values will be required for most of the analyses.

Transient analysis: Transient analysis is performed to check the circuit operation for change of inputs with time. Proper bias condition parameters are given as in stated in DC analyses. Additionally, for the two inputs (inverting, non-inverting) the ‘vsin’ source parameter ‘Amplitude’ and ‘Frequency’ are set to 1m V and 20 Hz respectively for our simulation. ‘Initial Phase for Sinusoid’ for inverting source is set to 180. The time-domain output is observed at the ‘Output’ pin.

AC analysis: With the help of ac analyses, the ac performance metrics such as gain, phase, -3dB frequency (cut-off) and unity gain bandwidth (UGBW) can be measured. Variables ‘vdc’, ‘IBIAS’, ‘Cc’ and ‘Vsupply’ are set to proper values. ‘acm’ parameter is set to 1m. The inverting input source ‘acp’ parameter is set to 180 degree. This sets the two ac inputs to 180 degree out of phase. To observe gain and phase, ‘AC Gain & Phase’ from ‘Direct plot’ can be used.

Pole-zero analysis: For ‘pz’ analysis, the positive output, negative output and input voltage parameter from ‘pz’ analysis window are set. The dc biasing is given. Then pole-zero summary can be observed or plotted using ‘Main form’.

Noise analysis: One of the key parameter of the system is input-referred noise. It can be measured using the test-bench. Proper biasing needs to be given. ‘acm’ variable must be set-up for one of the inputs. This input source generate the noise. Then in ‘Noise’ analyses form, that source must be selected as input. In ‘Direct plot’, the ‘Main form’ has the option for noise related curve generation. ‘Noise summary’ is also an excellent option for input-referred noise measurement.

CMRR analysis: A different test-bench schematic is developed for the CMRR analysis where two same OTA connections are given. One connection is similar to the test-bench shown in

Figure 18 and the other has the two inputs tied together to a ‘vdc’ source only (no ‘vsin’) to provide a common-mode voltage. CMRR expression is evaluated. Virtuoso calculator is used to create the expression. Usually a higher CMRR is desirable.

PSRR analysis: A different test-bench schematic is developed for the PSRR analysis where output is connected to inverting input via ‘iprobe’ cell from ‘analogLib’. ‘xf’ analysis is selected for the purpose.

Monte Carlo: This simulation provides the statistical report of different outcomes due to process, variation and temperature (PVT). For the schematic in

Figure 18, we choose ‘vth’ parameter to be evaluated for the variations. The ‘dc’ parameter expressions can be extracted using ‘calculator’. For this simulation, we use ‘ADE XL’. The result can be observed in histograms.

4.2. Schematic Level Simulation

4.2.1. Operational Trans-Conductance Amplifier (OTA)

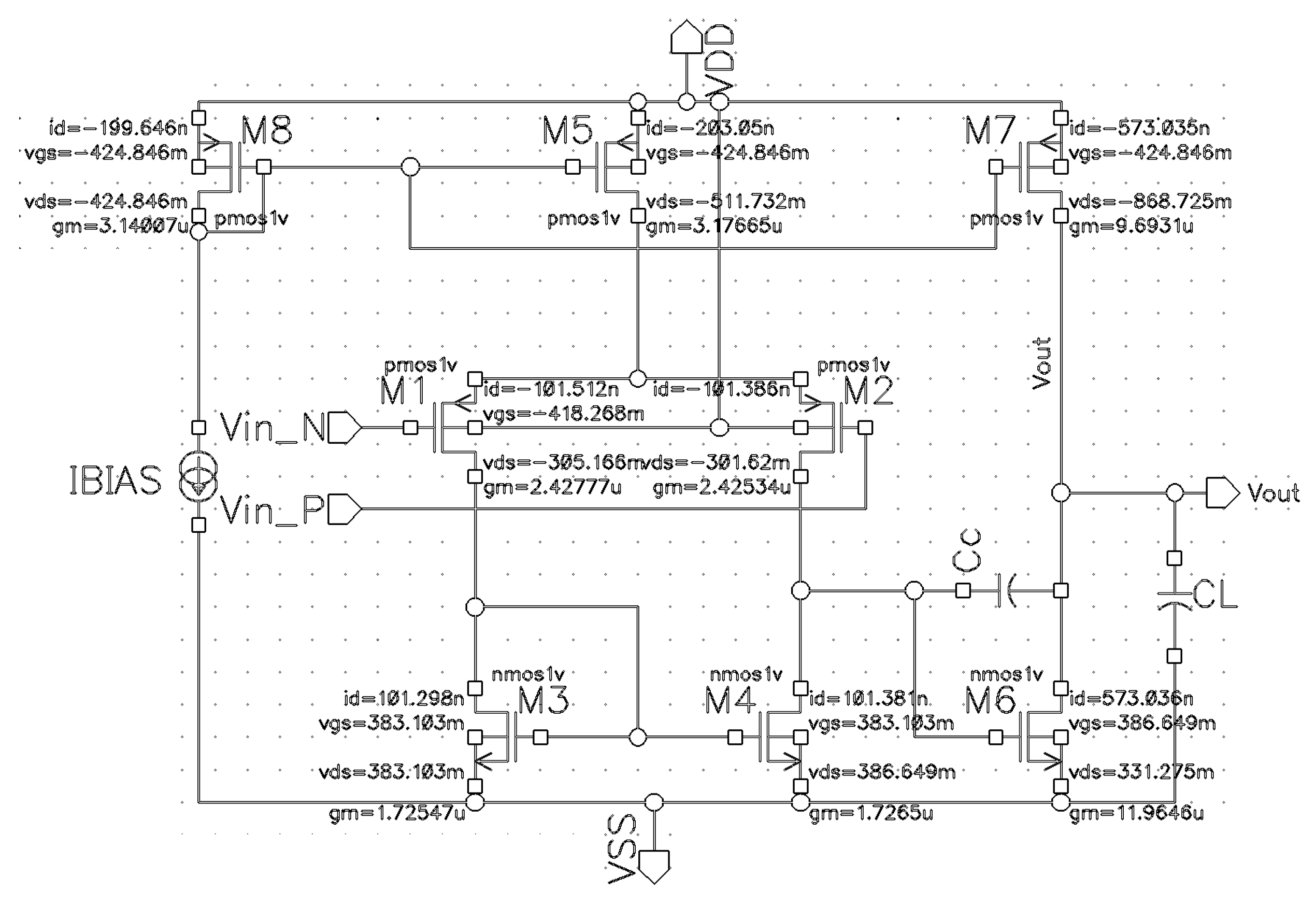

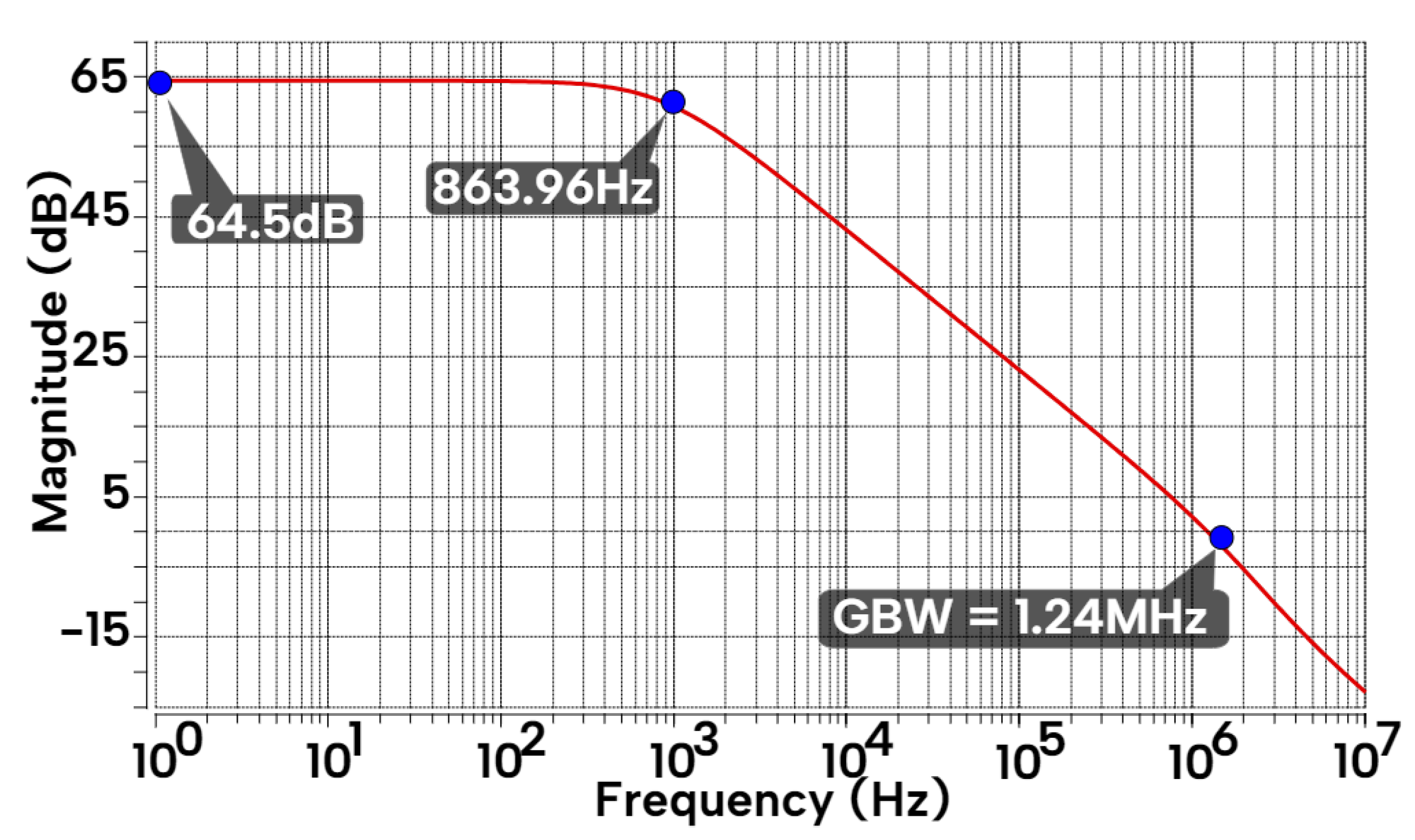

The designed OTA is simulated using ‘spectre’ using TSMC’s 45nm pdk technology with supply voltage of ±0.6 V. The dc analysis confirms the operating condition of all the MOSFET device in the required inversion/saturation region.

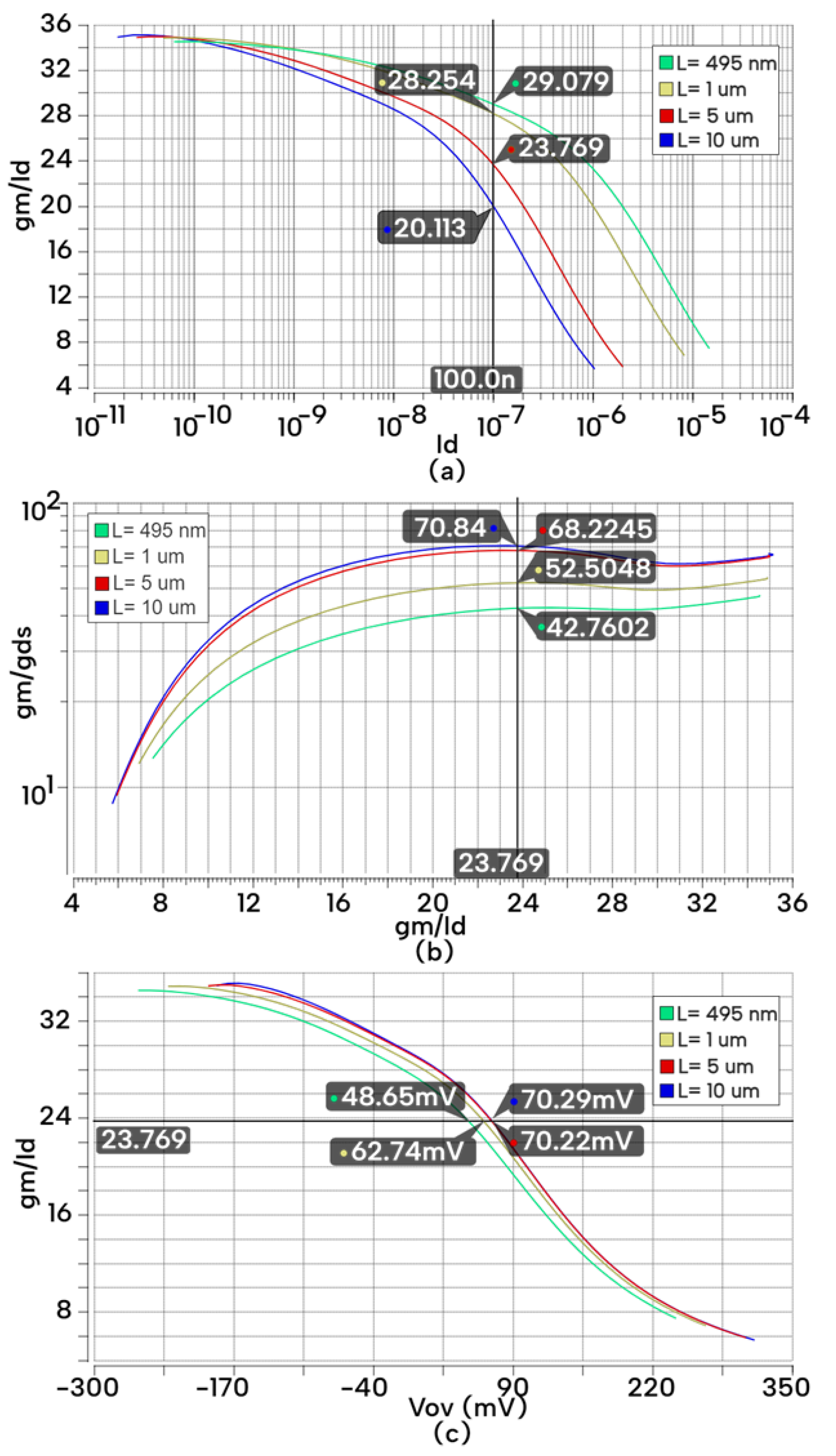

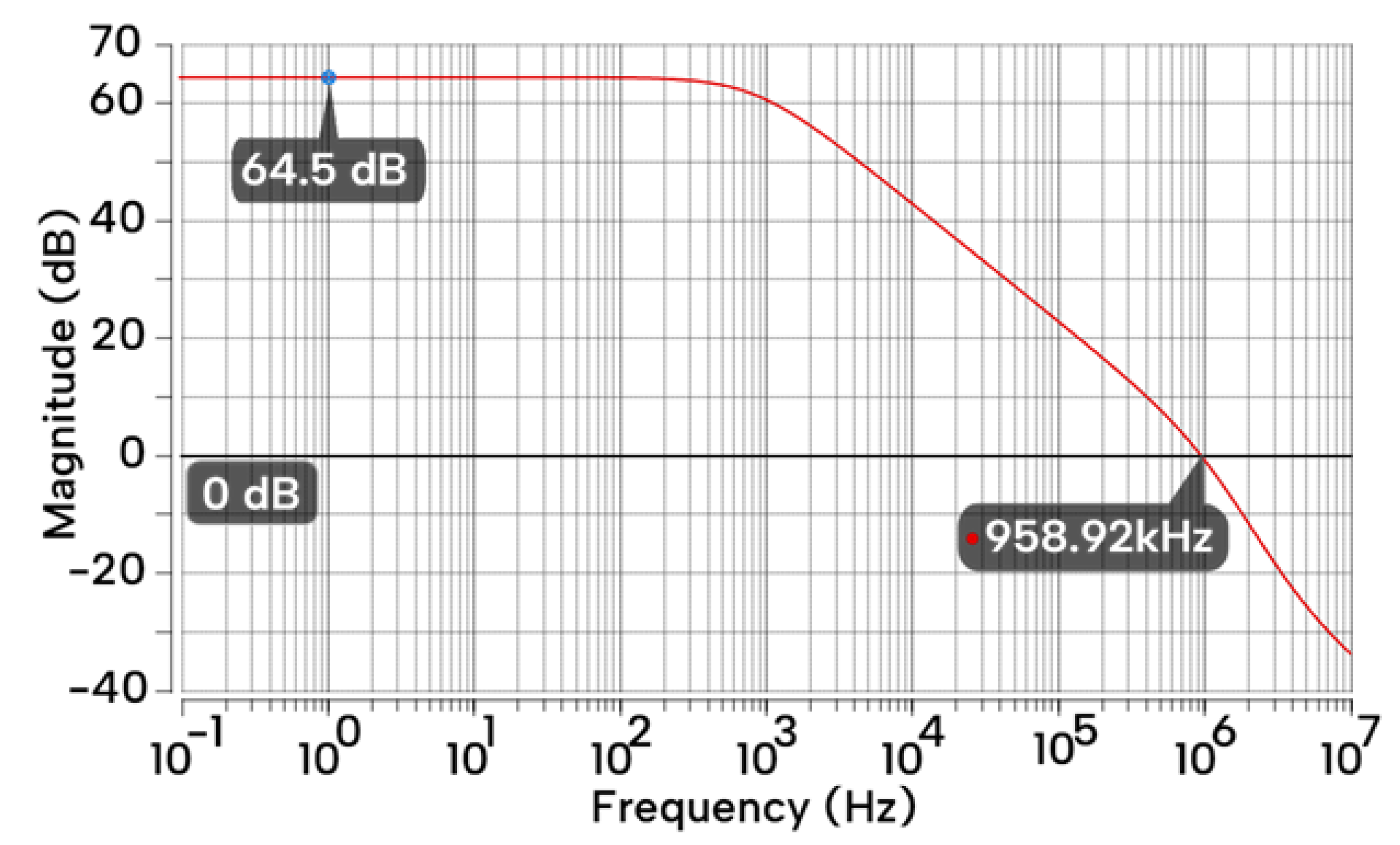

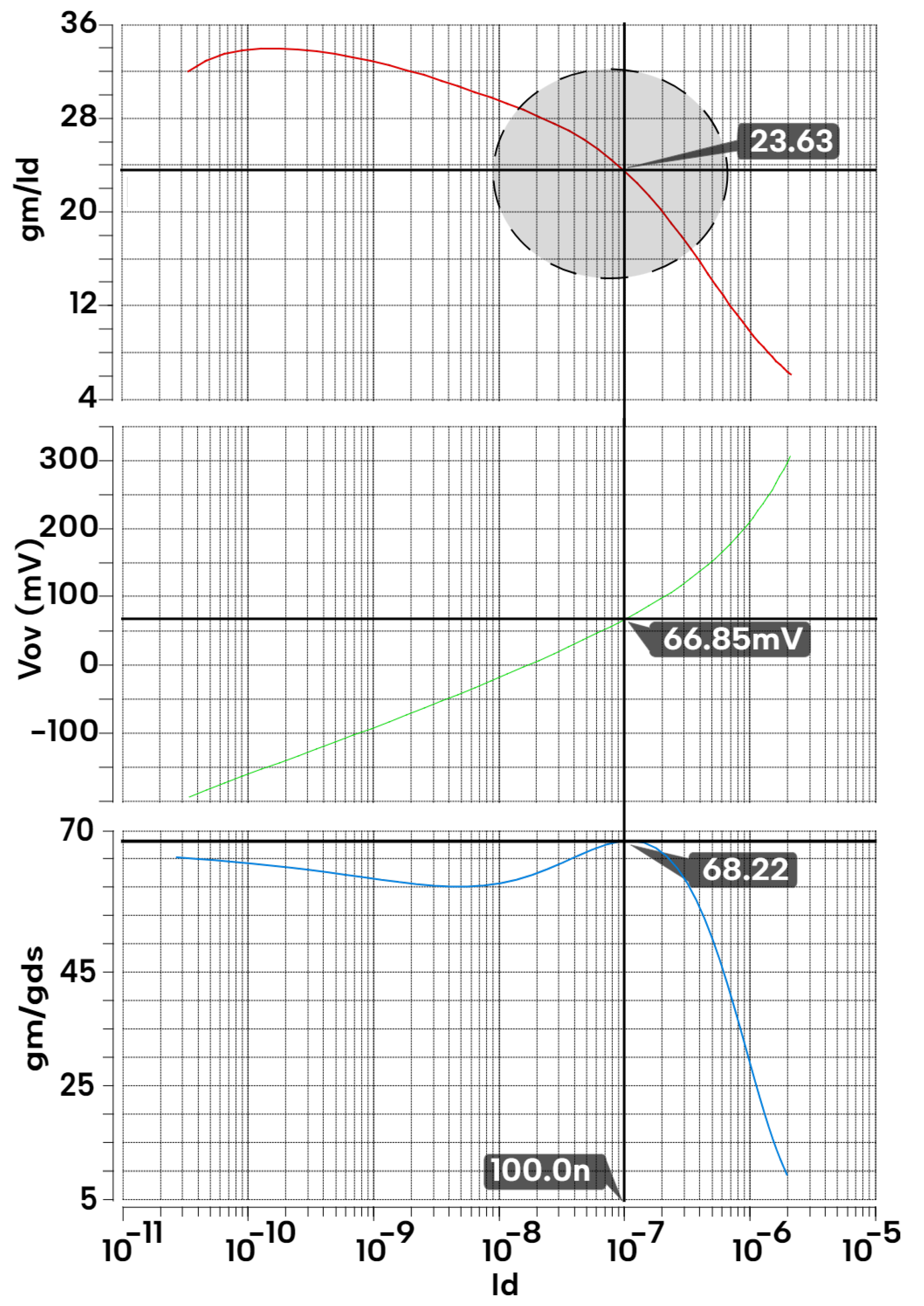

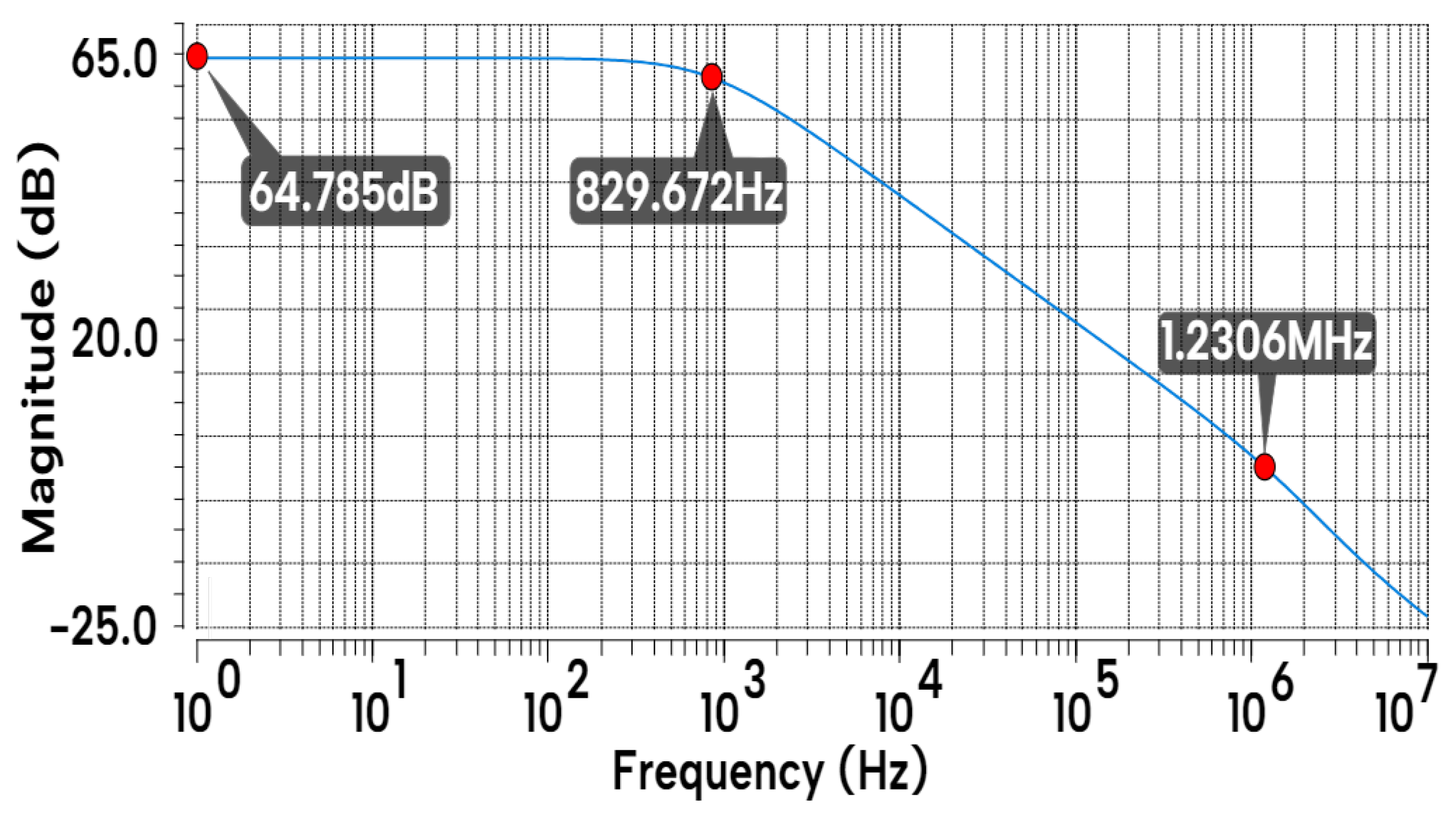

Figure 19 shows the magnitude response of the OTA which shows that the low frequency (dc) gain is 64.5 dB or 1679 (65.69 at the 1st stage and 25.56 at the 2nd stage), -3dB frequency (cut-off) is at 864 Hz and a unity gain-bandwidth is 1.24 MHz. The choice of ‘moderate inversion’ region for the driver MOSFET’s (M1, M2, M6) with a higher

than in ‘strong inversion’ region assures the high gain. The 1st stage gain is very close to the chosen

value (68.22 in

Figure 14).

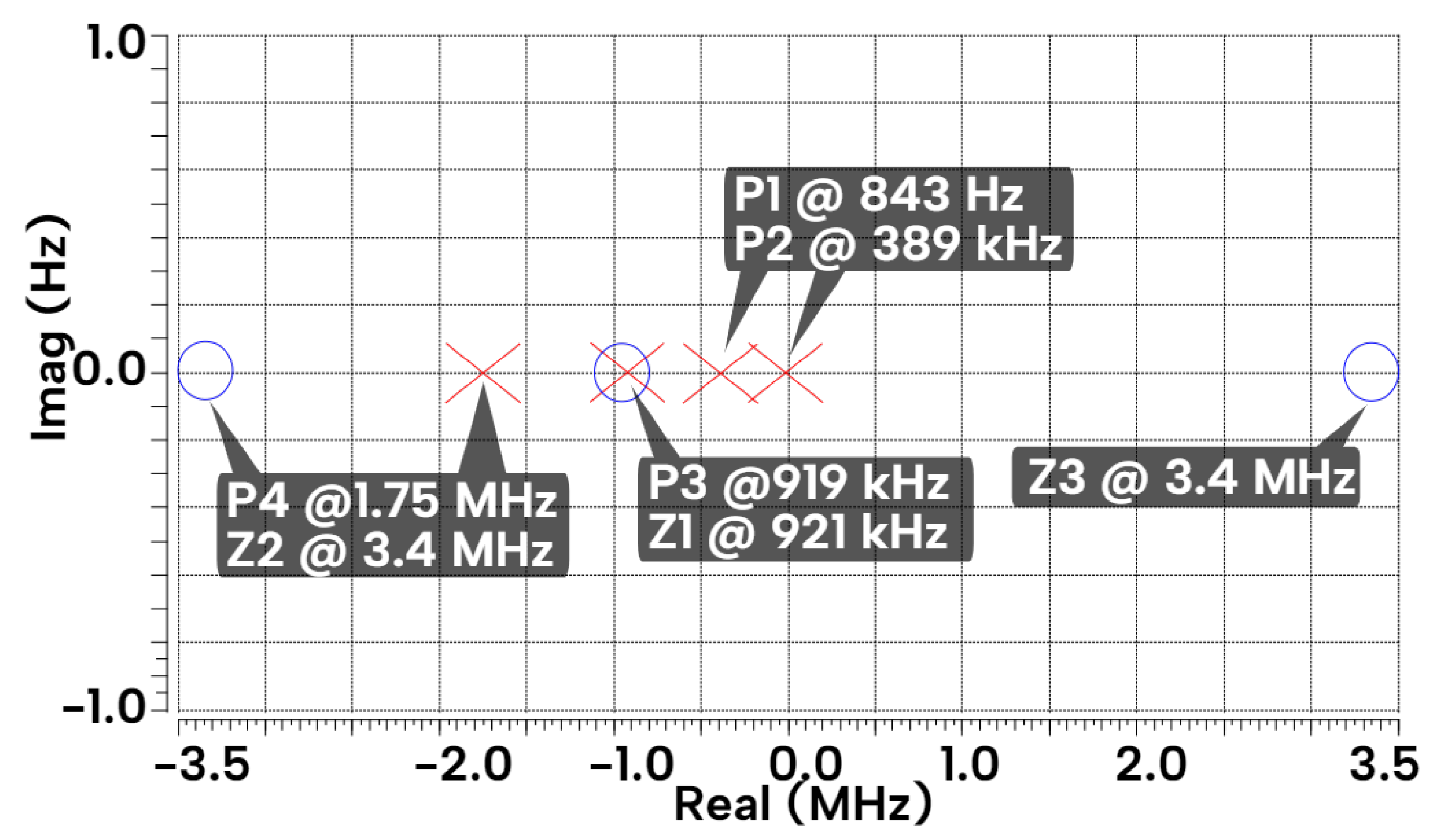

From pole-zero analysis presented in

Figure 20, the dominant pole approximately at 843 Hz sets the -3dB frequency. In total 4 poles and 3 zeros are observed. No right half poles but one right half zero is observed. The poles are from the input (P4), mirror (P3), first stage output (P2) and the second stage output (P1).

From the pole-zero diagram, P3 and Z1 nullify each other. The gain starts to decay at frequency 843 Hz (P1) which is further enhanced by the pole P2 at 389 KHz. The gain reaches 0 dB at 1.24 MHz. The pole P4 further increases the negative slope of gain at 1.75 MHz. Taking Bode’s approximation into account, the 3 poles before 3.4 MHz create a slope of -60 dB/decade where the two zeros increase the slope to -20 dB/decade. The system shows a phase margin of an acceptable 34 degree.

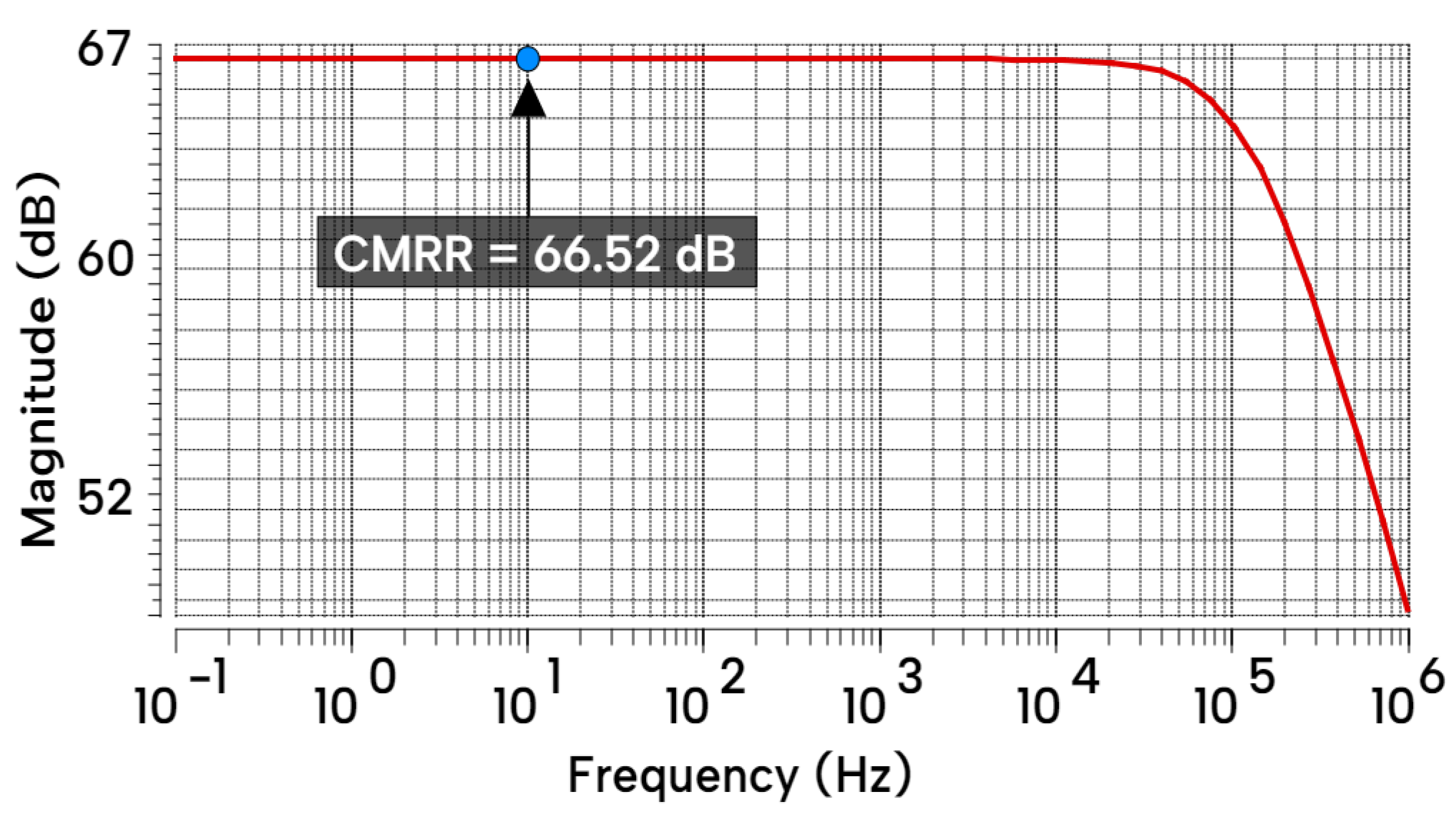

A common mode rejection ratio (CMRR) of 66.52 dB over a bandwidth of more than 10 kHz is observed in

Figure 21 which confirms an attenuation of more than 1000 times for the common noise coming through the two inputs. This is due to the high differential gain from high

value. The low mismatch in

values of

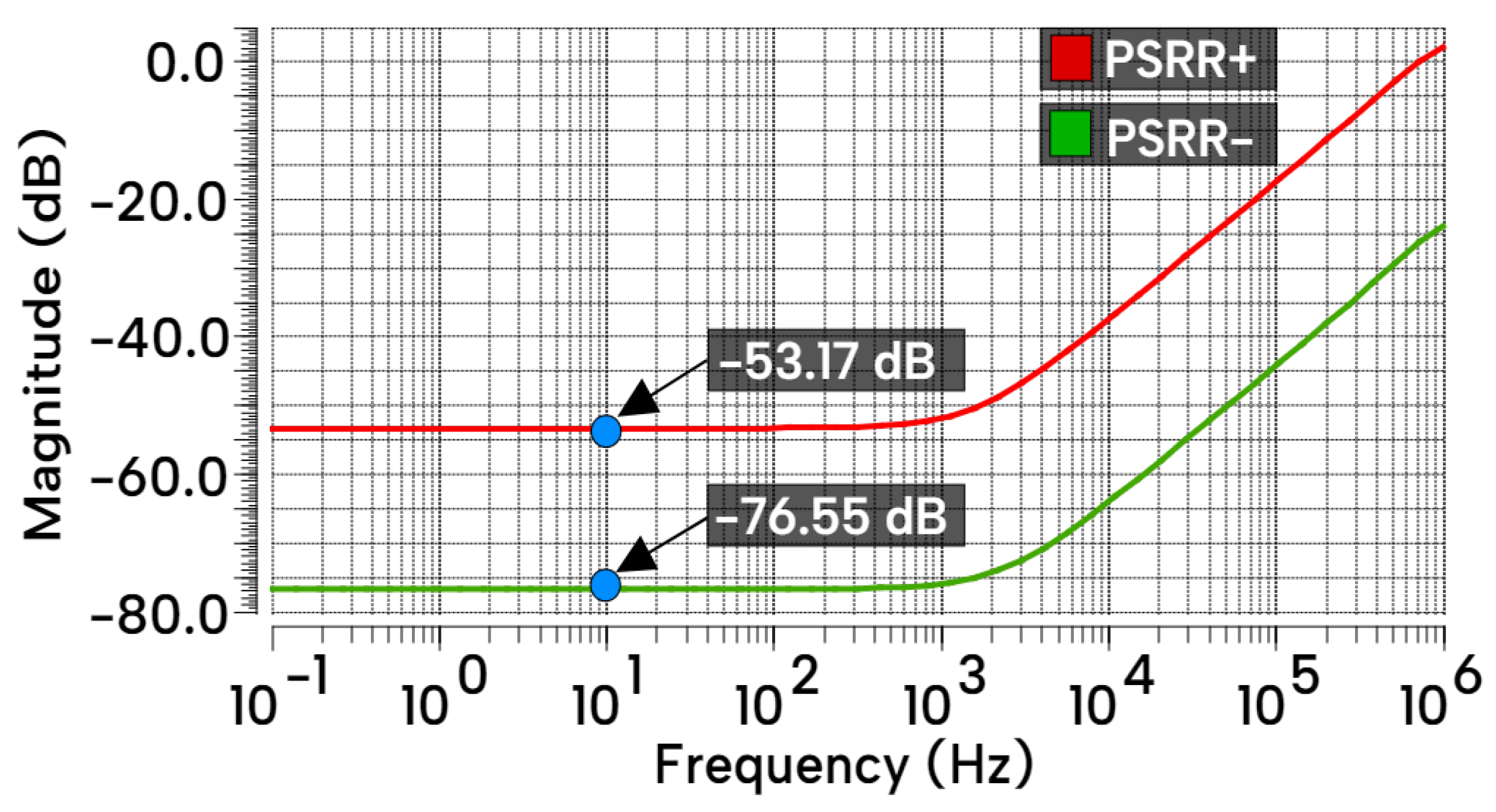

also contributes to this findings. Power Supply rejection ratio (PSRR) of -53.17 and -76.55 dB within 1 kHz bandwidth for positive and negative sources noise are observed in

Figure 22. If any noise appear at the power supply, the OTA will attenuate that noise by at least 456 times.

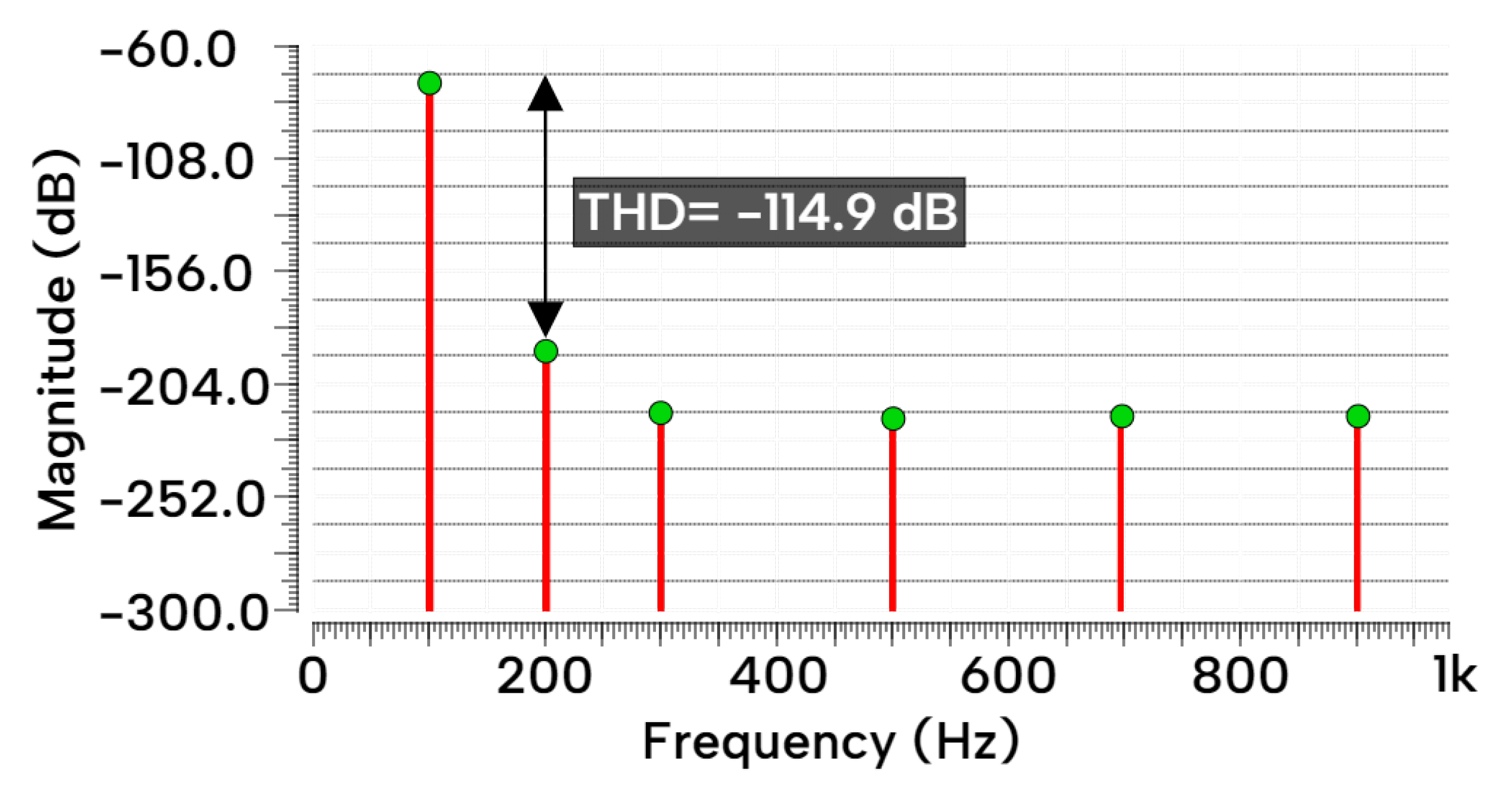

The transient analysis with the given test-bench can be used utilized for THD calculation. This can be done from ‘Virtuoso Visualization and Analysis’ (also known as ‘ViVA’ window) in ‘Measurements’ from Spectrum.

Figure 23 displays a Total Harmonic Distortion (THD) of -114.9 dB (less than 1%) for 400

V peak to peak (p-p) signal at 100 Hz. The THD here is a 2

nd order harmonic. Due to differential input, rest of the even order harmonics are nullified.

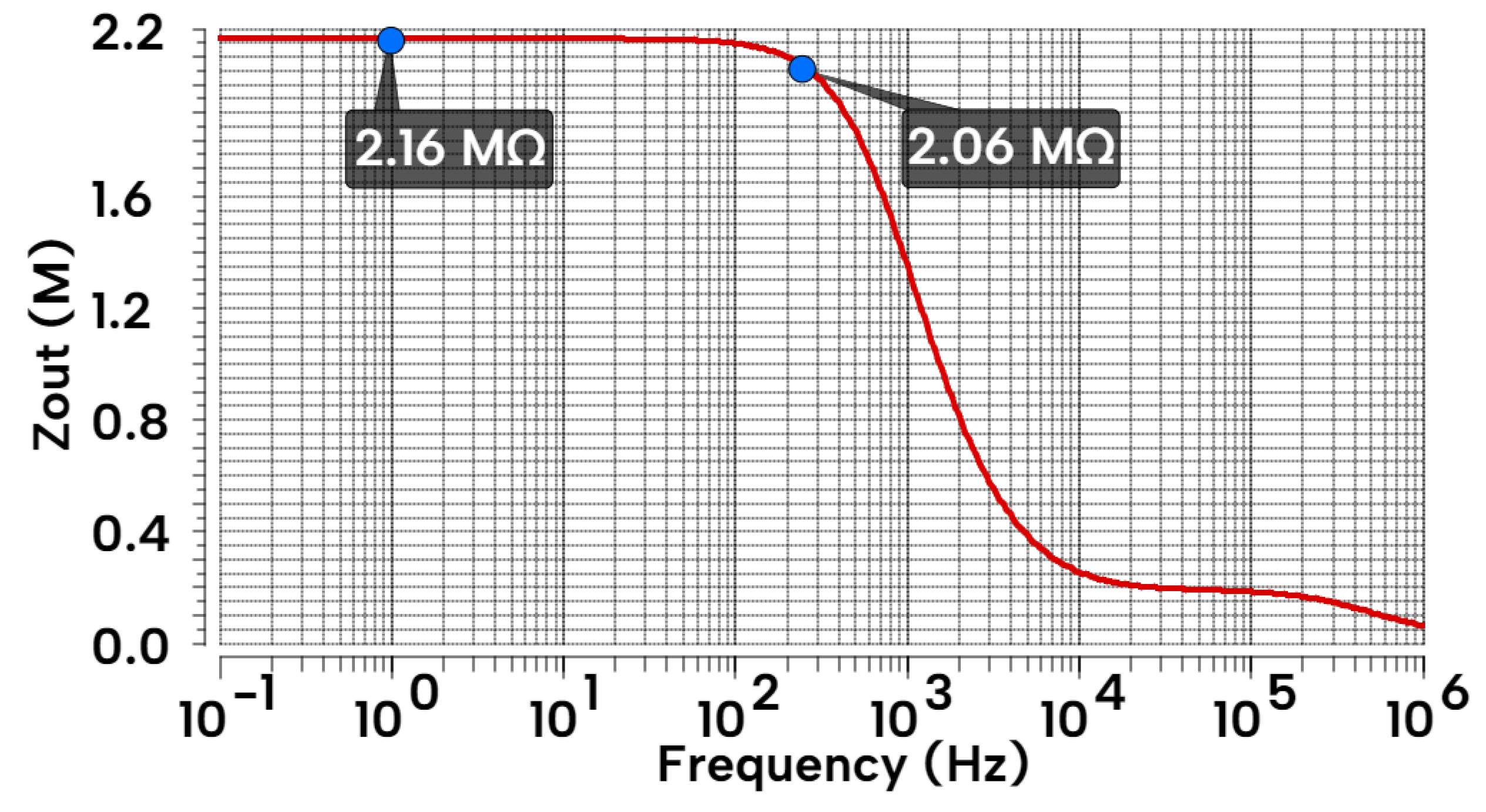

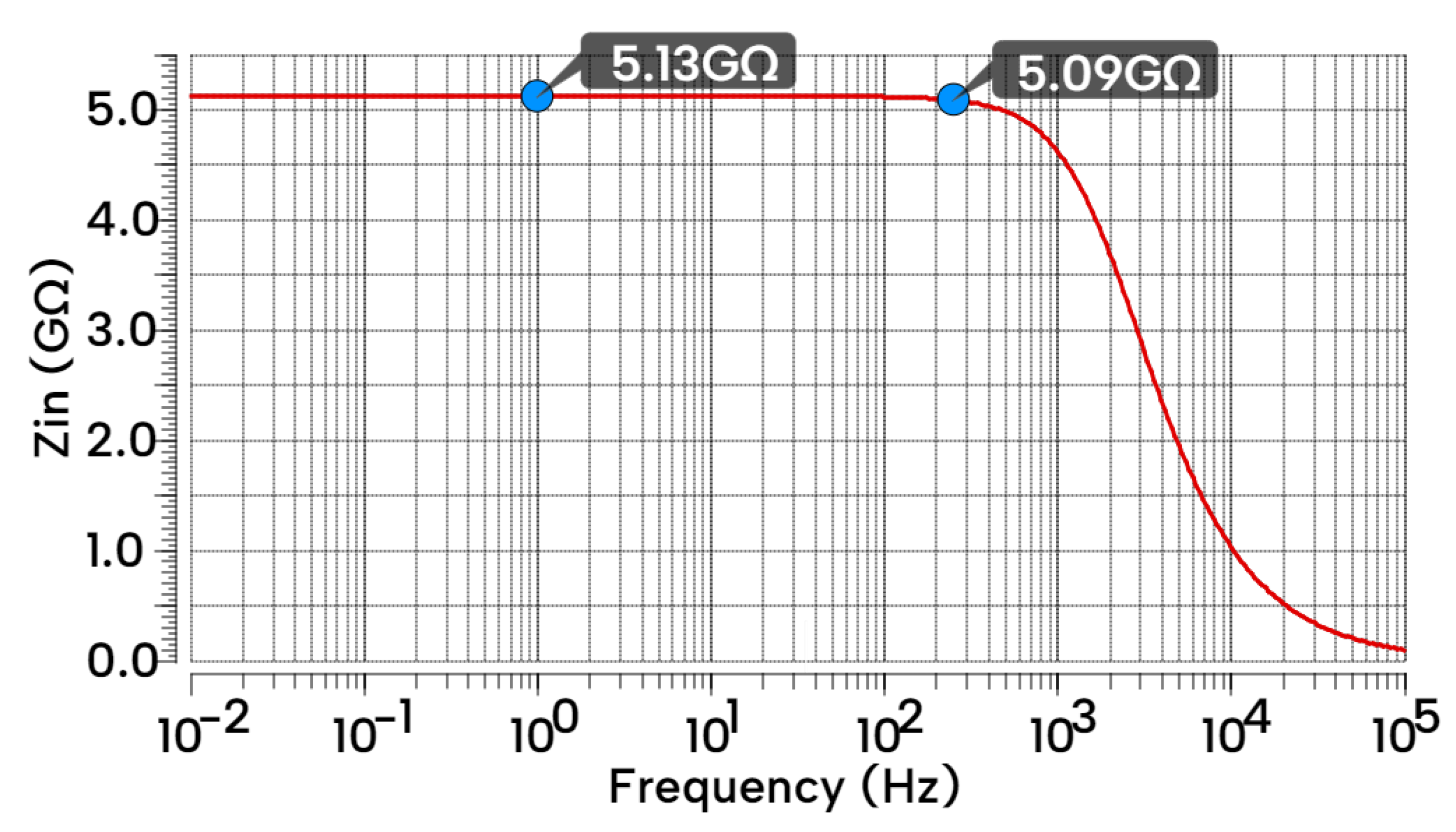

The OTA gives out an output impedance of 2.06 M

and a large input impedance of 5.13 G

inside the frequency of interest, as seen from

Figure 24 and

Figure 25. For output impedance measurement, a voltage source is added to OTA’s output node. Current is measured at the same node while frequency is varied.

Table 7 summarizes a performance comparison of the proposed OTA with the state-of-the art OTAs. Considering the lowest technology node, the proposed OTA gives the best gain and PSRR, and a comparable power, CMRR, THD, IRN and Zin.

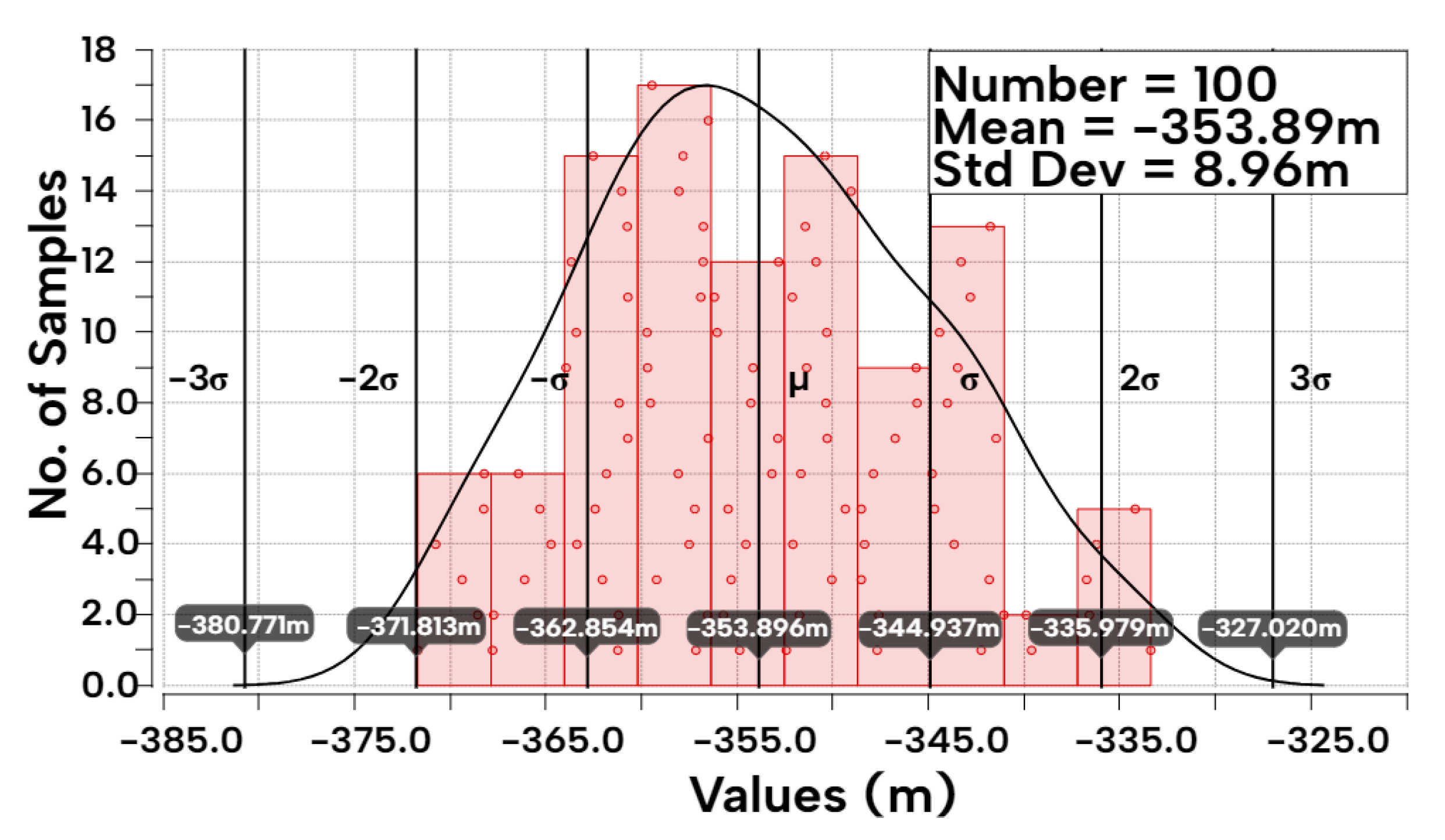

The process variation of the technology can change the performance of the OPAMP[

55], which in turn can change the response of the circuit.

Figure 26 illustrates the Monte Carlo histograms at T=27

oC for 100 points of threshold voltage parameter. A deviation of nearly ±20 mV is observed from the mean value. The OTA designed in this work has a 72.3 mV difference in gate to source voltage. This ensures appropriate region operation of the MOSFETs. The designers may opt for PVT simulations as it reveals biasing related challenges.

4.2.2. ECG Acquisition System

All the filters and instrumentation amplifier are simulated separately before forming the whole ECG system. Various performance parameters, figures are obtained via dc, ac, transient, xf, noise analyses using spectre simulator.

Table 8 summarizes the various performance parameters of the High Pass filter (HPF), Notch filter and Low Pass Filter (LPF) designed for the ECG system. All the individual parameter is within the acceptable value mentioned in [

35]. As the first block is an instrumentation amplifier and provides gain, the input-referred noise is reduced for the whole system.

Figure 27 shows the schematic used as the test-bench for the ecg acquisition system. Supply voltages (VDD, VSS) are given as ‘stimuli’.

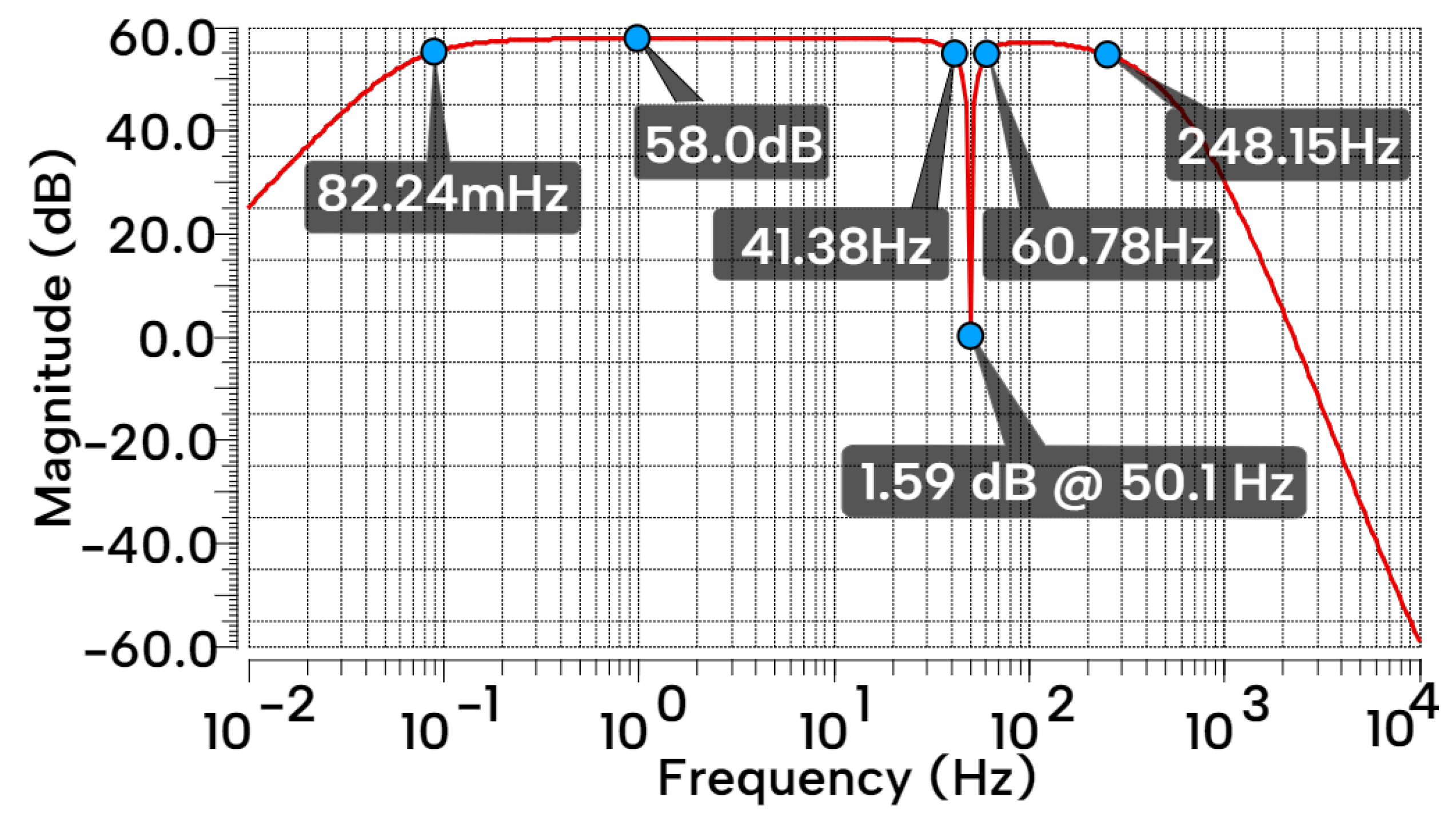

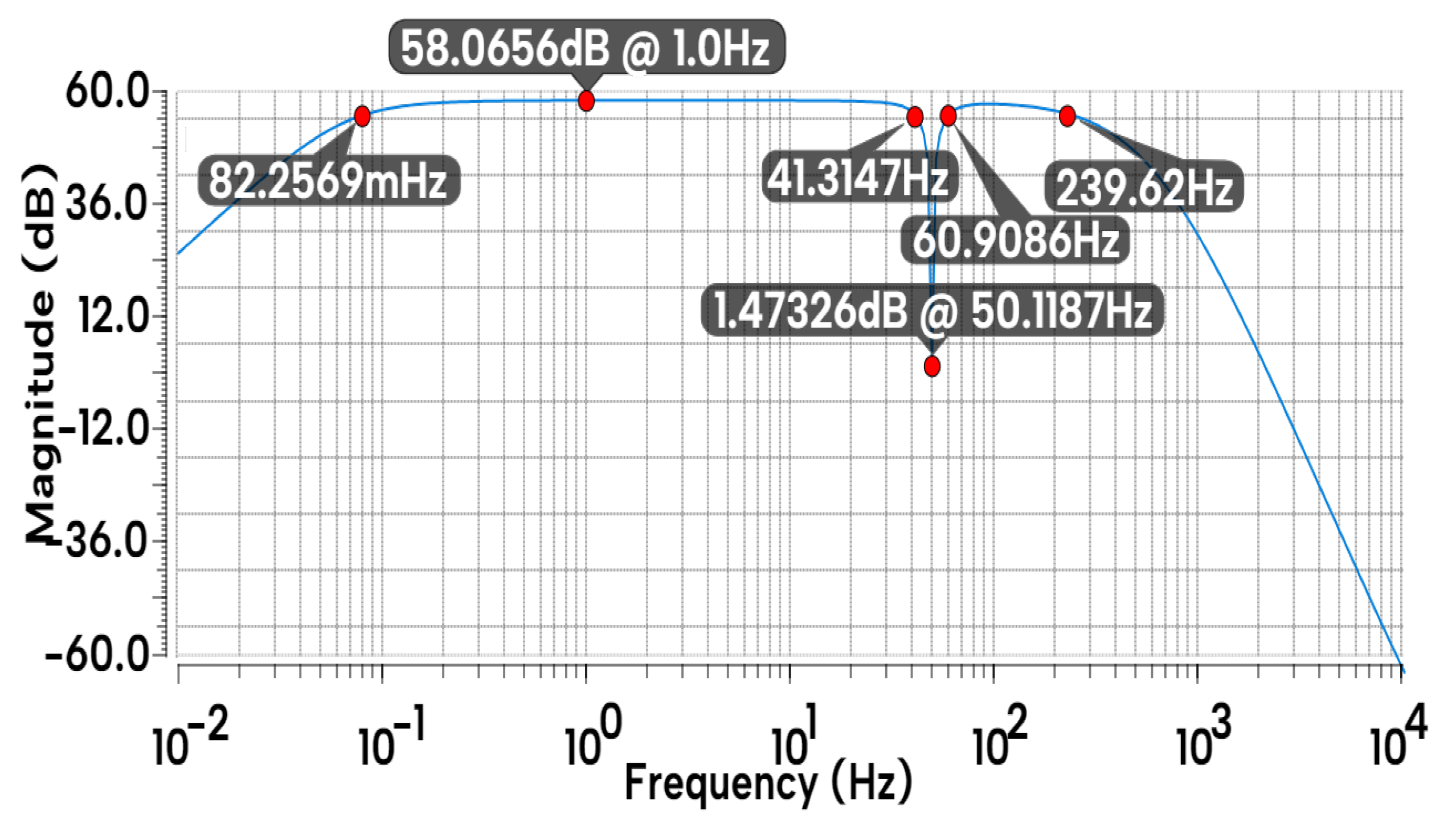

Figure 28 shows the magnitude response of the ECG system. The pass-band gain of the system is 58 dB. The lower cut-off is at 82.24 mHz resulting from the 2nd order HPF poles and the higher cut-off is at 248.15 Hz which is due to the poles of 5th order LPF. Cut-off’s of notch filter are at 41.38 Hz and 60.78 Hz. The notch depth is 56.4 dB at 50.1 Hz. These results confirm that the ECG designed in this work can function within the specified bandwidth of the ECG signals, where the 50 Hz power line frequency is selectively notched out.

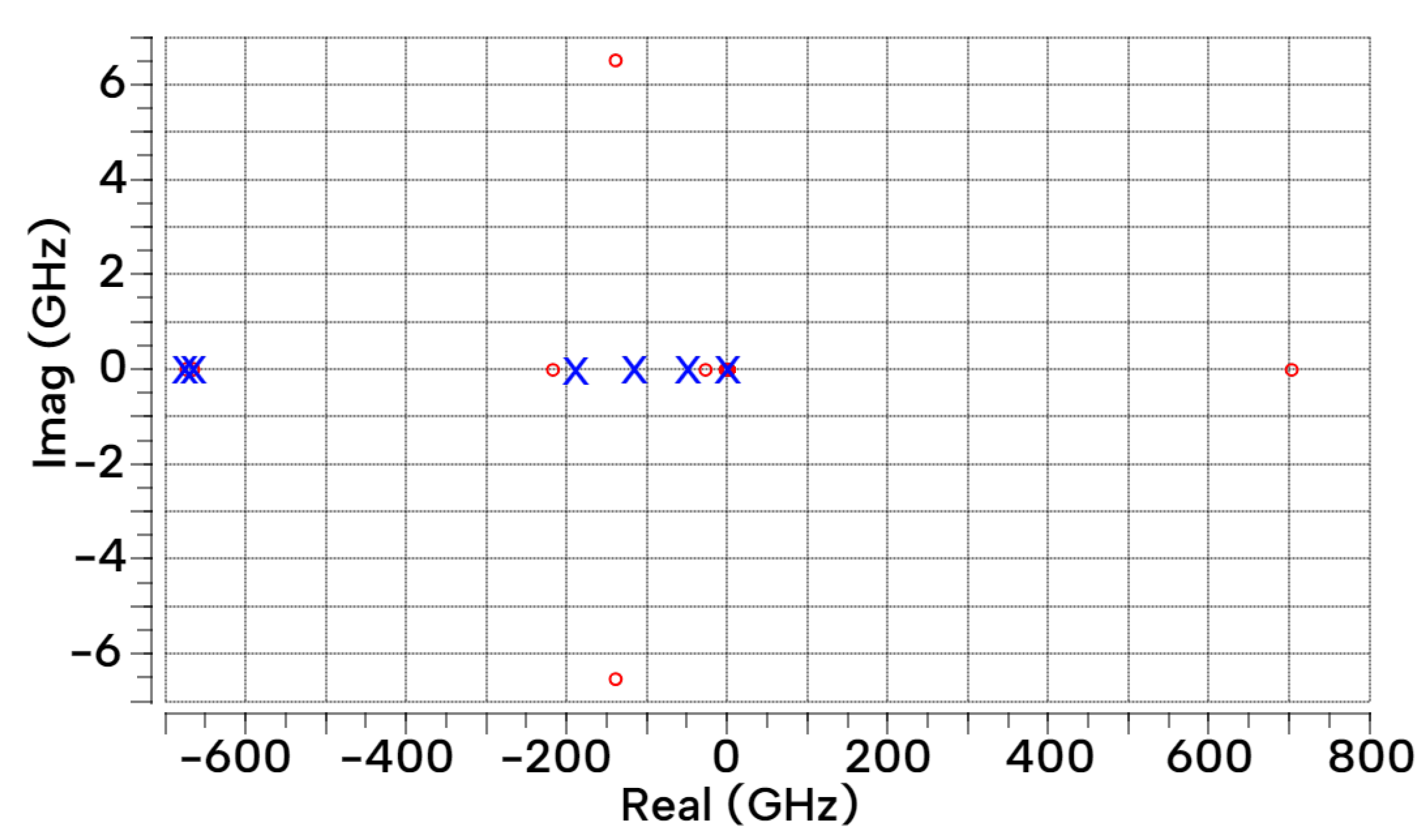

Figure 29 verifies the stability performance of the whole system through a pole-zero map. All the poles are situated inside the left half plane (LHP), while few zeros are located at the right half plane (RHP). While Right half plane poles makes the system unstable but zeros don’t. Right half plane zeros provides a +20dB/decade gain and -90 degree phase change. This makes it difficult to achieve the desired phase margin, as the gain will increase at that frequency but phase decreases which will reduce the phase margin (total phase change from 0 or 180 degree till 0 dB gain). Since the proposed system reaches 0dB gain near 1 kHz frequency, the effects of the RHP zeros becomes insignificant.

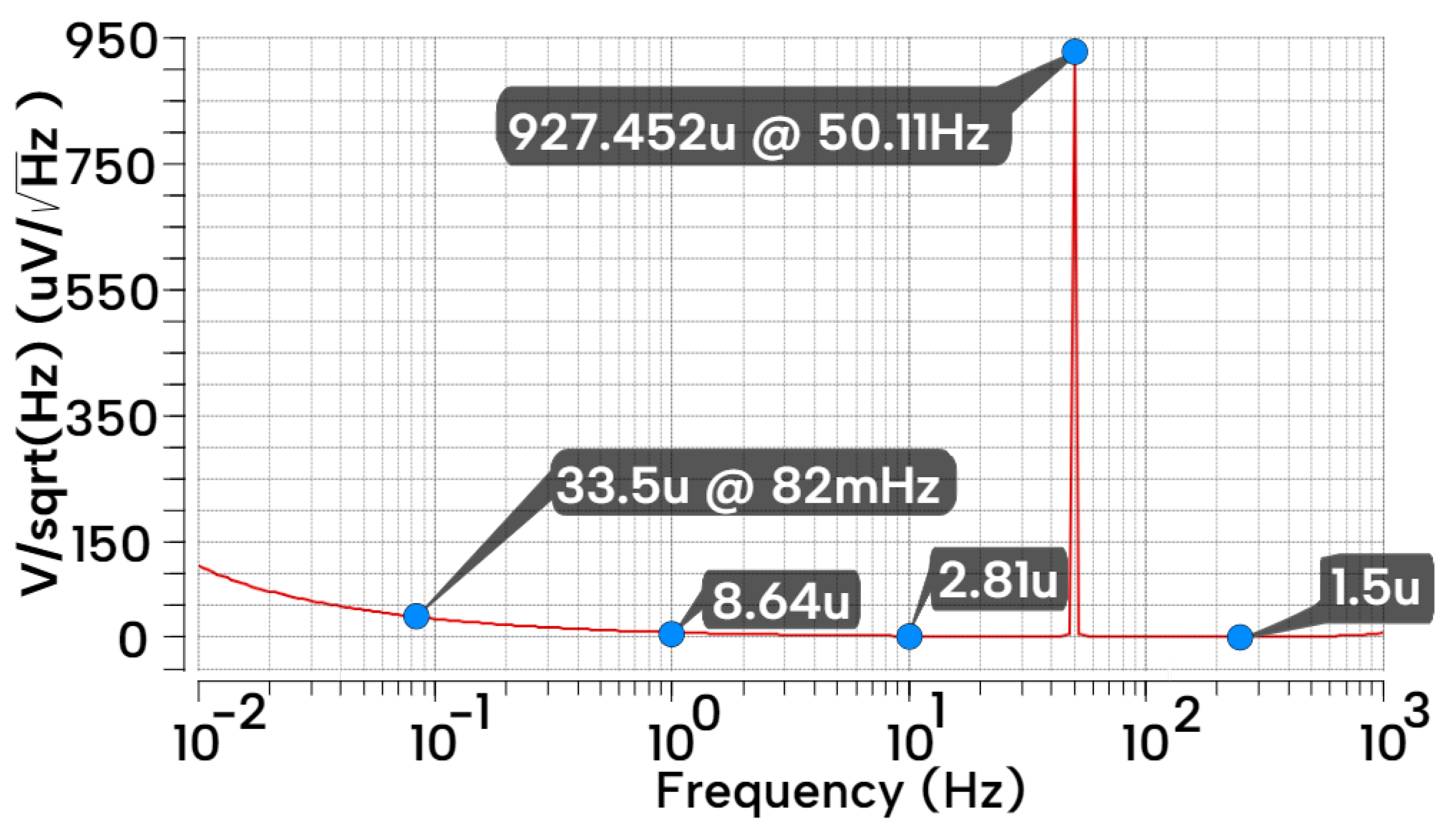

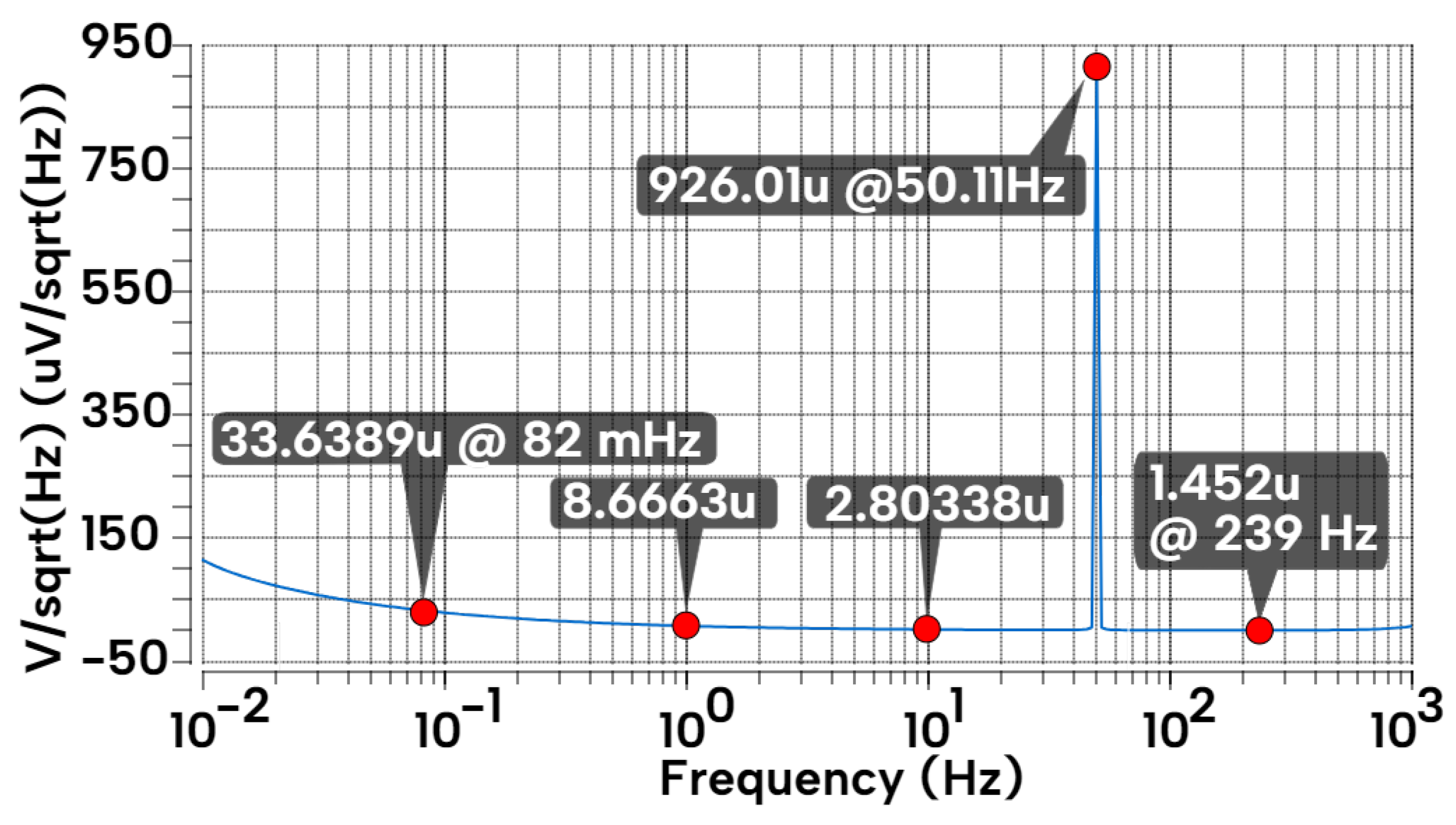

The input referred noise is demonstrated in

Figure 30. Flicker noise is typically a low frequency noise and is high at low frequencies. It decreases with the increase in frequency. From 0.01 to 0.1 Hz, the noise decreases which is a typical behaviour of flicker noise. The notch filter attenuates signal by nearly 56 dB at 50.1 Hz. This will make the signal weak but strong noise at that frequency. Similar behaviour was observed from the figure which shows a large spike of 927.452u input referred noise at 50.11 Hz.

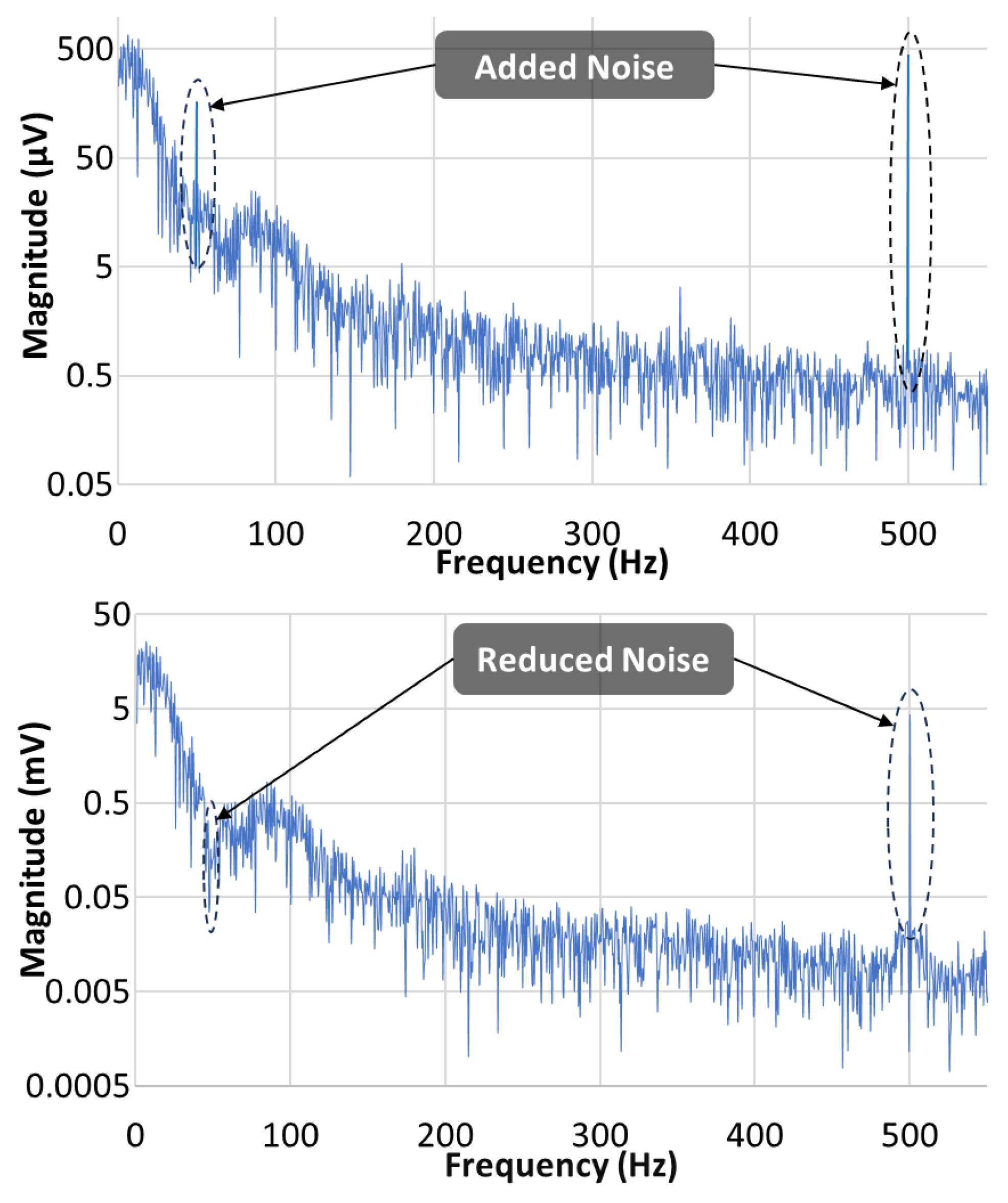

Using MIT-BIH data-set, an ECG signal[

56] with added noise at 50 Hz and 500 Hz is fed to ECG system. The overall gain of the system is set to 46 dB by changing the value of variable resistances for gain control. The ECG signal voltage spectrum is shown in

Figure 31 (Left) with externally added noise at 50 and 500 Hz. In typical ECG signal spectrum, most of the considerable signal is within 35 Hz range. This can be confirmed by the magnitude from 0 to 35 Hz, which is ranging in between 25-500 µV. The output voltage spectrum of the ECG system is shown in

Figure 31 (Right), where it can be seen that noise at 50 Hz is not visible and noise at 500 Hz is reduced while the magnitude of the signal is increased to a maximum value of nearly 26 mV.

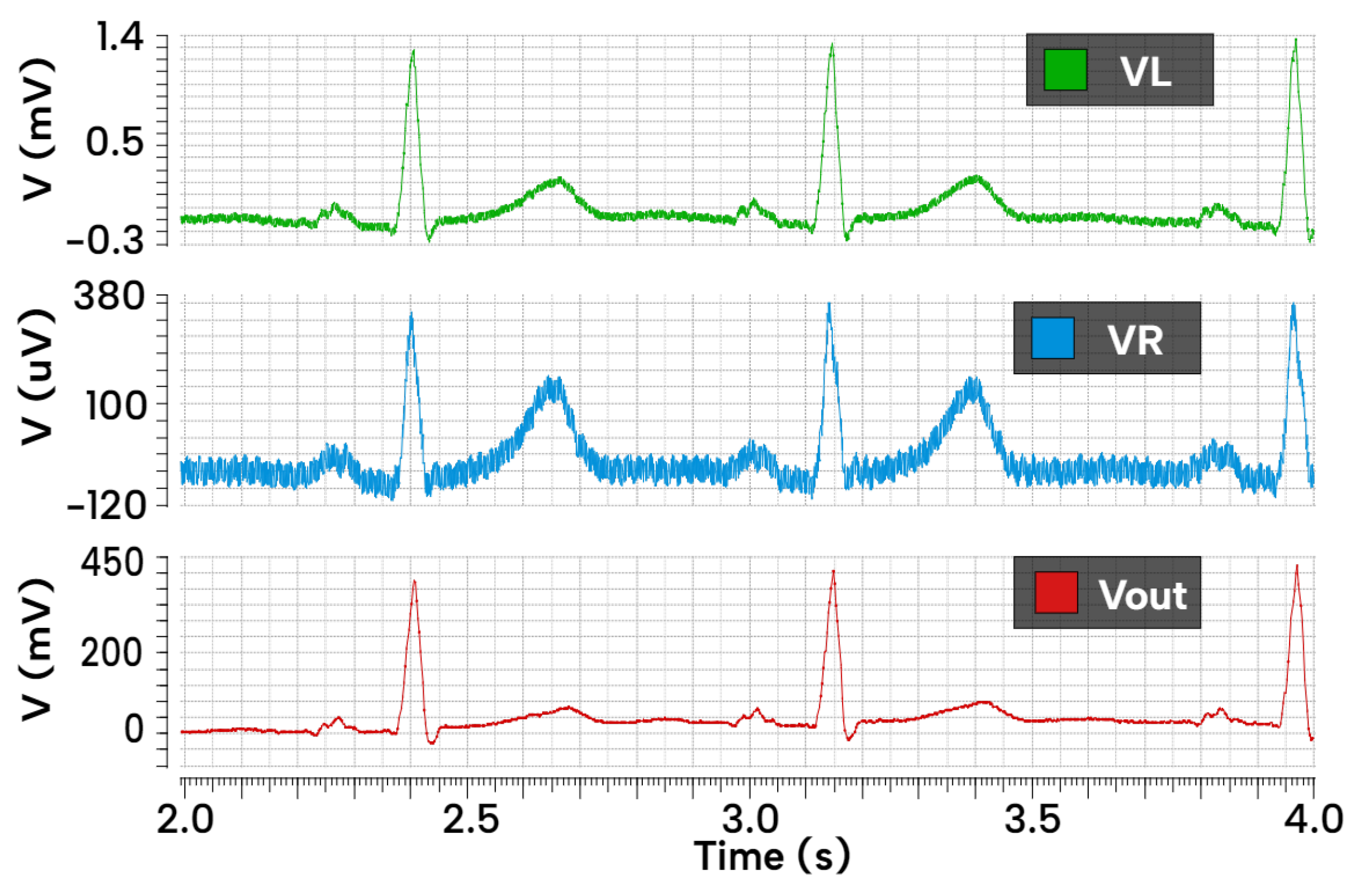

Figure 32 depicts the time domain signals, where VL (green) and VR (blue) are input signals from electrodes of left arm and right arm respectively. Vout (red) is the output signal from the ECG system. As demonstrated, the noise at the output signal is minimized and can be understood by comparing the haziness of the VL, VR and Vout signals.

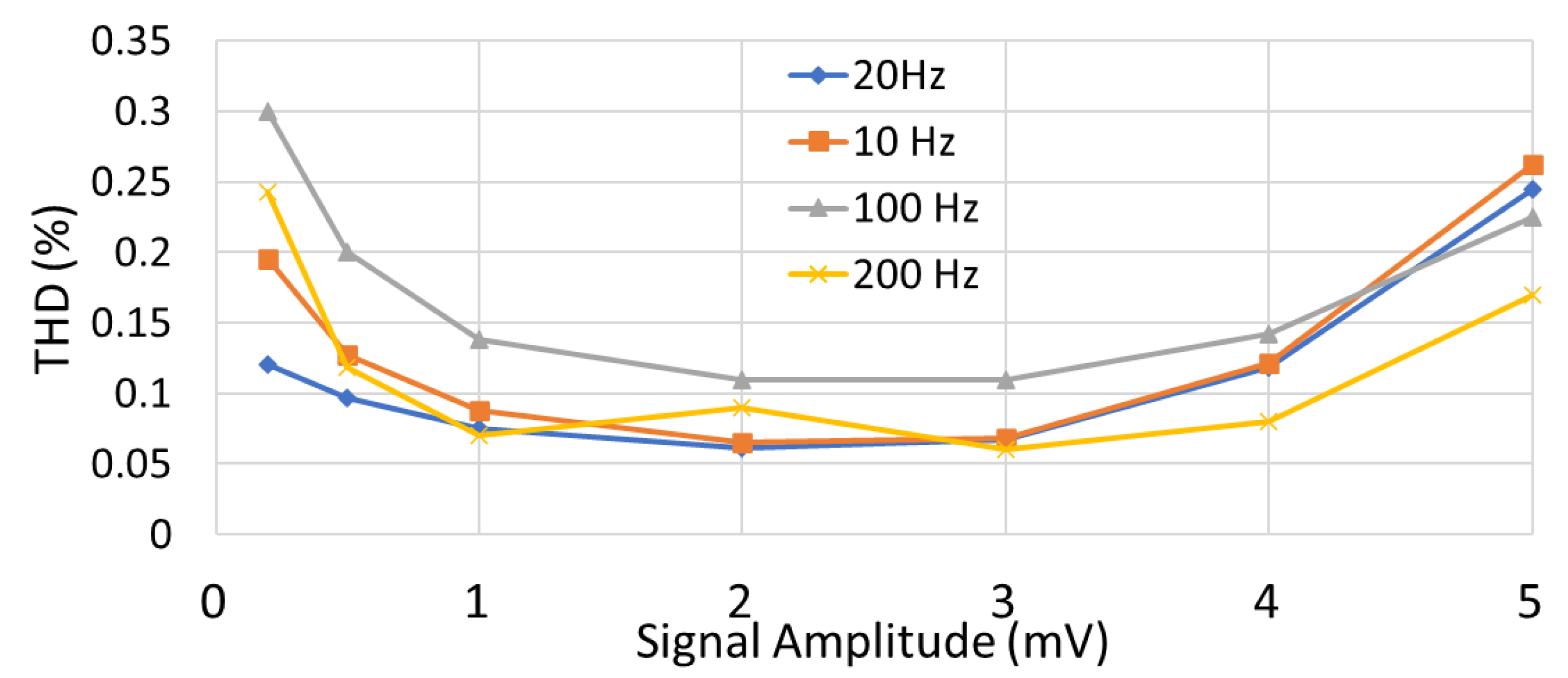

THD values in

Figure 33 represents system’s performance within the range. All THD values are less than - 50 dB. For the ECG signal range (0.2mV - 5mV), the designed system provides good linearity and providing 158 - 797 times larger signal at the output. It is worthy of mentioning that the dc analysis of the whole system has been done to ensure appropriate region of operation of all the transistors.

4.3. Post Layout Simulation

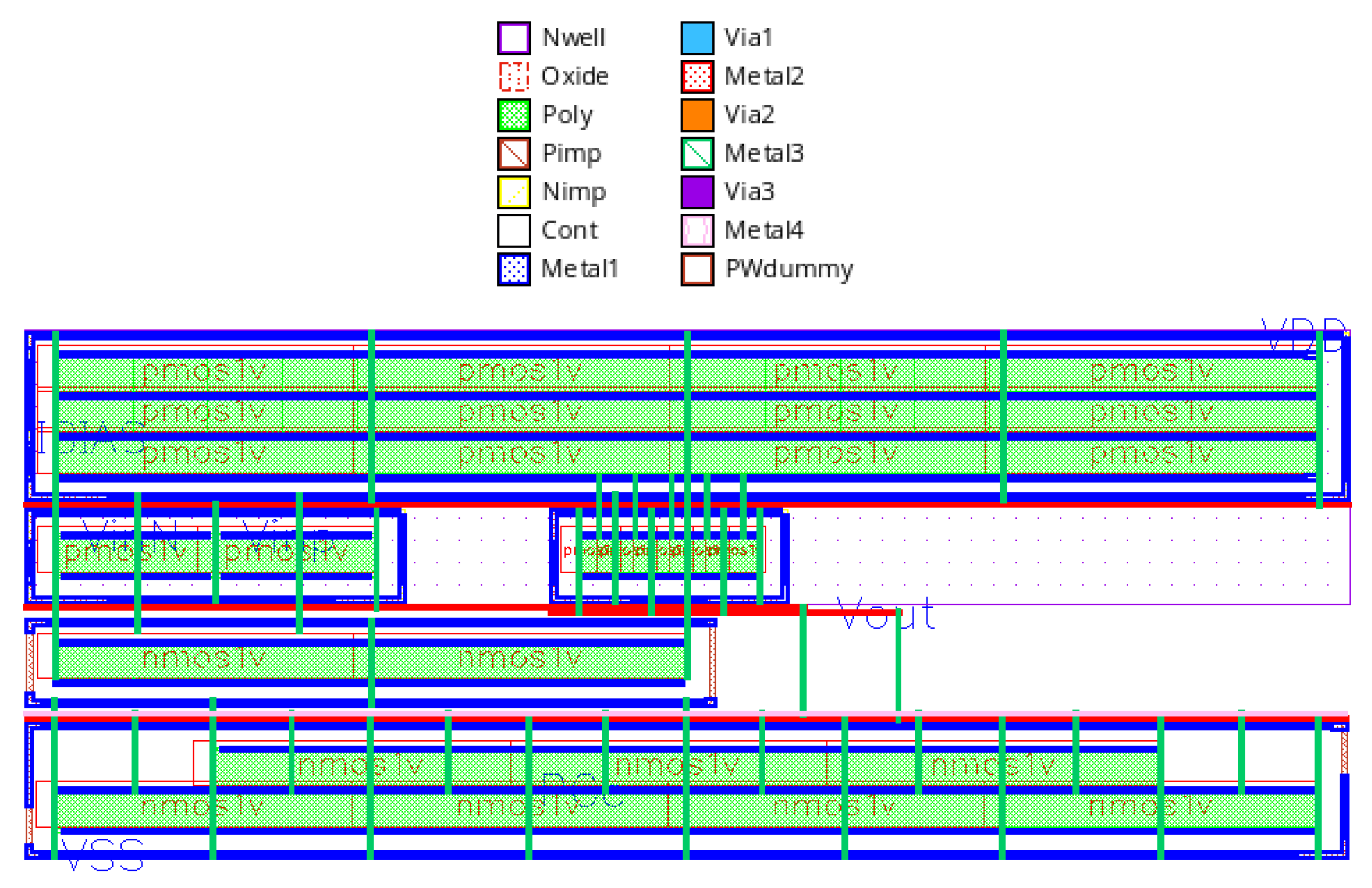

All the OTA’s are design-rule-checked, layouted and extracted using Cadence virtuoso’s ‘Layout XL’ tool (PVS, QRC plugins). For post-layout simulation, a ‘config’ view is created for the test bench circuit (‘schematic’ view). The ‘config’ view is also known as hierarchy editor. From ‘config’ view, all the OTA’s are set to ‘av-extracted’ view. This ‘av-extracted’ view contains all the parasitic resistances and capacitance’s formed after the layout. Then the test bench ‘schematic view’ and ADE L (Analog Design Environment) are opened from ‘config’ view. Again ‘spectre’ is chosen as simulator for the ADE L. Using the same ‘states’ from pre-layout simulation (saved previously), simulations are carried out for various analyses.

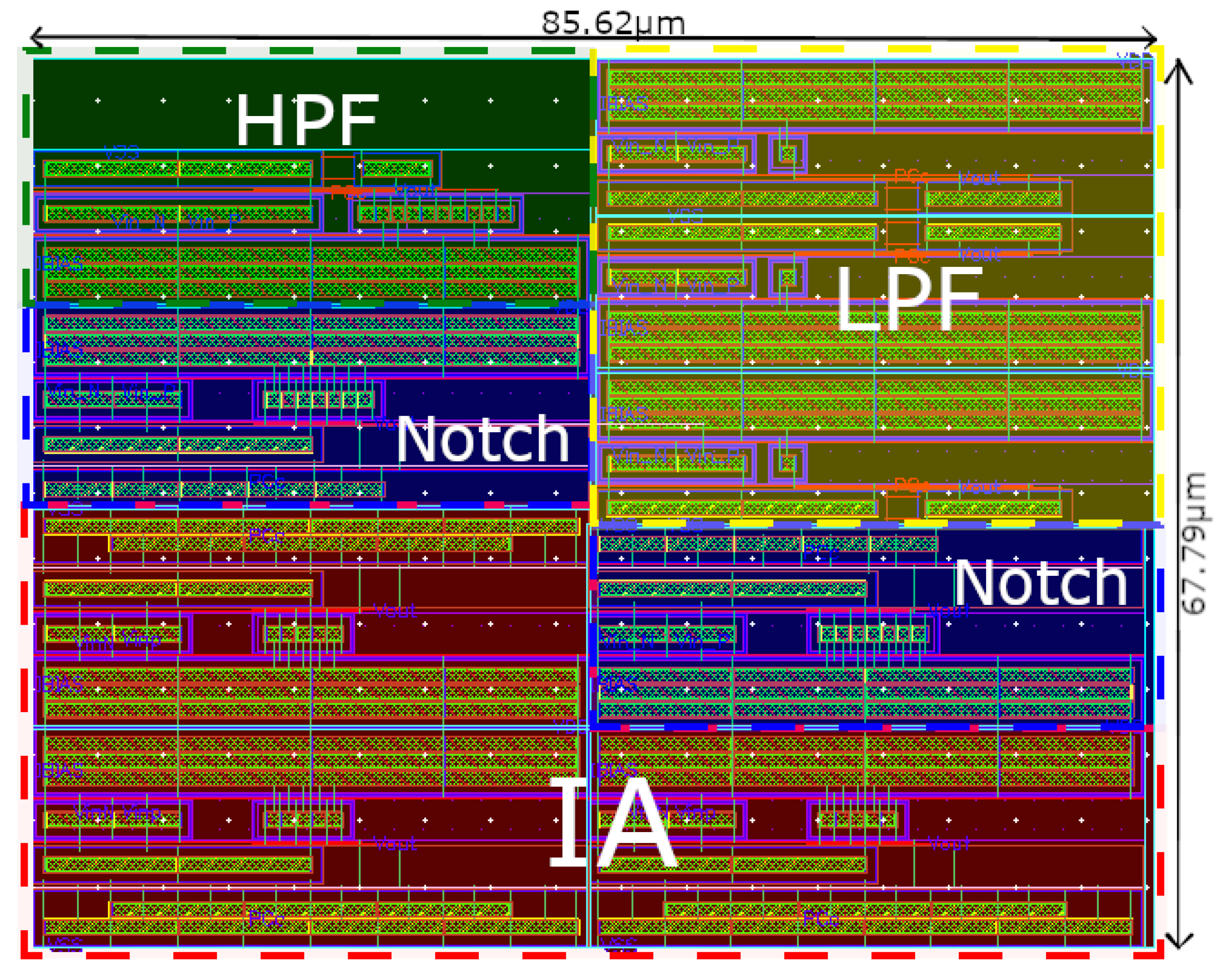

For the ECG system layout, only the OTA’s (total 9) of various blocks (IA, filters - Notch, LPF, HPF) and interconnection between them are considered. All the R, C components are excluded from the layout.

Figure 34 and

Figure 36 show the proposed layout view of the instrumentation amplifier OTA and ECG system respectively.

Advance layout technique such as common-centroid method is applied for both differential pairs and current mirror inside the OTA’s. This helps to reduce mismatch. No dummies are used. But sufficient space is kept for dummies, if required. The used layers for layout is shown in

Figure 34 (Left). For routing purpose, only metal 2, 3 and 4 are used, as higher metals have lower resistivity. This reduces voltage drop in interconnects. The direction for metal 1, 3 is kept vertical and for metal 2, 4 is horizontal. No metal jogging is done. Multiple via’s are placed wherever possible. This allows for better signal strength. For block to block inter-connection metal 4 is used. Devices with width greater than 1

m are broken into smaller multiple devices with width of 1

m. Guard ring for pMOS and nMOS devices are used to prevent latch-up issue. All the pMOS devices of OTA share a common ‘nwell’ while nMOS devices share a common ‘pdummy’. Top half of the layout is used for pMOS devices and bottom for nMOS devices. Routing symmetry is maintained between

pairs and

pairs. This helps in matching. The IA-OTA poses a dimension of 42.58µm x 16.995µm (W x H). The dimension could have been reduced with less gaurd rings and a more compact floor-plan (placement of devices). Though capacitors are not included in the layout, ‘mimcap’s can be used to implement such capacitors. ‘pmoscap’ would reduce the area but also reduces the performance of the system, as it incorporates resistance along with it. In 45 nm node, the sheet resistance of various metals would cause a very large area for resistors only. Consequently, we opt for off-chip resistor and capacitor.

Four different layouts and PEX for IA-OTA, Notch-OTA, LPF-OTA, HPF-OTA are done.

Figure 35 shows the post-layout magnitude response of the IA-OTA. The gain is slightly increased while -3dB frequency is reduced due to the added parasitics. These changes do not vary much and can be deemed as acceptable.

Finally, layout of the ECG system is designed with the OTA’s, as shown in

Figure 36. The red marked region is IA, blue is Notch, yellow is LPF and green is HPF block. The layout dimension is 85.62µm x 67.79µm (W x H), occupying an area of 0.0058mm

2.

Figure 36.

The proposed ECG filter circuit layout.

Figure 36.

The proposed ECG filter circuit layout.

Figure 37 demonstrates the post-layout frequency response of the ECG acquisition system, where no significant changes are observed. The new bandwidth is approximately 239 Hz, which is only 7 Hz lower than that obtained from the schematic-level simulation.

Figure 38 verifies a good similarity in noise performance with the pre-layout simulation. This justifies that the layout has less parasitic effects.

4.4. Comparison with State-of-the-Art Designs

Table 9 summarizes a comparison of the performance metrics with state-of-the-art designs for ECG acquisition systems. Among the mentioned works, this work utilizes the smallest technology node (45 nm). The order of the filter and gain of the system designed here are the highest among the reported works. This work has the smallest chip area, one of the best input-referred noise with power-line-interference removal capability. Rest of the parameters are comparable. These results highlight the fact that the

methodology developed in this work can be utilized in designing OTA with reduced time and effort.

Appendix A

; //SAMPLE OCEAN-SCRIPT FOR GM/ID CURVE GENERATION//

; DESIGN, RESULT, DEFINITION, MODEL FILE DIRECTORY

simulator( ’spectre )

design( "/home/simulation/pmos_char/spectre/schematic/netlist/netlist")

resultsDir( "/home/simulation/pmos_char/spectre/schematic" )

modelFile(

’("/pkg/eee/cadence/tech/gpdk045_v_5_0/..

/models/spectre/gpdk045.scs" "mc")

)

definitionFile(

"/home/work/save_op.scs"

)

;DC SWEEP

analysis(’dc ?saveOppoint t ?dev "/V0" ?param "dc"

?start ".1" ?stop ".6" ?lin "50" )

desVar( "half_supply" 300m ) ; M1, M2

desVar( "length" 45n )

desVar( "width" 1u )

envOption(

’firstRun t

’analysisOrder list("dc")

)

temp( 27 ) ; TEMPERATURE SET TO 27

;PARAMETRIC ANALYSIS - ‘length’ VARIED

paramAnalysis("length" ?values ’(4.95e-07

1e-06 5e-06 10e-06)

)

paramRun()

;PARAMETER EQUATIONS

gmoverId =((-getData("M0:gm" ?result "dc"))/getData("M0:id" ?result "dc"))

Id = (- getData("M0:id" ?result "dc"))

;CROSS-PLOTTING

newWindow()

ocnYvsYplot(?wavex Id ?wavey gmoverId)

awvLogXAxis(currentWindow() t)

awvSetXAxisLabel(currentWindow() "Id")

awvSetYAxisLabel(currentWindow() 1 "gm/Id")

addSubwindowTitle("pMOS - gm/Id vs Id")

;//Script finish//

Figure 1.

Typical block diagram of AFE for ECG signal acquisition

Figure 1.

Typical block diagram of AFE for ECG signal acquisition

Figure 2.

Simplified block diagram of the work in this paper

Figure 2.

Simplified block diagram of the work in this paper

Figure 3.

Two stage OTA with Miller Compensation

Figure 3.

Two stage OTA with Miller Compensation

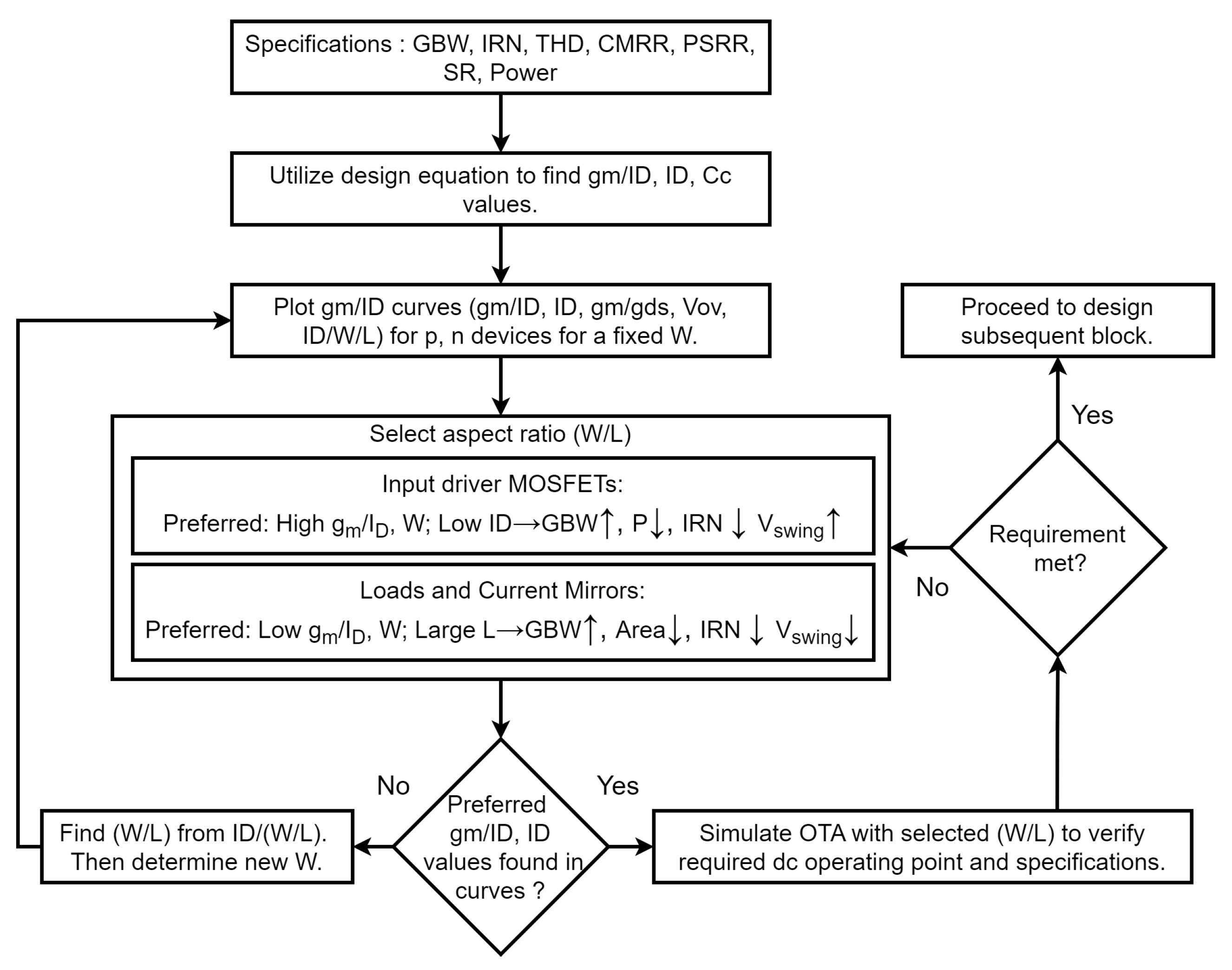

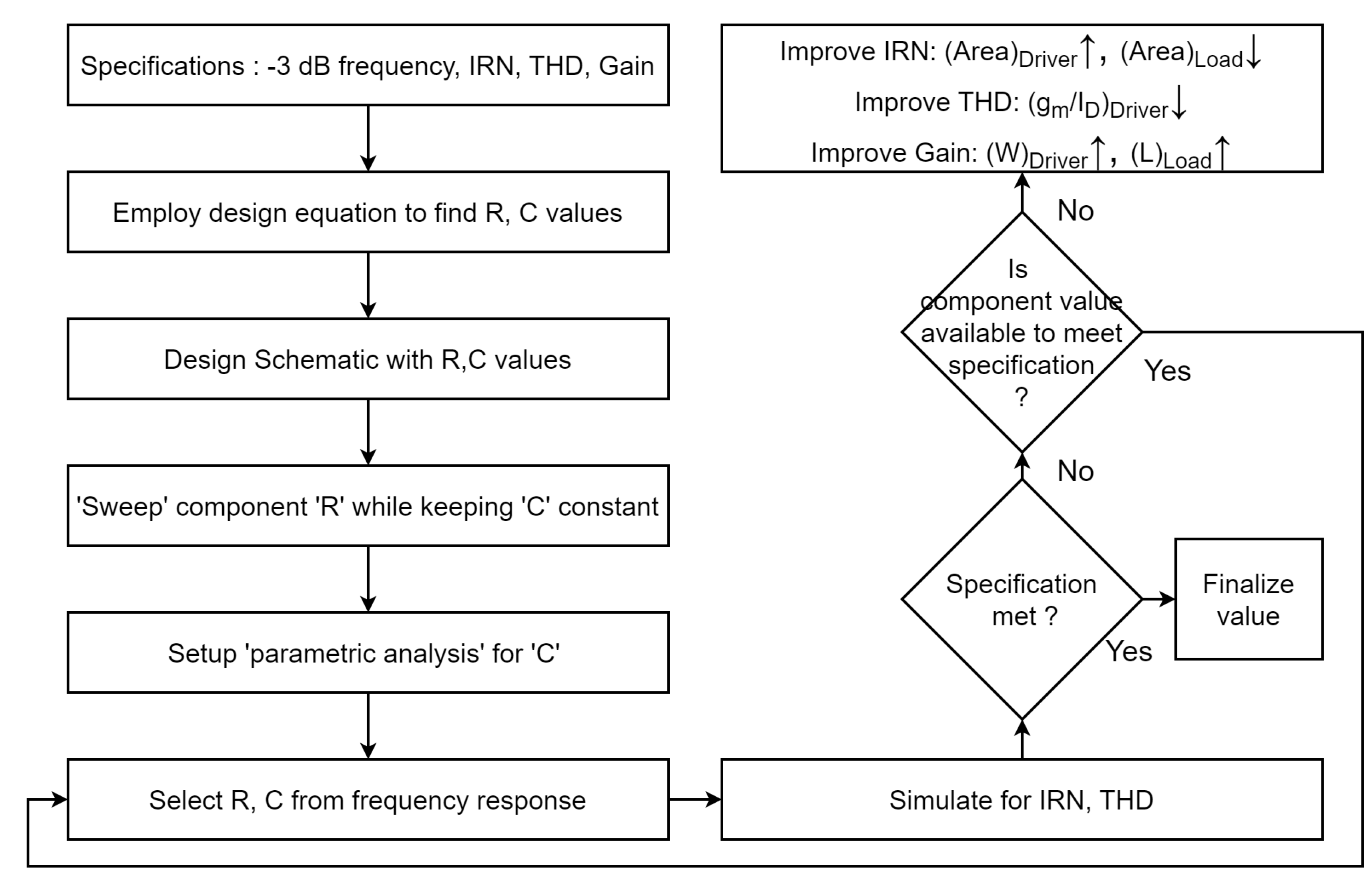

Figure 4.

Design flow for design and optimization of OTA.

Figure 4.

Design flow for design and optimization of OTA.

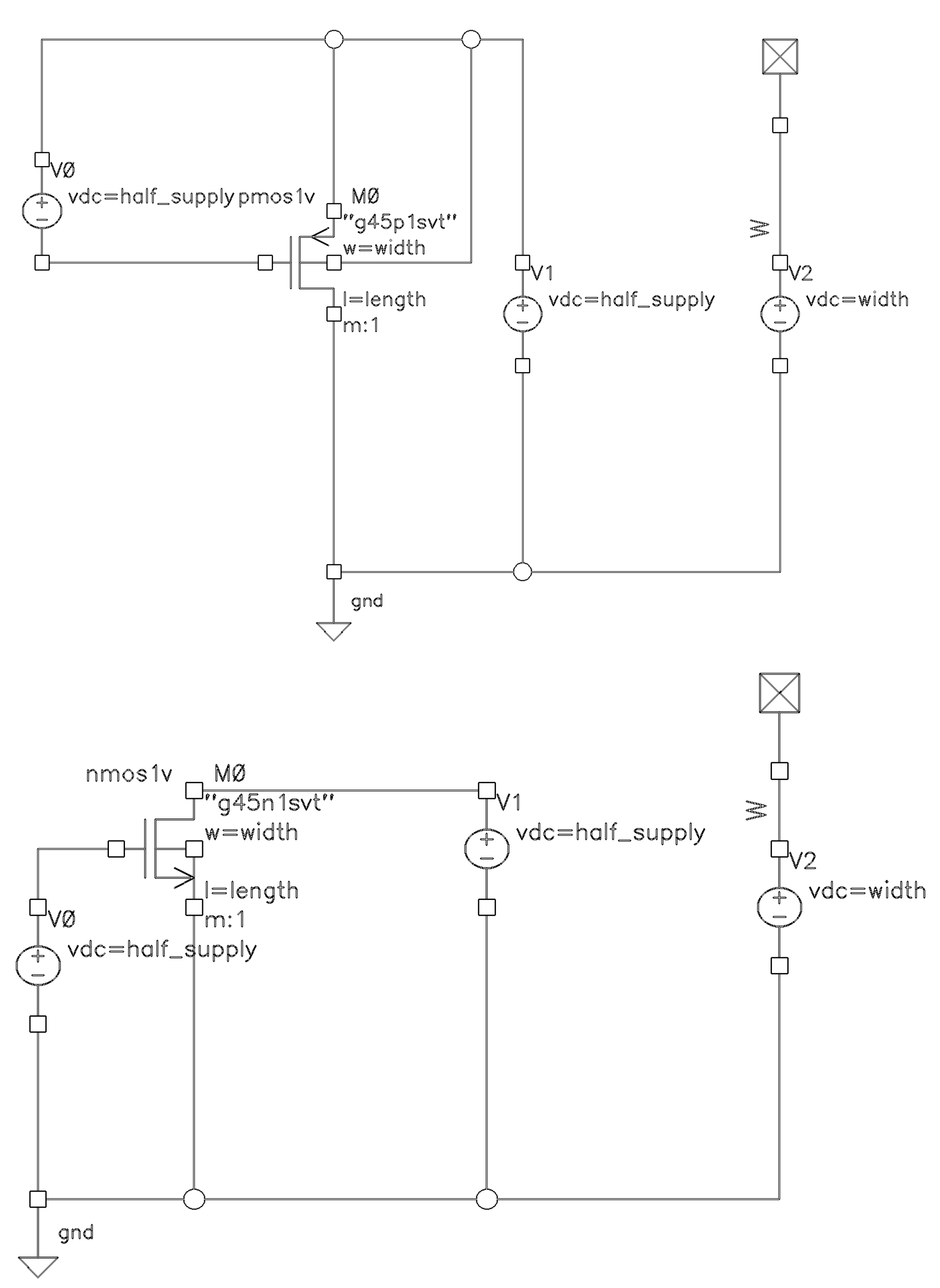

Figure 5.

Schematic diagrams for gm/ method curve generation. (Left) P- channel MOSFET. (Right) N-channel MOSFET.

Figure 5.

Schematic diagrams for gm/ method curve generation. (Left) P- channel MOSFET. (Right) N-channel MOSFET.

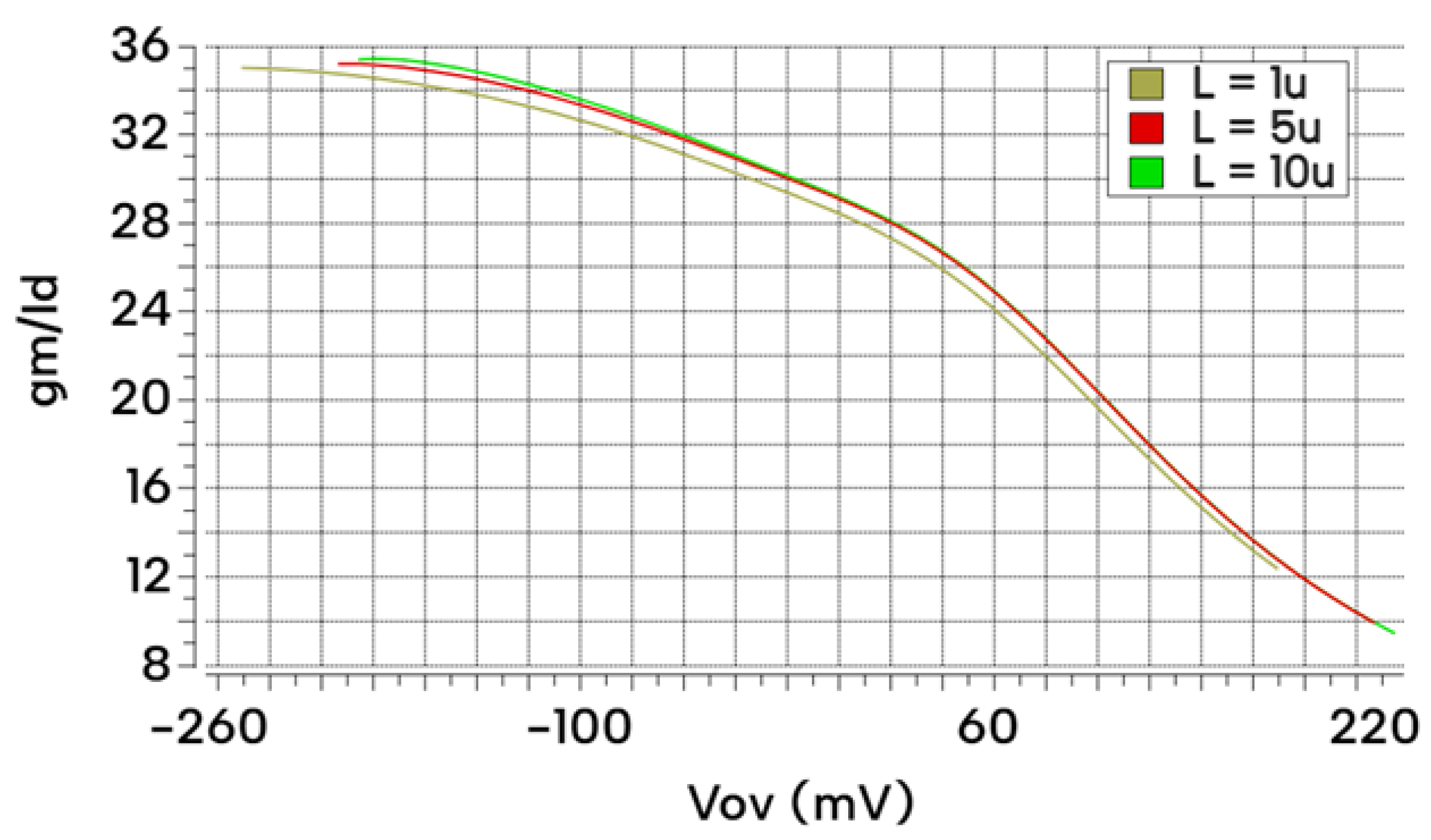

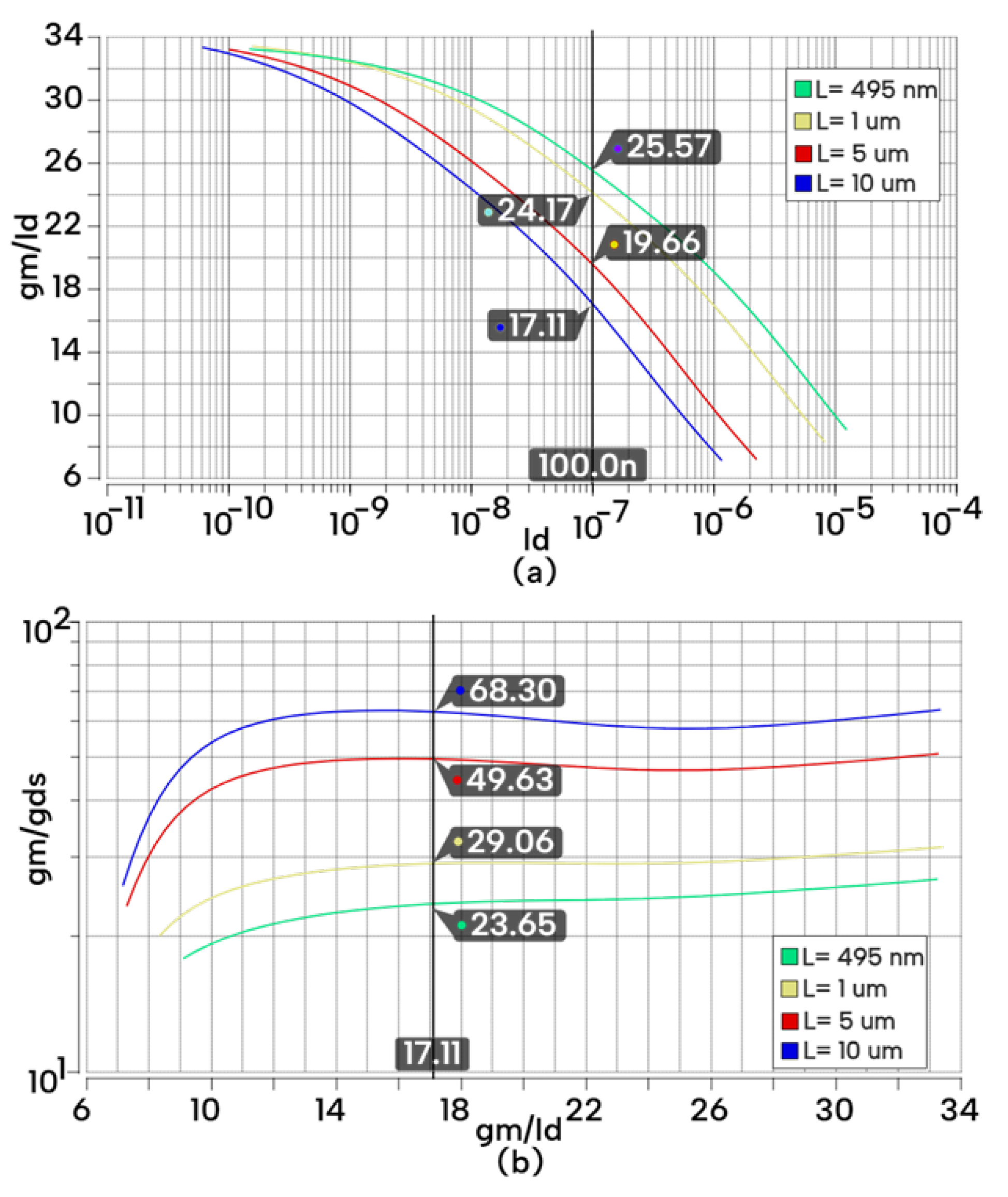

Figure 6.

vs Vov plot for p-channel MOS device at W=1 and L=1, 5, 10

Figure 6.

vs Vov plot for p-channel MOS device at W=1 and L=1, 5, 10

Figure 7.

Characteristic curves for the input pairs (). (a) vs for W=1 m. (b) vs for W=1 m. (c) vs Vov for W=1 m.

Figure 7.

Characteristic curves for the input pairs (). (a) vs for W=1 m. (b) vs for W=1 m. (c) vs Vov for W=1 m.

Figure 8.

Characteristic curves for the active loads (). (a) vs for W=1 m. (b) vs for W=1 m.

Figure 8.

Characteristic curves for the active loads (). (a) vs for W=1 m. (b) vs for W=1 m.

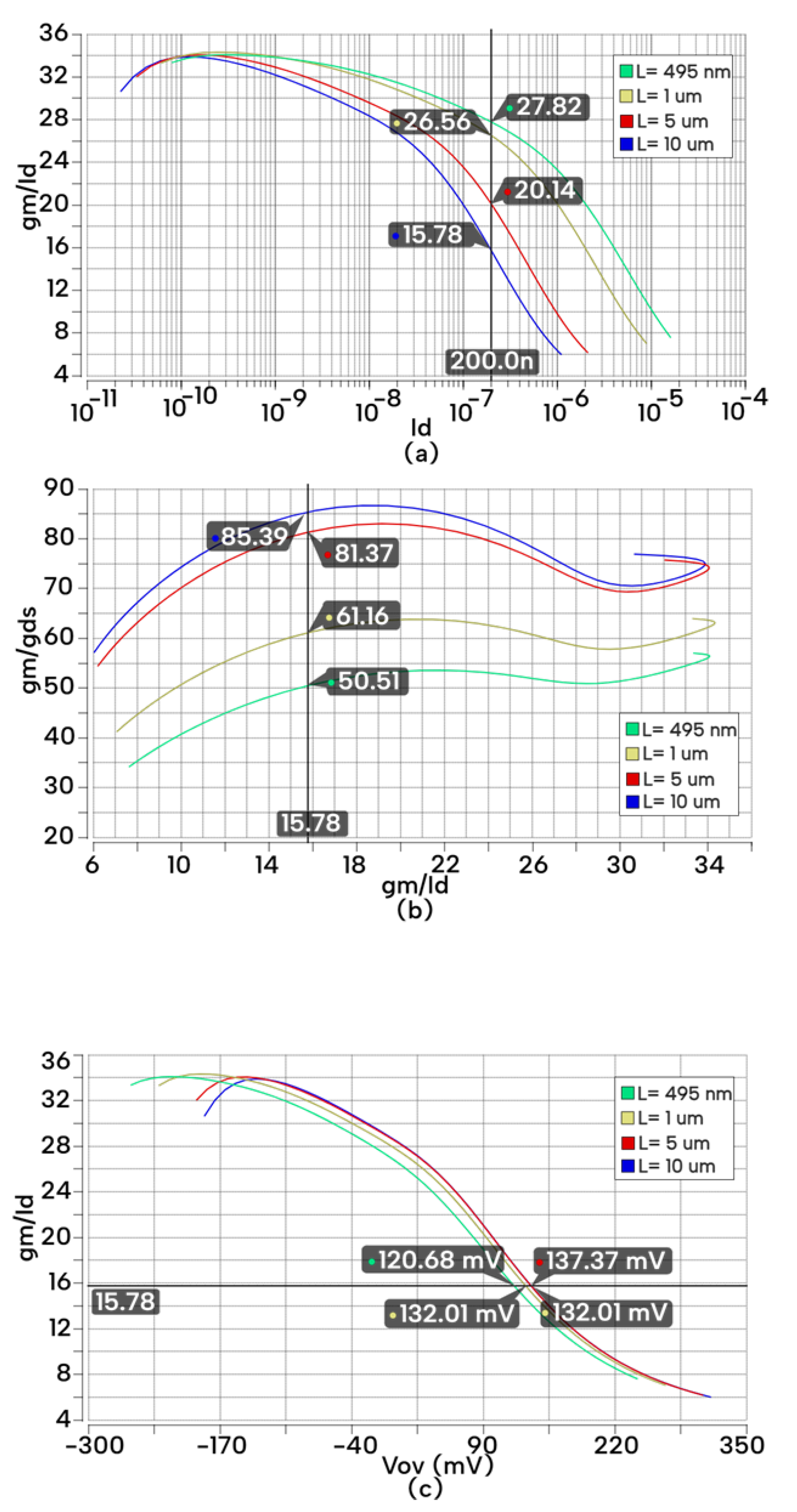

Figure 9.

Characteristic curves for and . (a) vs for W=1 m. (b) vs for W=1 m. (c) vs Vov for W=1 m.

Figure 9.

Characteristic curves for and . (a) vs for W=1 m. (b) vs for W=1 m. (c) vs Vov for W=1 m.

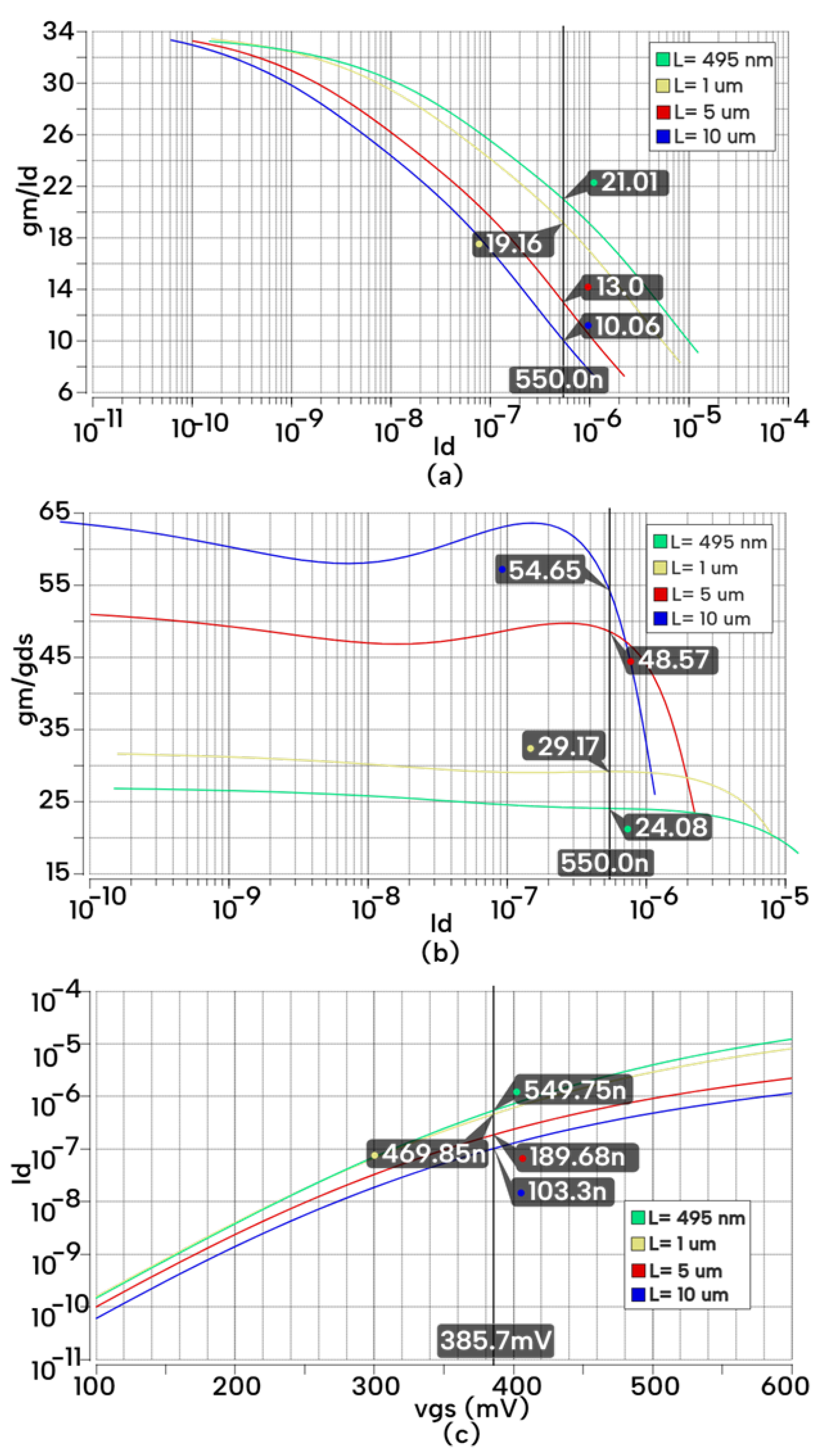

Figure 10.

Characteristic curves for the input driver (). (a) vs for W=1 m. (b) vs for W=1 m. (c) vs Vov for W=1 m.

Figure 10.

Characteristic curves for the input driver (). (a) vs for W=1 m. (b) vs for W=1 m. (c) vs Vov for W=1 m.

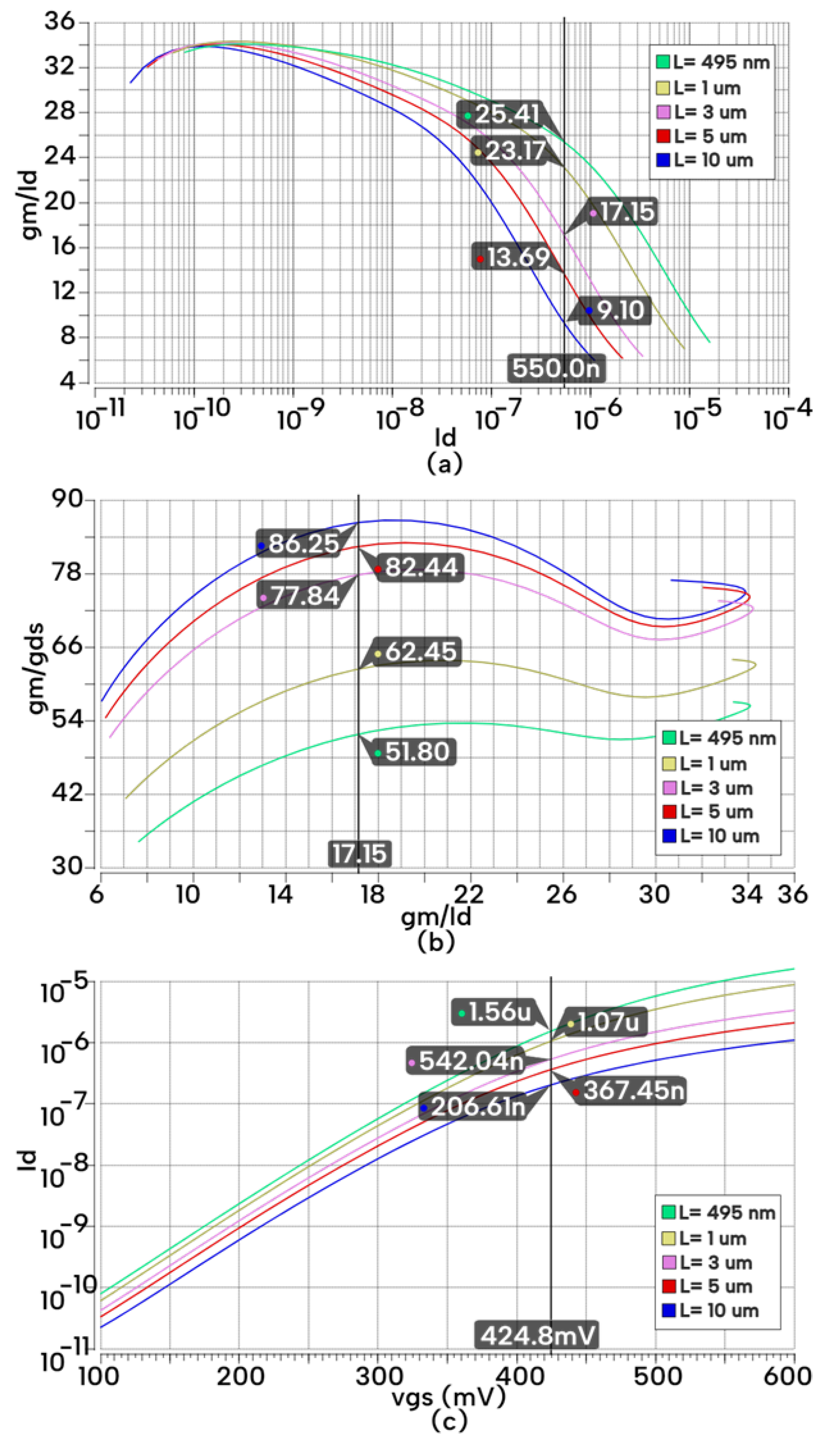

Figure 11.

(Characteristic curves for the active load (). a) vs for W=1 m. (b) vs for W=1 m. (c) vs Vgs for W=1 m.

Figure 11.

(Characteristic curves for the active load (). a) vs for W=1 m. (b) vs for W=1 m. (c) vs Vgs for W=1 m.

Figure 12.

Frequency response of designed OTA for the first iteration.

Figure 12.

Frequency response of designed OTA for the first iteration.

Figure 13.

DC operating points of the OTA circuit from simulation.

Figure 13.

DC operating points of the OTA circuit from simulation.

Figure 14.

, Vov and vs figures for p-channel MOS devices for W=1 m and L=5 m.

Figure 14.

, Vov and vs figures for p-channel MOS devices for W=1 m and L=5 m.

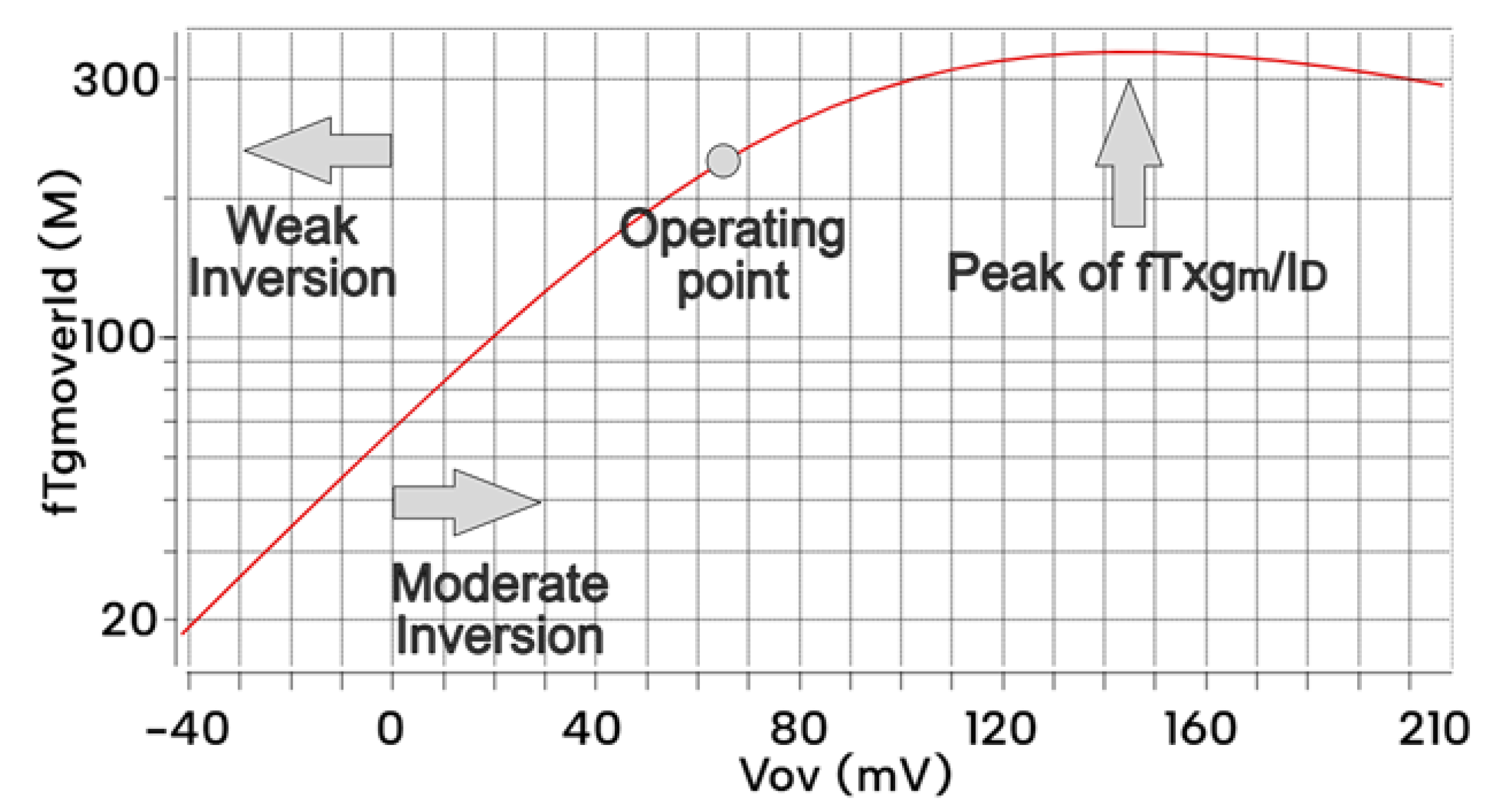

Figure 15.

ft x vs Vov plot for p-channel MOS device at W=1 and L=5.

Figure 15.

ft x vs Vov plot for p-channel MOS device at W=1 and L=5.

Figure 16.

Design flow for design and optimization of filters.

Figure 16.

Design flow for design and optimization of filters.

Figure 17.

Proposed ECG acquisition circuit diagram.

Figure 17.

Proposed ECG acquisition circuit diagram.

Figure 18.

Test-bench for dc, ac, transient, noise, pole-zero analyses.

Figure 18.

Test-bench for dc, ac, transient, noise, pole-zero analyses.

Figure 19.

Magnitude response of the designed OTA.

Figure 19.

Magnitude response of the designed OTA.

Figure 20.

Pole zero map of the OTA.

Figure 20.

Pole zero map of the OTA.

Figure 21.

CMRR waveform vs. frequency.

Figure 21.

CMRR waveform vs. frequency.

Figure 22.

PSRR waveform vs. frequency.

Figure 22.

PSRR waveform vs. frequency.

Figure 23.

Output voltage spectrum of the designed OTA for an input sinusoidal of 100 Hz and 0.4 mV p-p.

Figure 23.

Output voltage spectrum of the designed OTA for an input sinusoidal of 100 Hz and 0.4 mV p-p.

Figure 24.

Output impedance of the Operational Trans-conductance Amplifier.

Figure 24.

Output impedance of the Operational Trans-conductance Amplifier.

Figure 25.

Input impedance of the Operational Trans-conductance Amplifier.

Figure 25.

Input impedance of the Operational Trans-conductance Amplifier.

Figure 26.

Threshold voltage deviation distribution

Figure 26.

Threshold voltage deviation distribution

Figure 27.

Test-bench for the final ECG acquisition system.

Figure 27.

Test-bench for the final ECG acquisition system.

Figure 28.

Magnitude Response of the whole ECG system.

Figure 28.

Magnitude Response of the whole ECG system.

Figure 29.

Pole-zero locations of the ECG system.

Figure 29.

Pole-zero locations of the ECG system.

Figure 30.

Input referred noise density.

Figure 30.

Input referred noise density.

Figure 31.

(Left) ECG spectrum with added noise at 50 Hz and 500 Hz. (Right) Output voltage spectrum of the designed ECG acquisition system.

Figure 31.

(Left) ECG spectrum with added noise at 50 Hz and 500 Hz. (Right) Output voltage spectrum of the designed ECG acquisition system.

Figure 32.

Output of ECG the system for noisy inputs.

Figure 32.

Output of ECG the system for noisy inputs.

Figure 33.

THD for various amplitude and frequency.

Figure 33.

THD for various amplitude and frequency.

Figure 34.

(Left) Layers used in layout. (Right) Post layout view for the instrumentation amplifier OTA.

Figure 34.

(Left) Layers used in layout. (Right) Post layout view for the instrumentation amplifier OTA.

Figure 35.

Post layout magnitude response of the instrumentation amplifier OTA.

Figure 35.

Post layout magnitude response of the instrumentation amplifier OTA.

Figure 37.

The proposed ECG acquisition system post layout frequency response.

Figure 37.

The proposed ECG acquisition system post layout frequency response.

Figure 38.

The proposed ECG acquisition system post layout input referred noise.

Figure 38.

The proposed ECG acquisition system post layout input referred noise.

Table 1.

Summary of design requirements for individual MOSFETs of the 2 stage miller compensated OTA.

Table 1.

Summary of design requirements for individual MOSFETs of the 2 stage miller compensated OTA.

| MOSFET |

Inversion region |

Area |

|

|

Moderate |

Large |

High to Medium |

|

Strong |

Small |

Low |

|

Strong |

Small |

Low |

|

Moderate |

Large |

High to Medium |

|

Strong |

Small |

Low |

Table 2.

Design specification for the 2 stage miller compensated OTA.

Table 2.

Design specification for the 2 stage miller compensated OTA.

| Parameter |

Value |

|

±0.6 V |

|

200 nA |

| GBW |

1.25 MHz |

| Slew Rate |

0.67

|

| CMRR |

High () |

| PSRR |

High () |

| THD |

Low () |

|

2 pF |

Table 3.

Summary of dc operating point of each MOSFET device for the first iteration.

Table 3.

Summary of dc operating point of each MOSFET device for the first iteration.

| MOSFET |

Aspect Ratio (W/L) |

|

|

|

|

1/5 |

-301.62 mV |

101.38 nA |

23.91 |

|

1/10 |

386.64 mV |

101.38 nA |

16.96 |

|

6/10 |

-511.73 mV |

203.05 nA |

15.61 |

|

7/5 |

331.27mV |

573.03 nA |

20.87 |

|

5/1 |

-868.72 mV |

573.03 nA |

16.91 |

|

6/10 |

-424.84 mV |

199.64 nA |

15.73 |

Table 4.

Design parameters for the 2 stage miller compensated OTA of instrumentation amplifier.

Table 4.

Design parameters for the 2 stage miller compensated OTA of instrumentation amplifier.

| Parameter |

Value |

|

±0.6 V |

|

200 nA |

|

1 m/5m |

|

1 m/10 m |

|

6 m/10 m |

|

7 m/10 m |

|

5 m/1 m |

|

500 fF |

Table 5.

Finalized aspect ratios for the optimized OTAs.

Table 5.

Finalized aspect ratios for the optimized OTAs.

| Parameter |

IA |

LPF |

HPF |

Notch |

|

1 m/5m |

2.5m/5m |

1m/10m |

1m/5m |

|

1 m/10 m |

1m/10m |

1m/10m |

1m/10m |

|

6 m/10 m |

6m/10m |

6m/10m |

6m/10m |

|

7 m/10 m |

1m/10m |

1m/5m |

5m/5m |

|

5 m/1 m |

0.9m/0.9m |

10m/1m |

7m/1m |

Table 6.

Design parameters for the proposed ECG acquisition system.

Table 6.

Design parameters for the proposed ECG acquisition system.

| Parameter |

Value |

| R1 |

300 M

|

| R2 |

32 M

|

| R3 |

16 M

|

| R4 |

10 M

|

| R5 |

99 M

|

| R6 |

190 M

|

| R7 |

400 M

|

| R8 |

900 M

|

| R9, R10 |

3.5 G

|

| R11 |

1 G

|

| Rvar1 |

60 M

|

| Rvar2 |

200 M

|

| C1 |

99.2 pF |

| C2 |

198.4 pF |

| C3 |

1.4 pF |

| C4 |

900 pF |

Table 7.

Performance comparison of the proposed OTA with previously reported work.

Table 7.

Performance comparison of the proposed OTA with previously reported work.

| Parameter |

This Work |

[18] |

[19] |

[20] |

| Tech [nm] |

45 |

350 |

180 |

180 |

| Topology |

Miller-OTA |

CR-OTA1

|

GBFC-IBL2

|

MI-OTA3

|

| Supply [V] |

±0.6 |

2 |

± 0.75 |

± 0.5 |

|

[A] |

816n |

160n |

570n |

200n |

| Power [nW] |

980 |

320 |

855 |

267.5 |

| Gain [dB] |

64.5 |

39.8 |

47.6 |

31.17 |

| PSRR [dB] |

76.55 |

70 |

- |

37.26 |

| CMRR [dB] |

66.55 |

65 |

105.6 |

90.05 |

| THD [%] |

<1 |

<1 |

<1 |

<1 |

| IRN [] |

15.9 |

2.05 |

0.12 (PSD) |

174 |

| Zin [] |

5.1 |

- |

0.3 |

- |

Table 8.

Input-Referred Noise, Power Consumption and Total Harmonic Distortion for the filters.

Table 8.

Input-Referred Noise, Power Consumption and Total Harmonic Distortion for the filters.

| Parameter |

2nd order HPF |

Notch Filter |

5th order LPF |

| Input-Referred Noise |

70.1Vrms/

|

14Vrms/ @ PB |

130Vrms/

|

| Power Consumption |

2.034 W |

2.67 W |

1.21 W |

| Total Harmonic Distortion |

-92.5 dB |

-52.1 dB |

-112.2 dB |

Table 9.

Performance comparison of the designed ECG acquisition system with contemporary designs.

Table 9.

Performance comparison of the designed ECG acquisition system with contemporary designs.

| Parameters |

This Work1

|

[57]1

|

[20]1

|

[58]1

|

[59]1

|

[60]2

|

| ]1* Technology [nm] |

45 |

180 |

180 |

180 |

180 |

180 |

| ]3* Supply [V] |

±0.6 |

1.8 |

± 0.25 |

0.5 |

0.5 |

1 |

| ]3* Order |

HPF-2nd, LPF-5th |

LPF-2nd |

BPF-3rd |

LPF-4th |

BPF-2nd |

LPF-5th |

| ]3* Power [] |

10.88 |

19.4 |

.161 |

0.003 |

0.0313 |

0.041 |

| ]3* Gain [dB] |

58.06 |

34.5 |

0 |

-5.6 |

37.1 |

-7 |

| ]1* BW [Hz] |

.08-239.6 |

1.7-352 |

.1-250 |

200 |

1.5-112 |

250 |

| ]3* IRN [] |

33.6 |

3.47 |

198 |

91.9 |

17.9 |

134 |

| ]3* PLI Removal |

Notch |

No |

Notch |

No |

No |

No |

| ]3* Area [mm2] |

0.0058 (off-chip RC) |

156.25 |

0.0528 (off-chip cap) |

0.074 |

0.167 |

0.24 |