The proposed analog front-end has been designed and simulated referring to the 180 nm CMOS process from TSMC. This section delves into the layout design aspects of the dc-coupled pixel input amplifiers and provides sizing information concerning the various components. Additionally, it showcases results obtained through extensive simulations.

5.1. Layout and Transistor Sizing

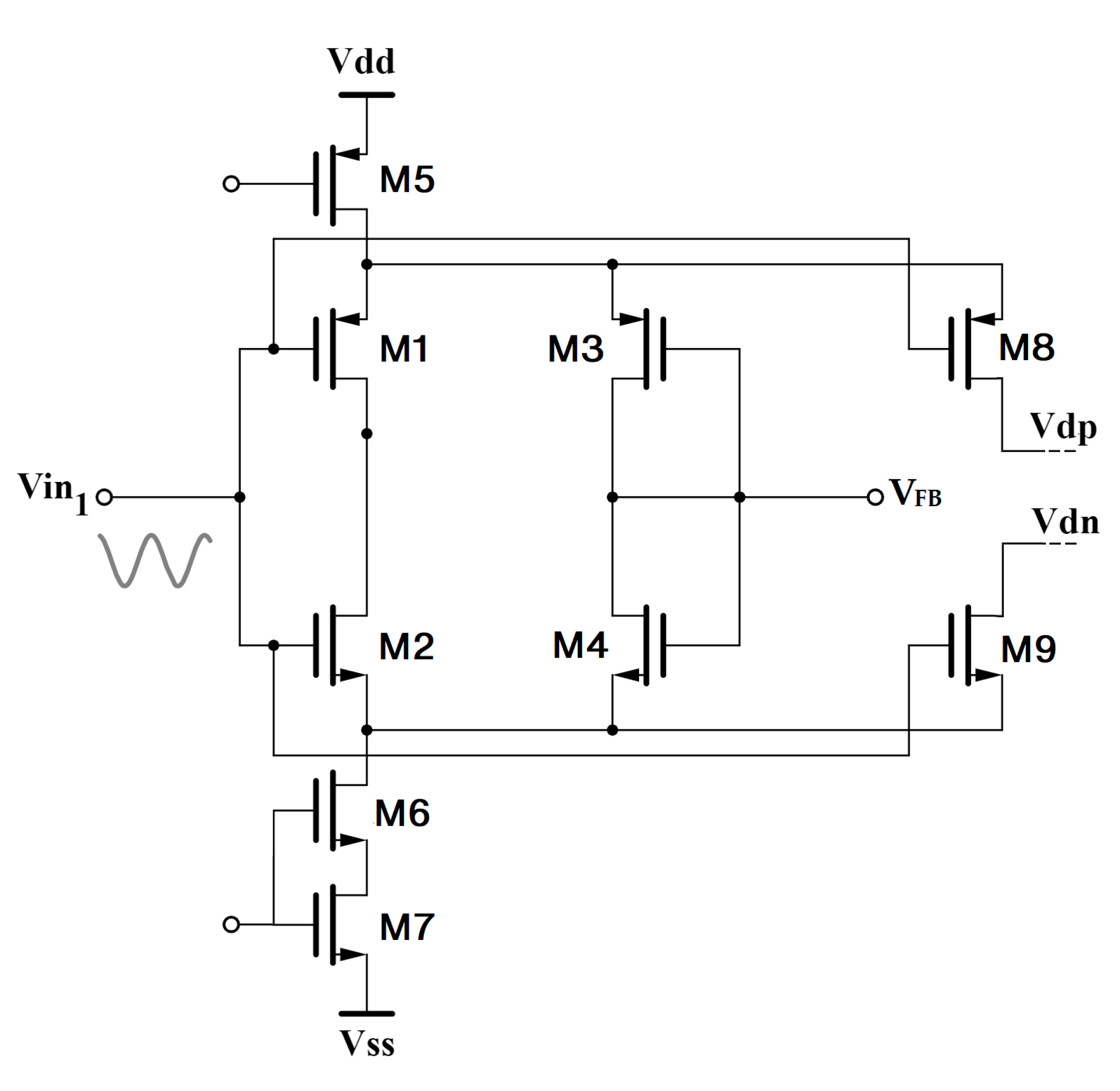

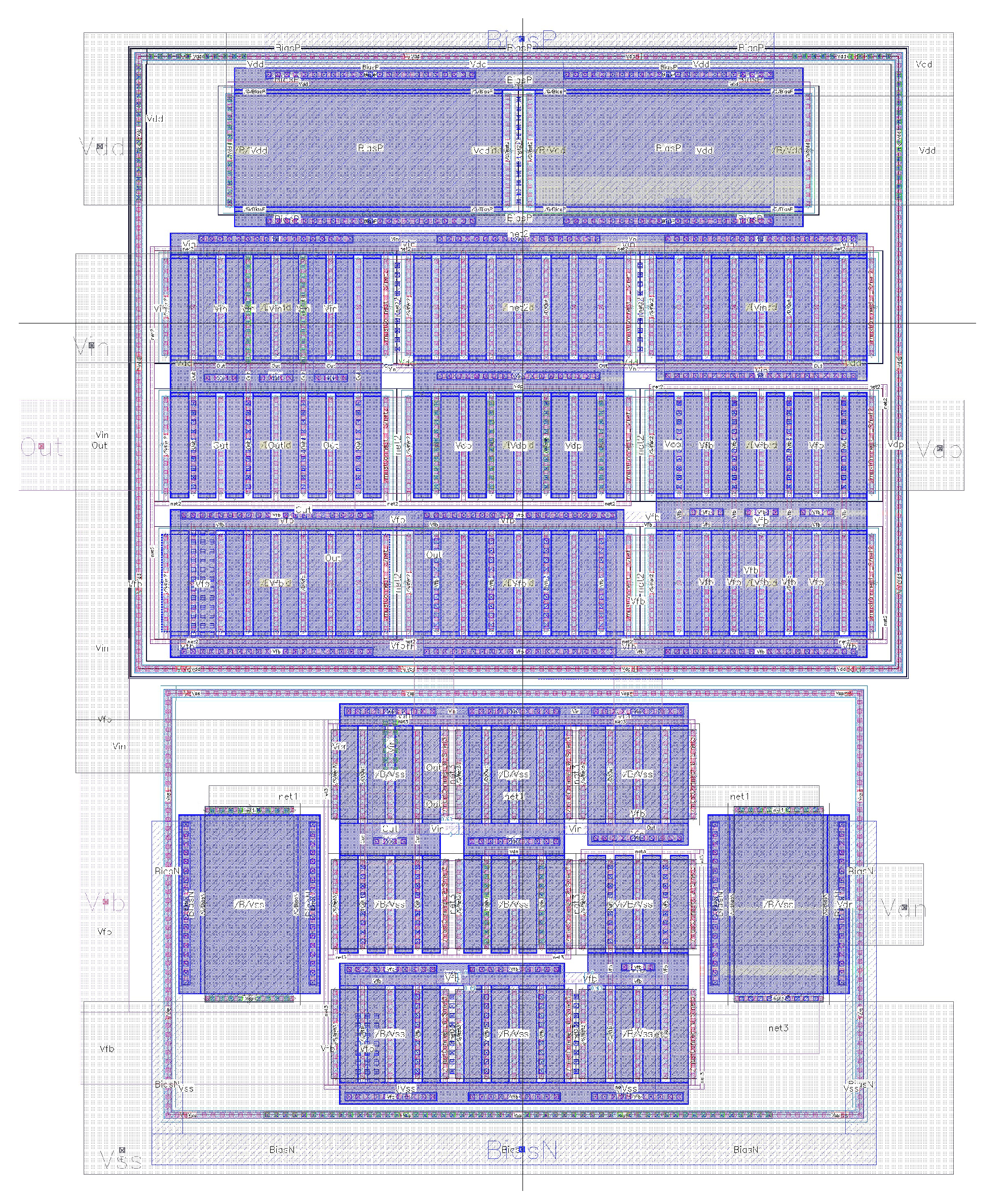

The layout of the inverter-based amplifier is reported in

Figure 9, showing an area of

. Utilizing four metal layers, this layout encompasses all the transistors described in detail in

Section 3.1. Notably, the smaller transistors (

M8-M9 in

Figure 3), responsible for replicating the scaled currents, are surrounded by the transistors of the inverter and the feedback transistors to mitigate potential mismatch between the devices.

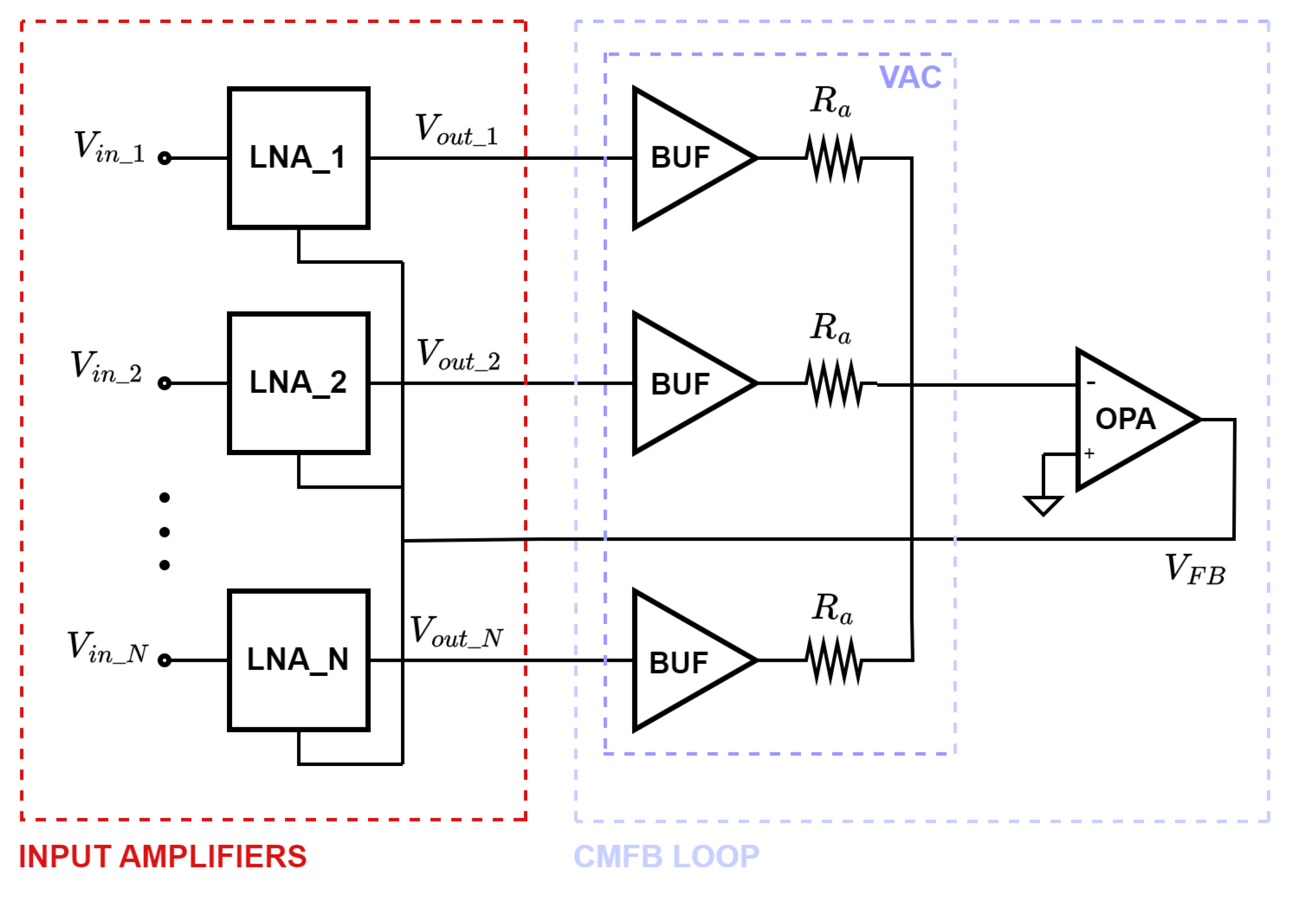

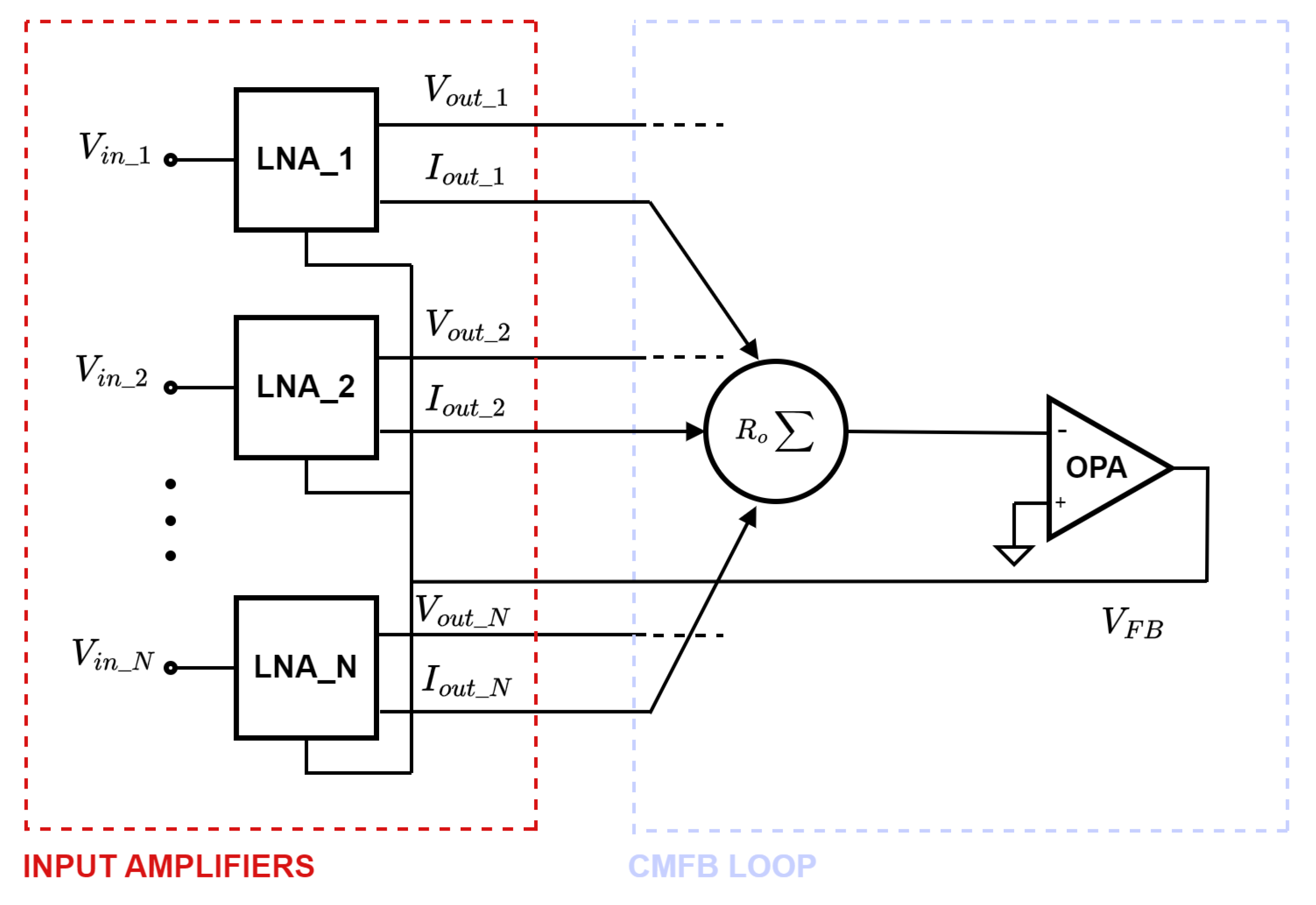

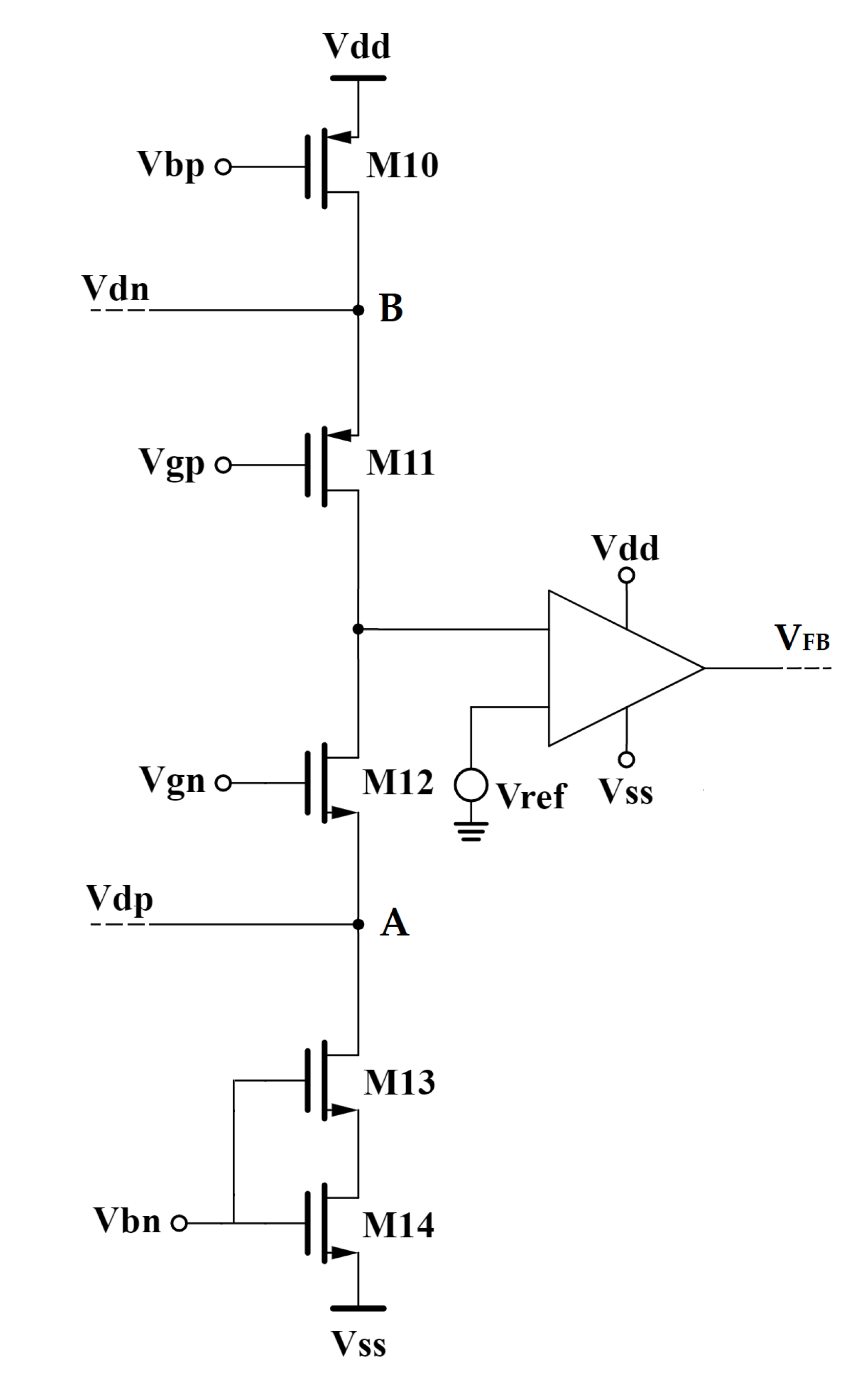

With reference to

Figure 3 and 4, table 1 summarizes the size parameters of the MOS transistors used both in the pixel amplifier and in the CMFB stage that makes up the closed loop. As stated before, the transistors that make up the inverter and the feedback transistors are sized equally by design. In order to accurately scale the currents of the main amplifiers, feedback transistors

M8 and

M9 are sized to have a width scaled by a factor 4. Transistors

M5 and

M6-M7 are sized with the intent of producing a bias current of 2.5

for the main amplifying branch. Regarding the common-gate transistors implemented in the current-summing branch of the front-end, sizes have been chosen to be equal to the replicating transistors to minimize area occupation. For biasing purposes, the

W and

L parameters of transistors

M10 and

M13-M14 have been chosen to generate a current at least equal to the sum of the scaled, replicated currents.

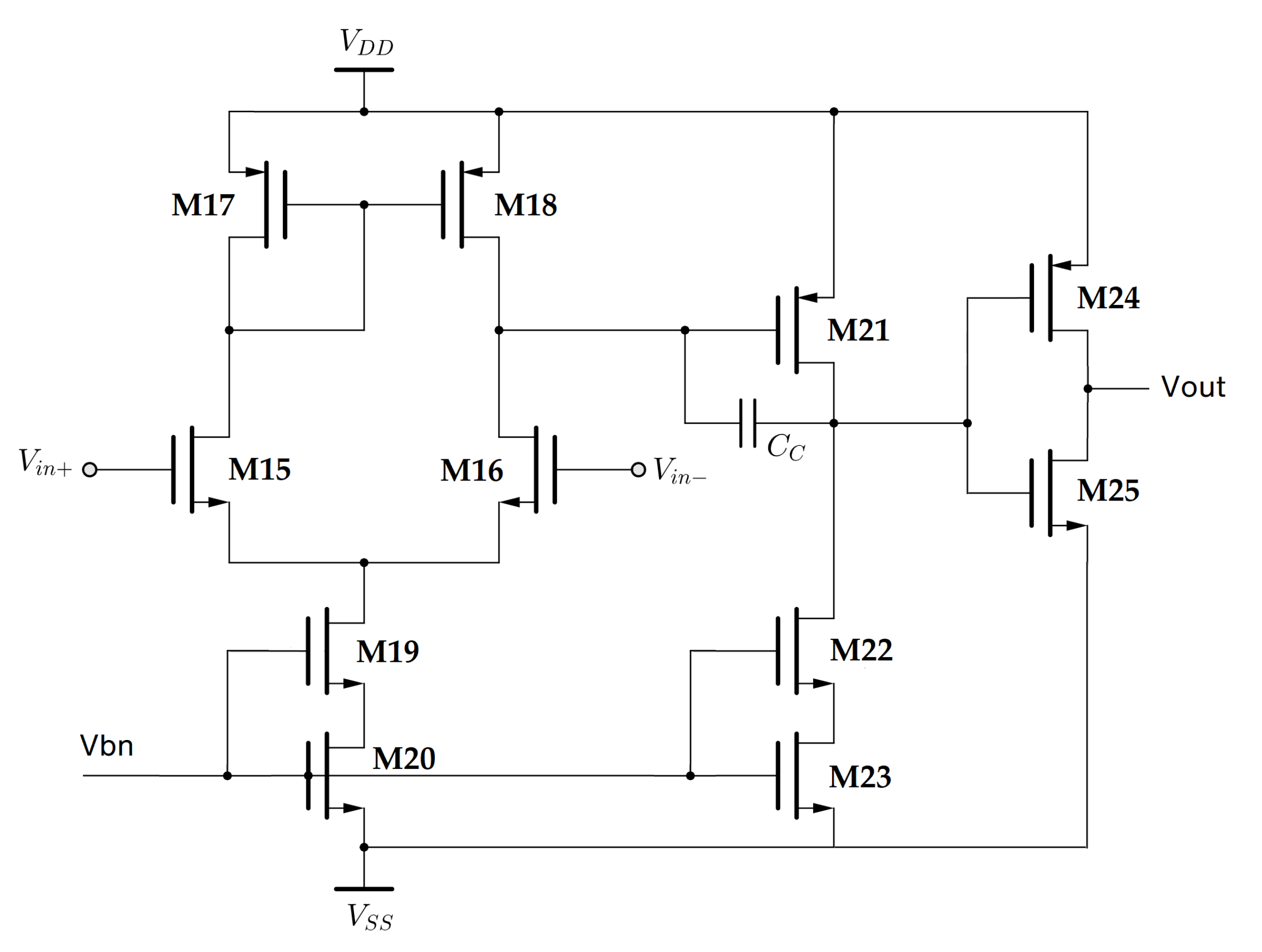

Table 2 displays the sizing choices made with respect to the error amplifier. In this case, the parameters of the transistors have been set with the aim of obtaining a high open-loop gain for the amplifier, of at least 80 dB, with a phase margin 60°.

Table 2.

Transistor sizes for error amplifier.

Table 2.

Transistor sizes for error amplifier.

| MOSFET |

Width |

Length |

| M15-M16 |

|

|

| M17-M18 |

|

|

| M19-M20 |

|

|

| M21 |

|

|

| M22-M23 |

|

|

| M24 |

|

|

| M25 |

|

1

|

5.2. Circuit Simulations

The proposed front-end’s nominal behavior was simulated within the Cadence Virtuoso environment. To achieve results that closely resemble the actual implementation of the neural recording system, simulations were conducted by using the post-layout netlist with extracted parasitics. The circuit is biased with a dual voltage supply (=-=0.5 V), while the total current used to bias a single channel is set at 3.5 .

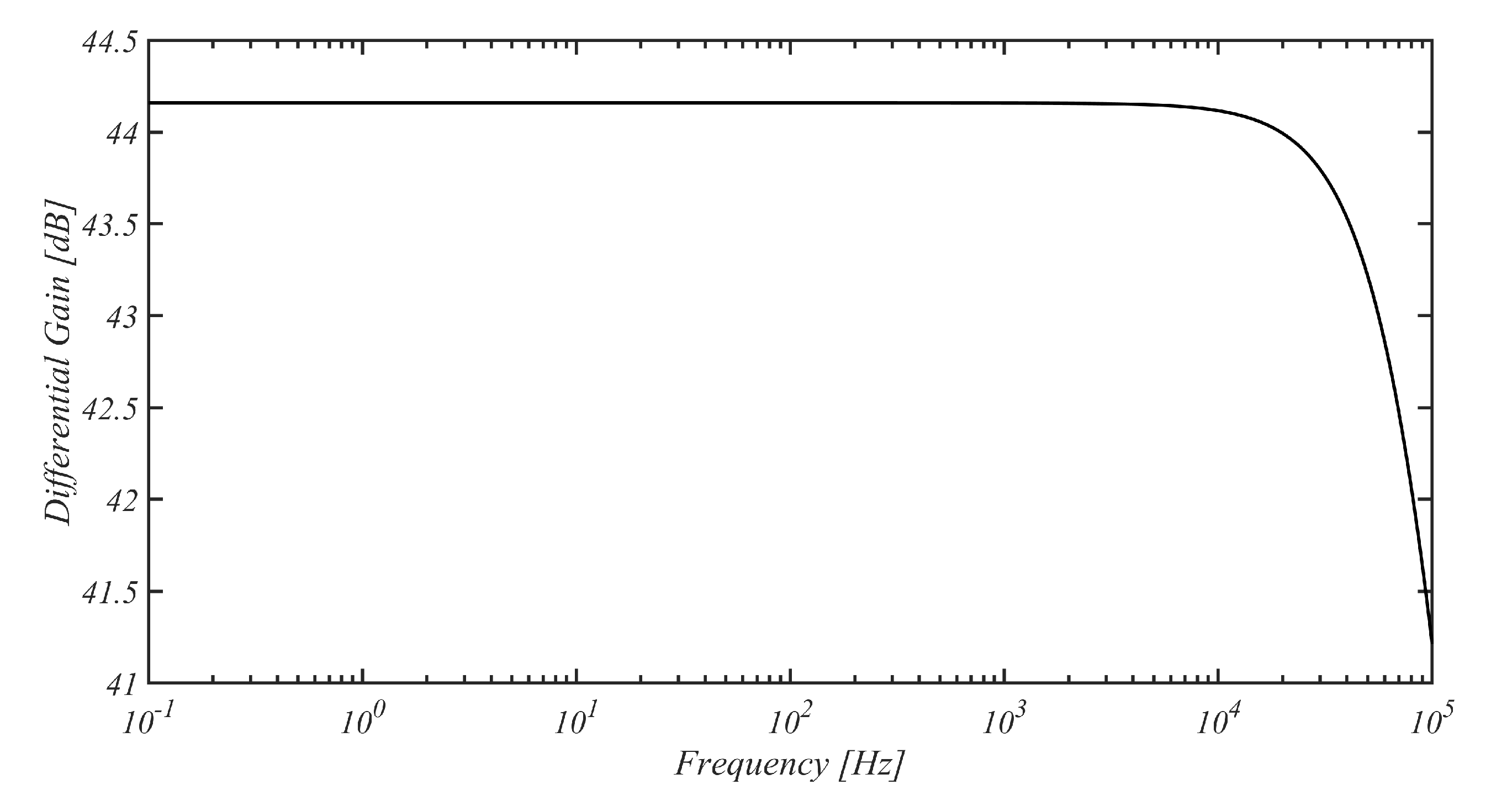

Figure 10 shows that the inverter-based pixel amplifiers integrated in each recording channel boast a differential gain of 44.16 dB, alongside a high cut-off frequency exceeding 100 kHz. These metrics highlight the amplifiers’ ability to capture and amplify neural signals across the entire frequency spectrum that encompasses both local field potentials and action potentials as measured from the extracellular space.

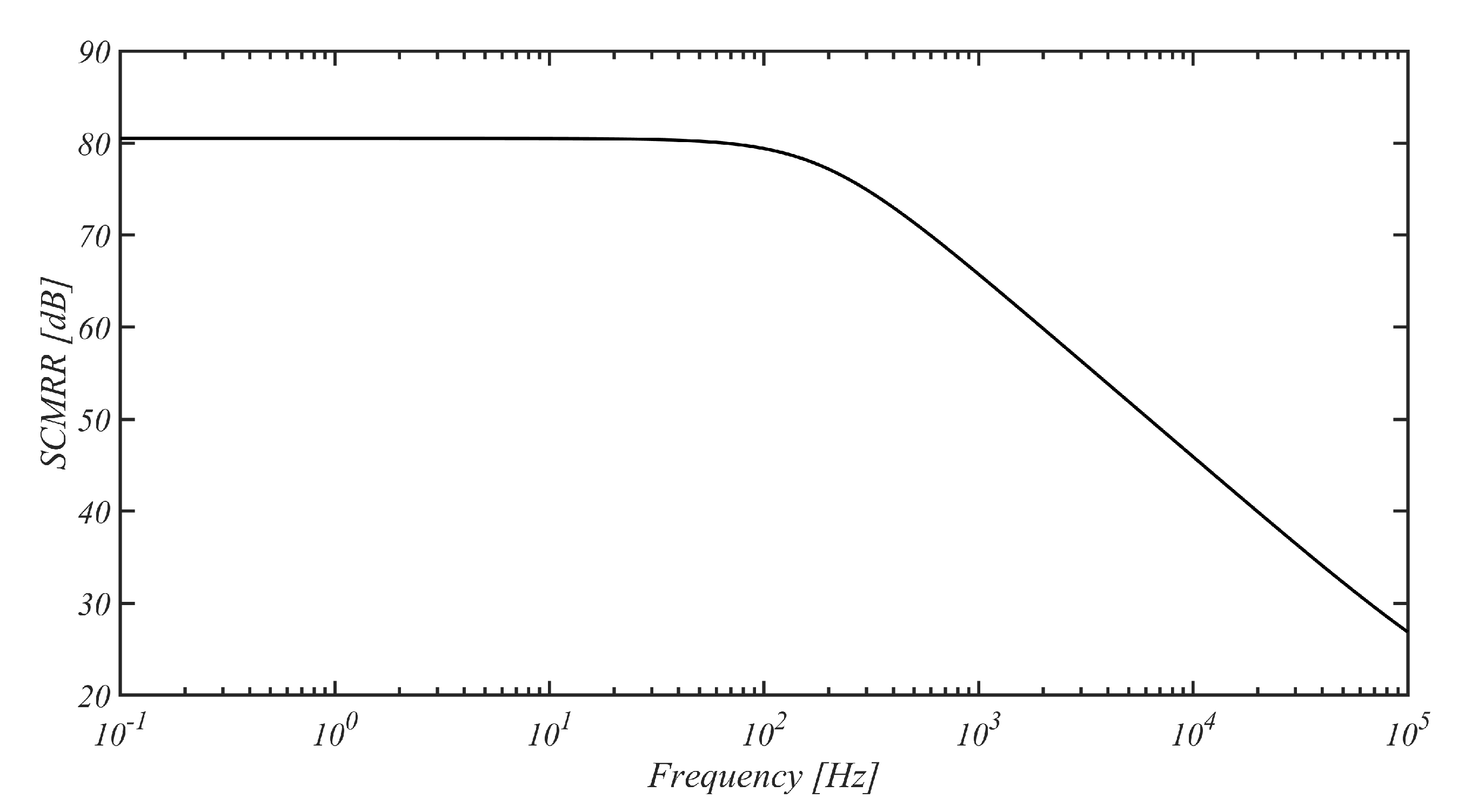

As shown in

Figure 11, further simulations have revealed a favorable SCMRR of 80.5 dB at low frequencies. Particularly noteworthy is the performance of the front-end within the range comprised between 0.1 Hz and 100 Hz, where the SCMRR maintains a value of at least 80 dB. A moderately high level of rejection is kept at higher frequencies, with the SCMRR exceeding 60 dB up to the frequency of 2 kHz.

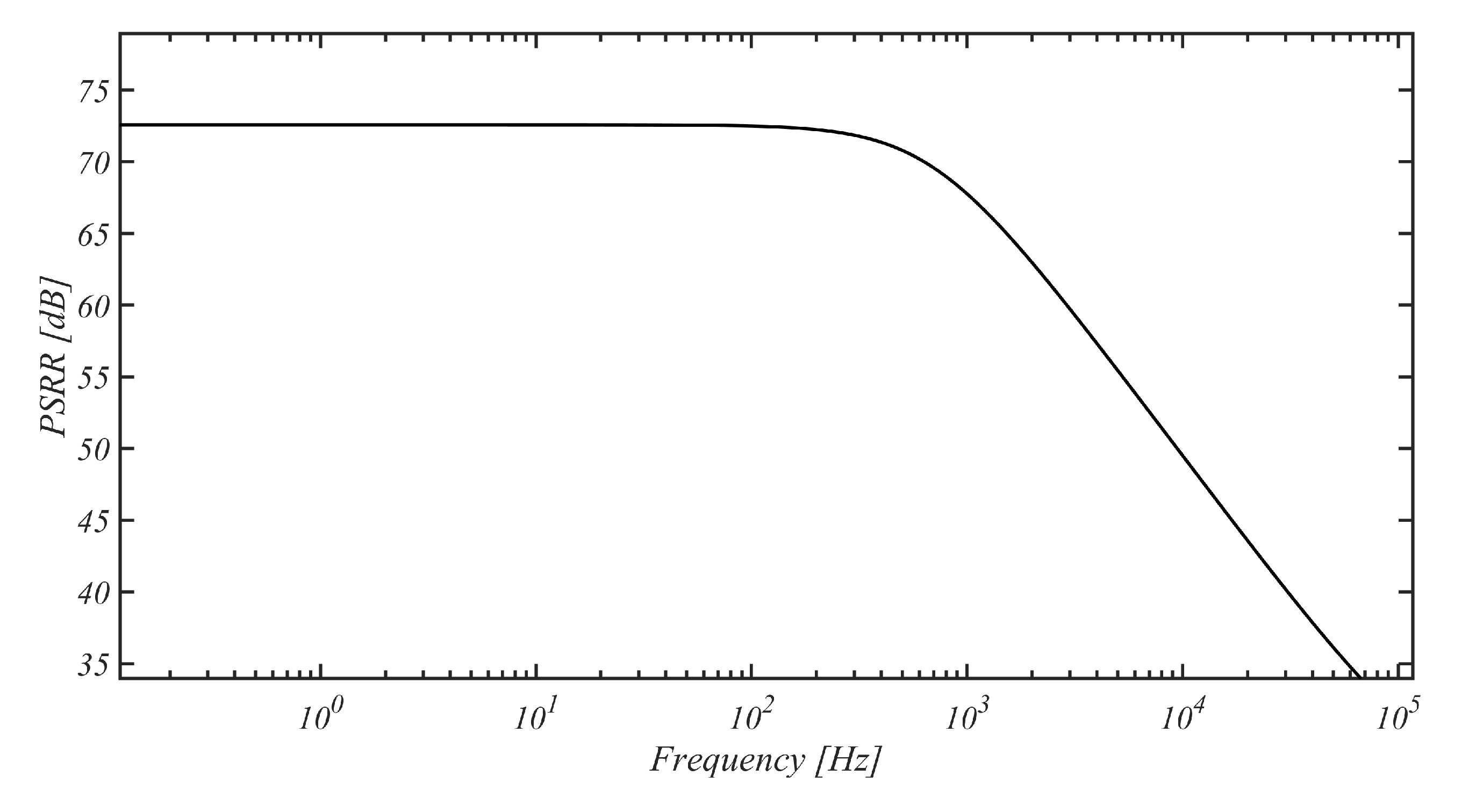

The PSRR of the front-end, as indicated in

Figure 12, shows a value of 72.55 dB at frequencies in the range that spans from 0.1 Hz to 100 Hz. For higher frequencies, the measured PSRR exhibits a similar behavior to the SCMRR, maintaining a level above 60 dB up until 2 kHz.

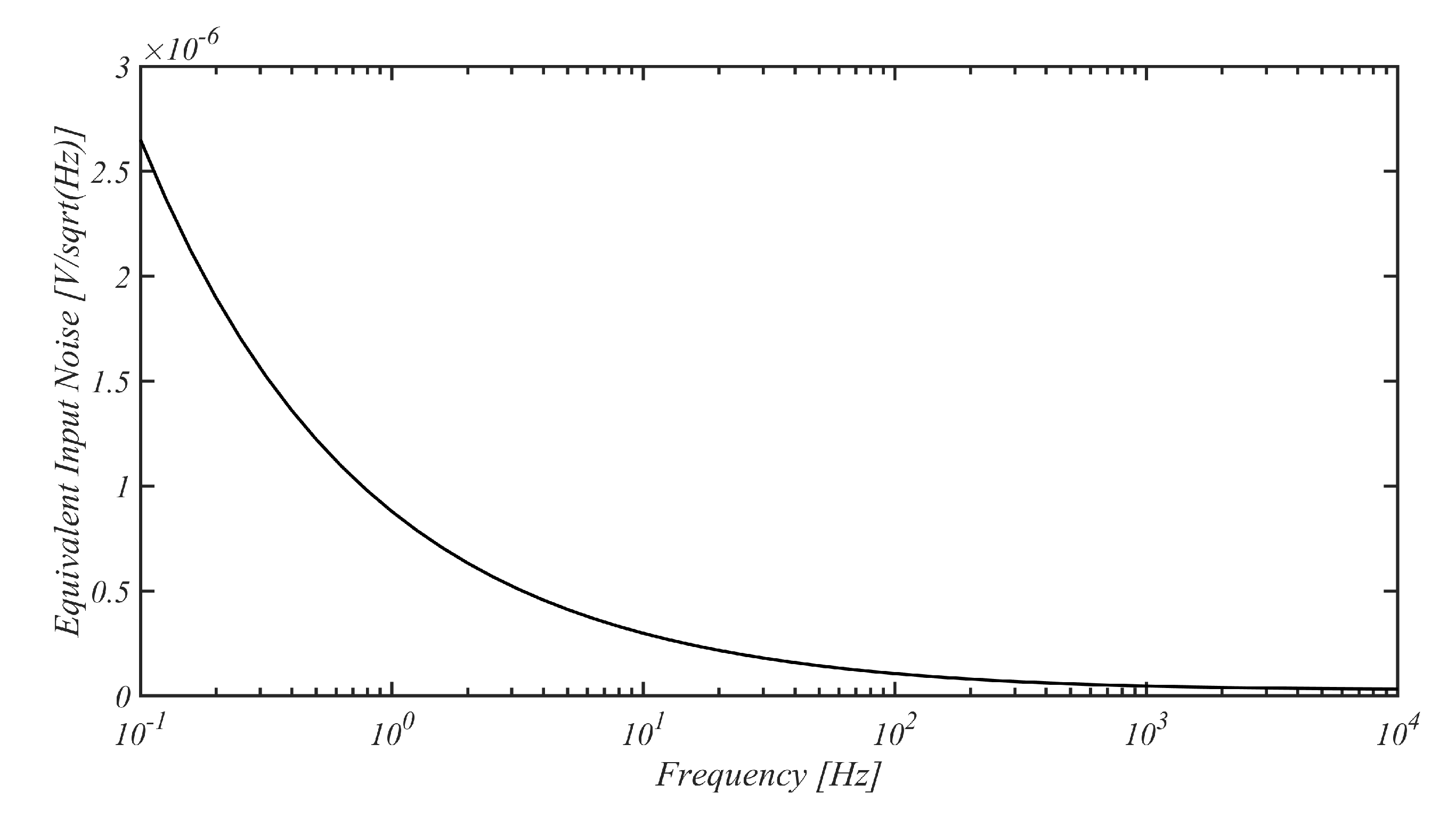

The input-referred noise spectrum of the input amplifier is presented in

Figure 13, showing a noise level of 100

at 100 Hz and a value of 50

at 1 kHz. By integrating the noise spectrum across various frequency intervals, the noise performance of the amplifier was evaluated in terms of input referred noise (IRN). The achieved results are compiled in table 3.

Table 3.

IRN values measured in different frequency intervals.

Table 3.

IRN values measured in different frequency intervals.

| |

Bandwidth |

Integrated Value |

|

|

|

|

|

|

|

|

|

A widely used figure of merit that allows to relate the noise performance of the circuit with its power consumption and bandwidth is the noise efficiency factor (NEF) [

37], expressed as follows:

where

is the thermal volta,

is the total supply current of the amplifier, and

is the amplifier’s bandwidth (in Hz). By replacing in (

33) the values of the total current required to bias the individual recording channel, the IRN and the bandwidth, we obtain

In addition, the power efficiency factor (PEF) can be computed as

5.3. Process and Mismatch Simulations

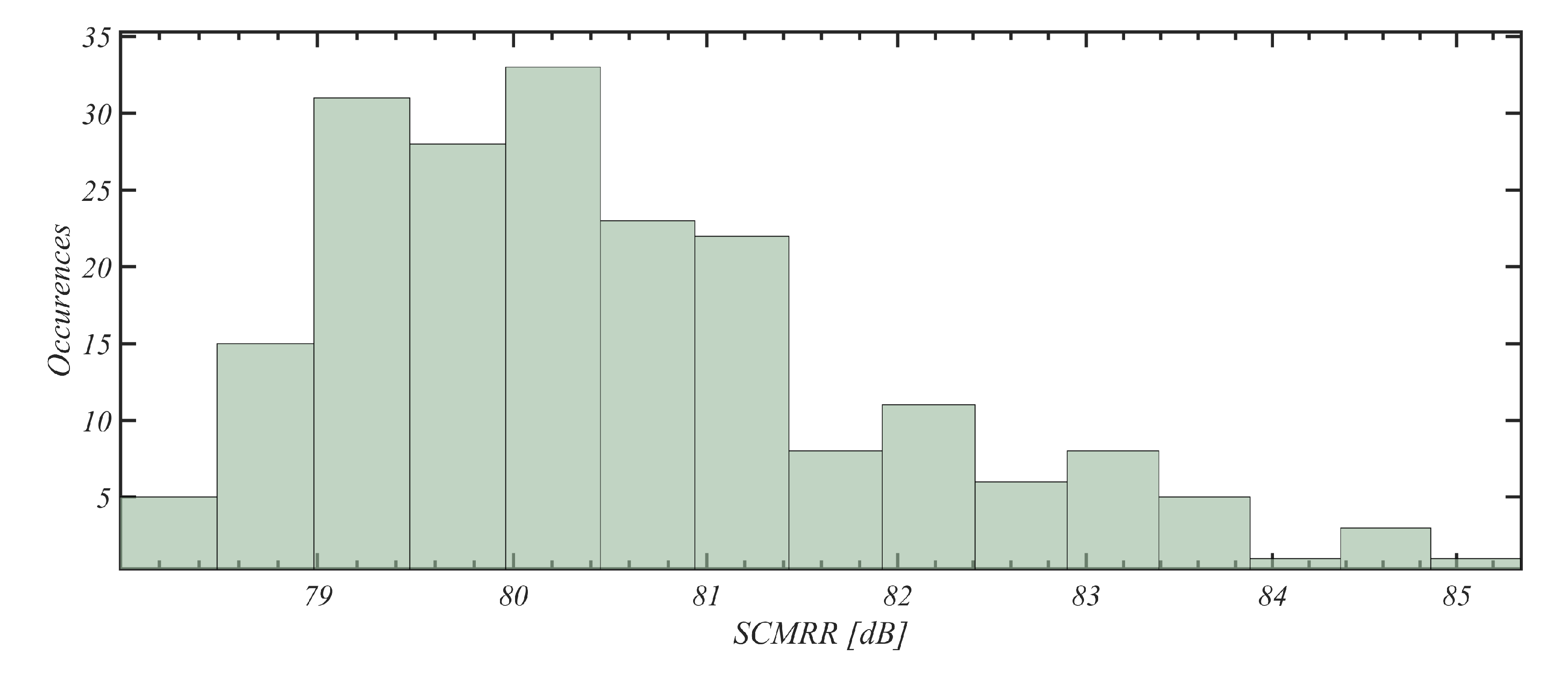

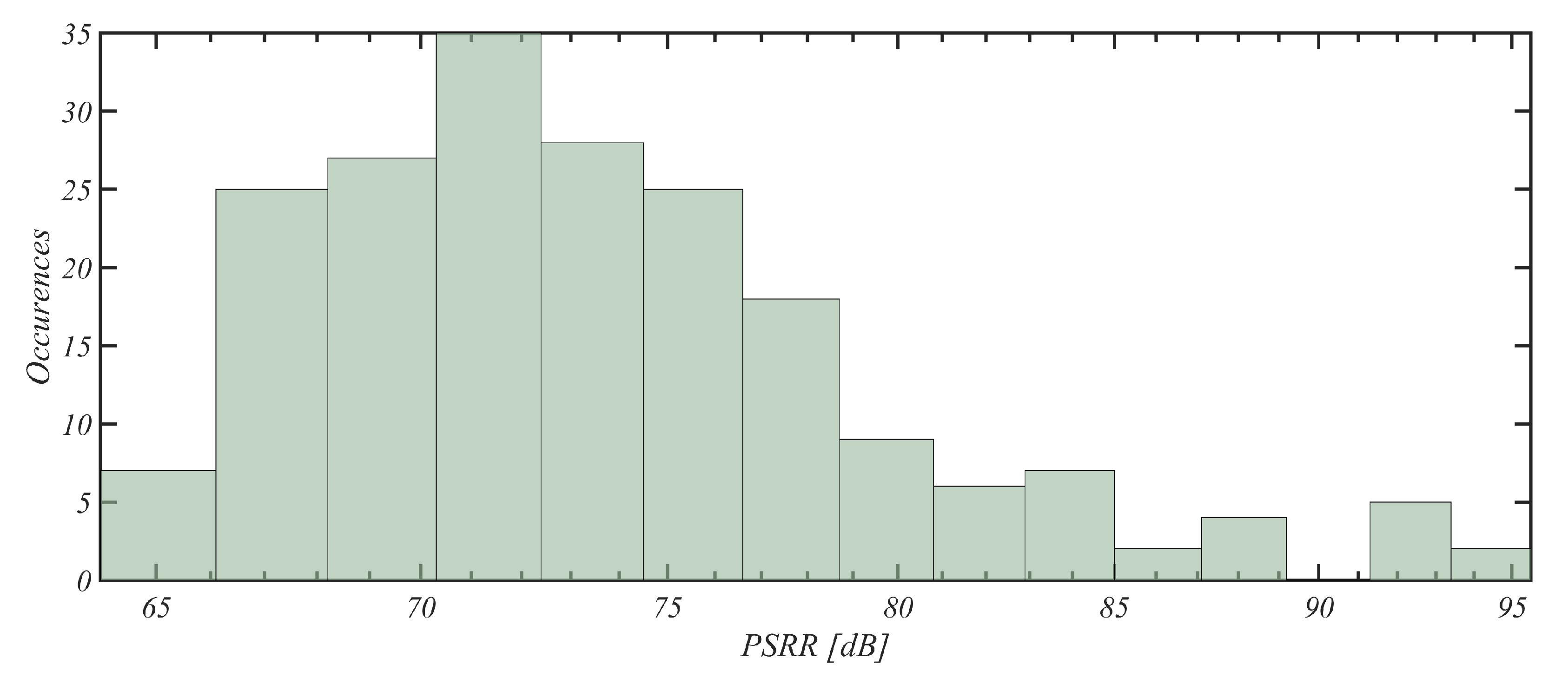

To assess the robustness of the front-end against PVT (Process, Voltage, and Temperature) and mismatch variations, the system underwent comprehensive testing via multiple simulations. Specifically, a Monte Carlo simulation comprising 200 iterations was conducted. The outcomes of these simulations are outlined in Table 4.

It must be noted that both the differential gain and the common-mode gain of the front-end demonstrate standard deviations within a 2 dB interval, consequently maintaining a similarly constrained SCMRR. Particularly, the differential gain exhibits minimal fluctuations around its mean value of 44.16 dB. Although the PSRR (Power Supply Rejection Ratio) variance is marginally higher, it remains moderately limited, with a mean of 74.11 dB and a variance of 6.30 dB. In both instances, the tested performance metrics yield favorable results, with both figure of merits exceeding 70 dB on average.

Table 4.

Performance under mismatch variations.

Table 4.

Performance under mismatch variations.

| Parameter |

Min |

Max |

Mean |

Std. Dev. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Concerning the SCMRR and the PSRR, histograms related to the distribution of results over the 200 Monte Carlo iterations are presented in

Figure 14 and 15.

To further test the robustness of the proposed front-end, a parametric simulation focusing on temperature variations was conducted. By gradually varying the operating temperature within the range [0 °C – 50 °C], the front-end’s gain and noise parameters, along with the rejection parameters, were evaluated accordingly (Tab. 5).

Regarding the differential gain of the input amplifiers, minimal fluctuations were observed; differently, the common-mode gain of the system exhibits a gradual decrease in value as the test temperature rises. Consequently, the SCMRR displays an increasing trend with growing temperatures, reaching a maximum value of 86.72 dB for 50 °C.

Conversely, the PSRR of the system tends to decrease in value with rising temperatures. In the range corresponding to the physiological conditions of the brain [38 °C – 41 °C], both PSRR and SCMRR are characterized by relatively minor variations, with values that manage to stay steady around 70 dB and 80 dB, respectively. When examining the noise performance of the front-end amidst temperature variations, it’s expected for the IRN of the system to experience a gradual rise. Nevertheless, with 4.23 , considering the total bandwidth [1 Hz – 7.5 kHz], just barely exceeds its nominal value, measured at 27 °C.

Table 5.

Performance under temperature variations.

Table 5.

Performance under temperature variations.

| Temp (°C) |

0.00 |

10.50 |

21.00 |

31.60 |

42.10 |

50.00 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Continuing with the evaluation of the front-end, the following batch of simulations was conducted by varying the power supply voltage of ±10% of its nominal value. By consulting the results displayed in table 6, it emerges that variations in the differential gain were once again minimal. In a similar manner, the common-mode gain of the system varied between a minimum of -39.21 dB for (Vdd - Vss) = 1.1 V, and a maximum of -32.36, corresponding to (Vdd - Vss) = 0.9 V.

Integrating the input noise spectrum in the bandwidths of interest revealed a minor increasing trend in the band related to the local field potentials [1 Hz – 300 Hz] and a minor decreasing trend as it pertains to the band of the action potentials [300 Hz – 7.5 kHz]. Overall, the IRN measured in the total frequency band exhibits a negligible decrease.

Table 6.

Performance under supply voltage variations.

Table 6.

Performance under supply voltage variations.

| Vdd-Vss (V) |

0.90 |

0.94 |

0.97 |

1.02 |

1.07 |

1.10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

To conclude with the PVT analysis, the results of the simulations under corner variations are compiled in Table 7. Generally, it can be observed that the front-end’s robustness is quite favorable.

Table 8 shows a comparison between the front-end proposed in this work and various analog front-ends that were introduced in recent years. For most parameters, the simulation results presented in this section of the paper are comparable with modern state-of-the-art findings. Of particular importance is the area occupation per recording channel which, for our devised front-end, is reduced by a factor 3 with respect to the front-end introduced in [34], and is approximately equal to a tenth of the area occupied by the work presented in [33]. Additionally, thanks to the implemented closed CMFB loop, the CMI of the front-end hereby described is significantly higher than the ones measured for other devices.

Table 7.

Performance under process variations.

Table 7.

Performance under process variations.

| Temp (°C) |

TT |

FF |

SS |

SF |

FS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Table 8.

Performance comparison against state-of-the-art front-ends.

Table 8.

Performance comparison against state-of-the-art front-ends.

| |

[33] |

[38] |

[39] |

[34] |

This Work |

| Year |

2016 |

2018 |

2019 |

2022 |

|

| Process |

65 nm |

180 nm |

180 nm |

180 nm |

nm |

| N° Channels |

16 |

4 |

4 |

15 |

|

| Supply (V) |

1 |

|

|

|

|

| P/Ch () |

|

|

|

|

|

| A/Ch () |

|

|

|

|

|

| NEF/PEF |

|

|

|

|

|

| SCMRR (dB) |

90 |

76 |

|

75 |

|

| PSRR (dB) |

78 |

80 |

|

74 |

|

| CMI () |

220 |

– |

– |

300 |

|

| IRN ( ) |

|

|

|

|

|

| THD (%(@ )) |

|

– |

– |

|

|