Submitted:

23 August 2024

Posted:

23 August 2024

You are already at the latest version

Abstract

Keywords:

1. Introduction

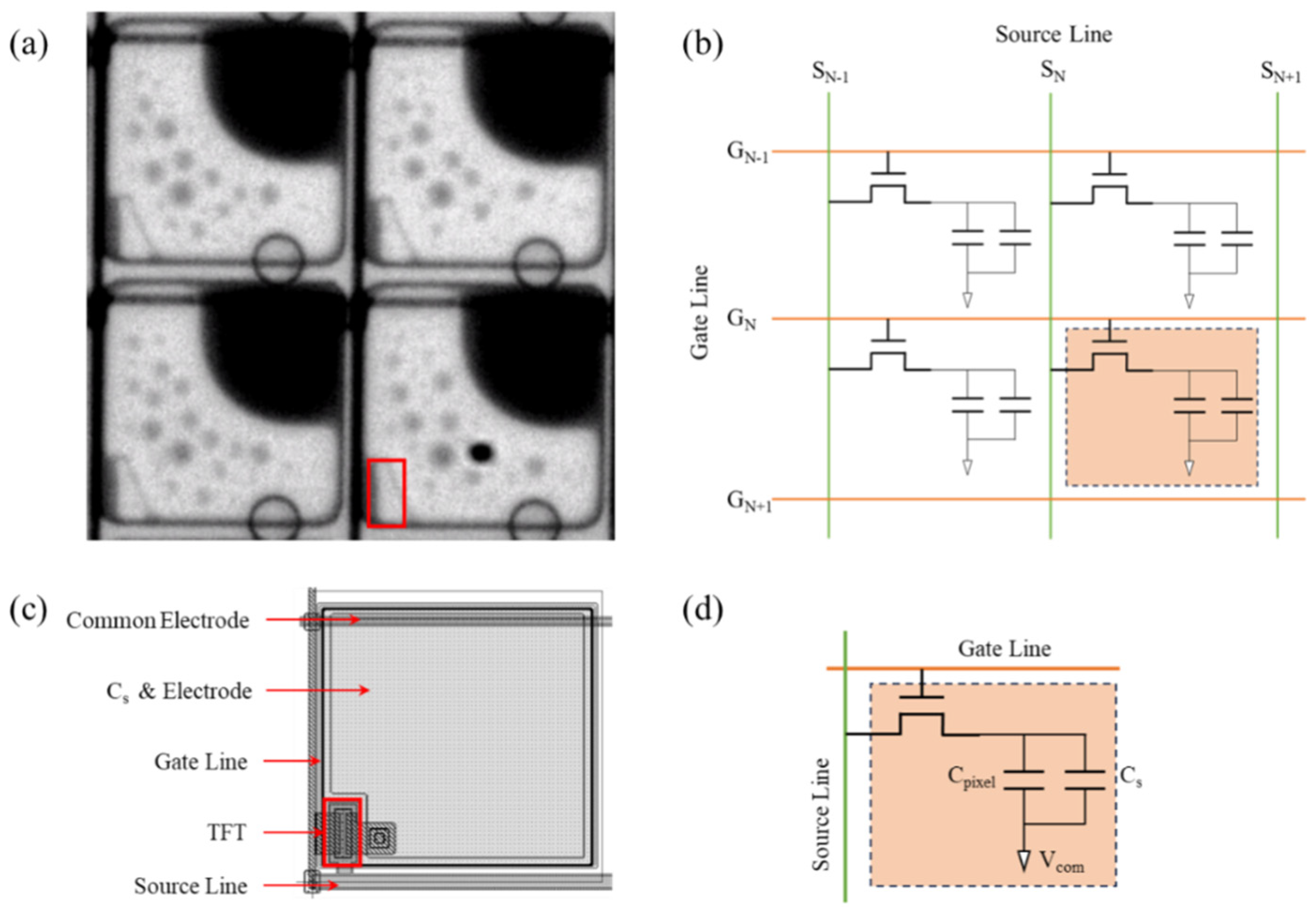

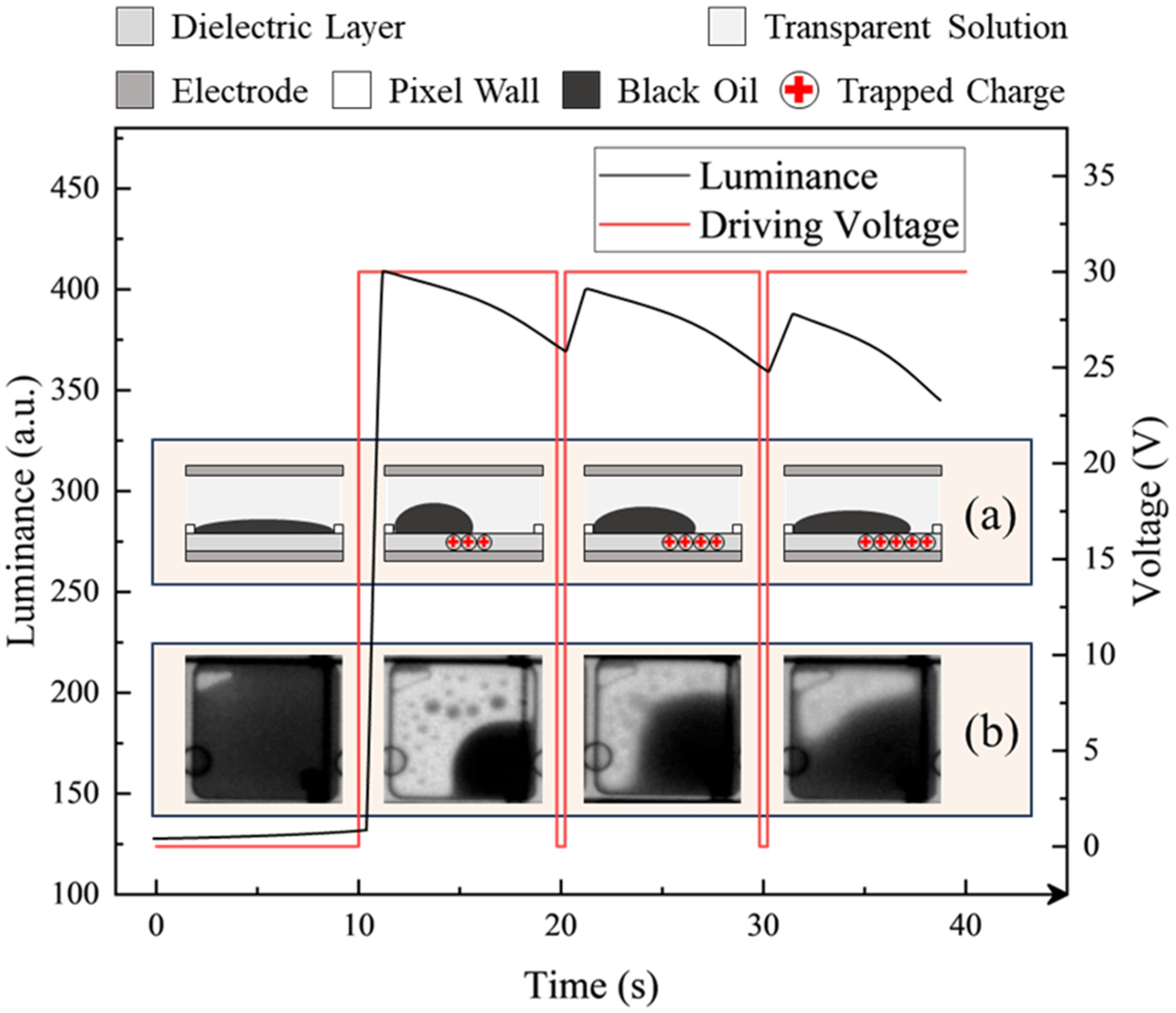

2. Oil Backflow Phenomenon in AM-EWDs

3. Experimental Methods

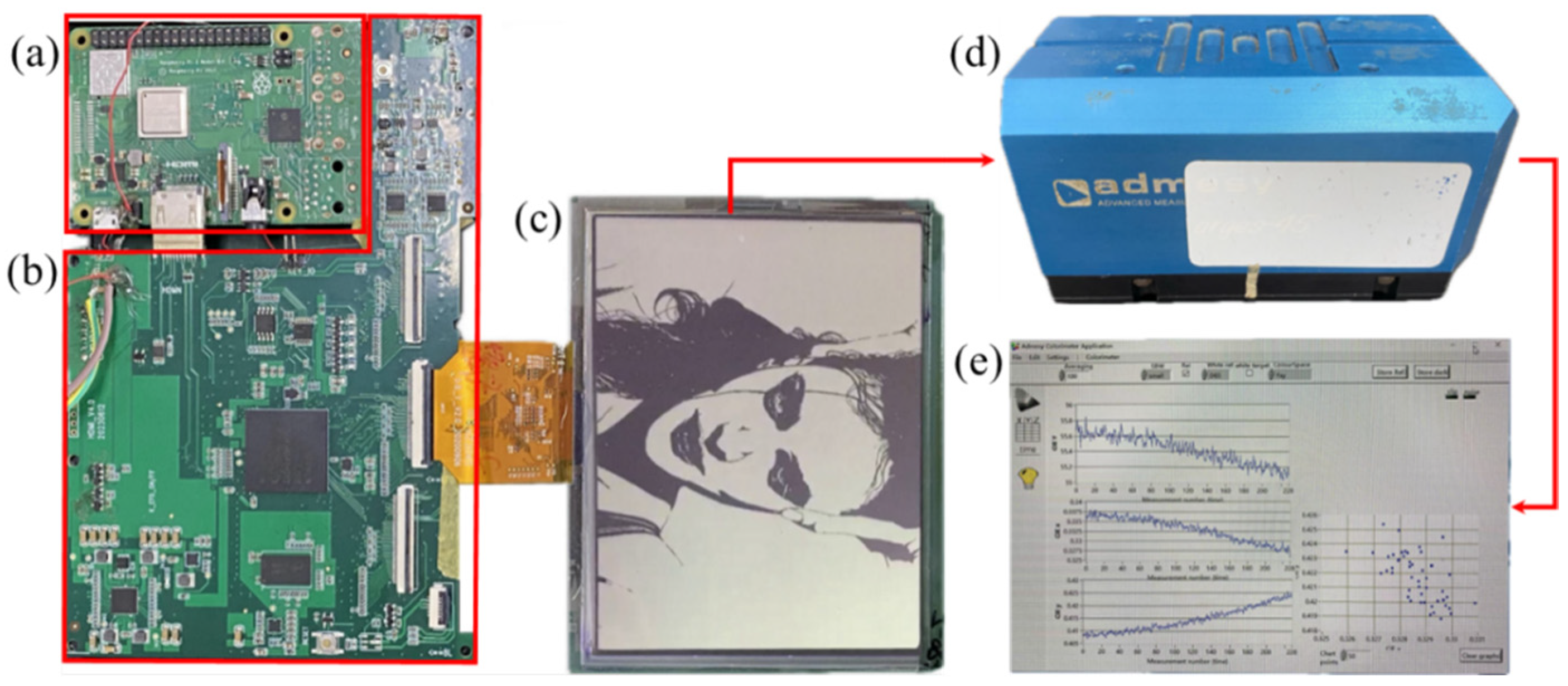

3.1. Experimental Platform

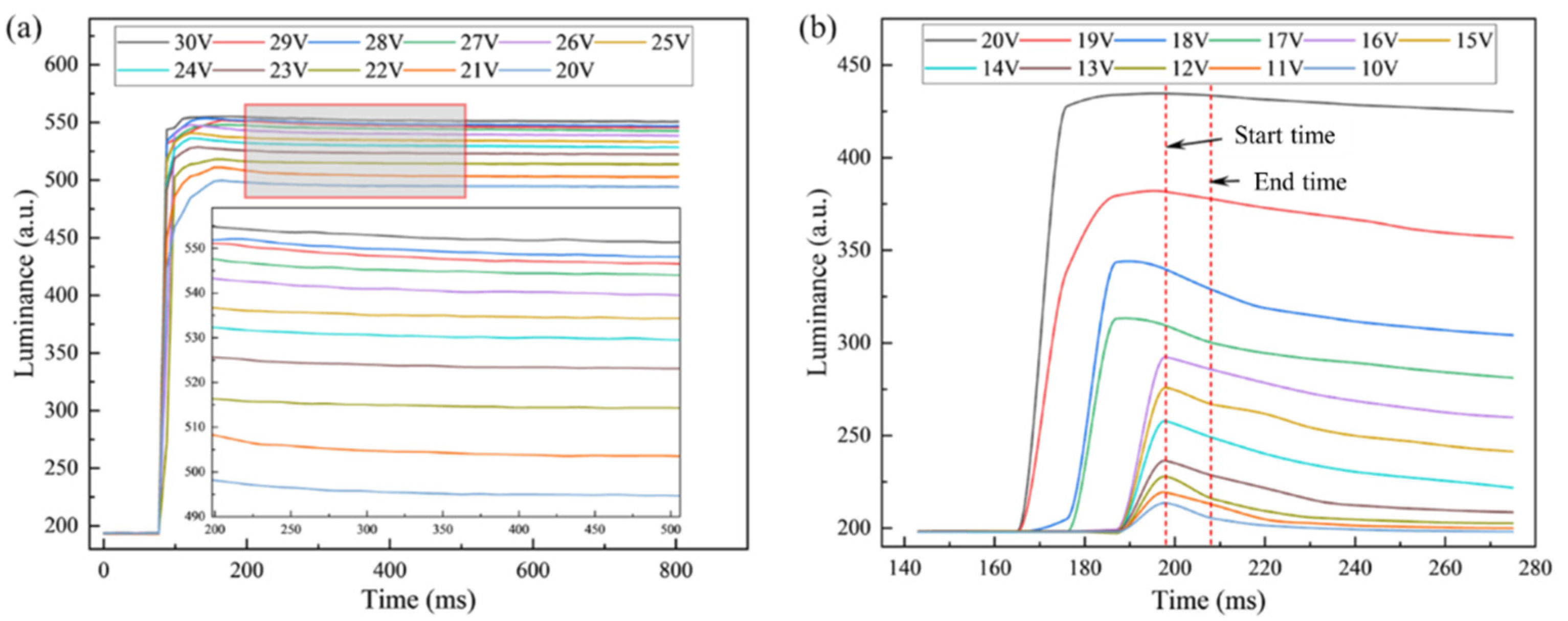

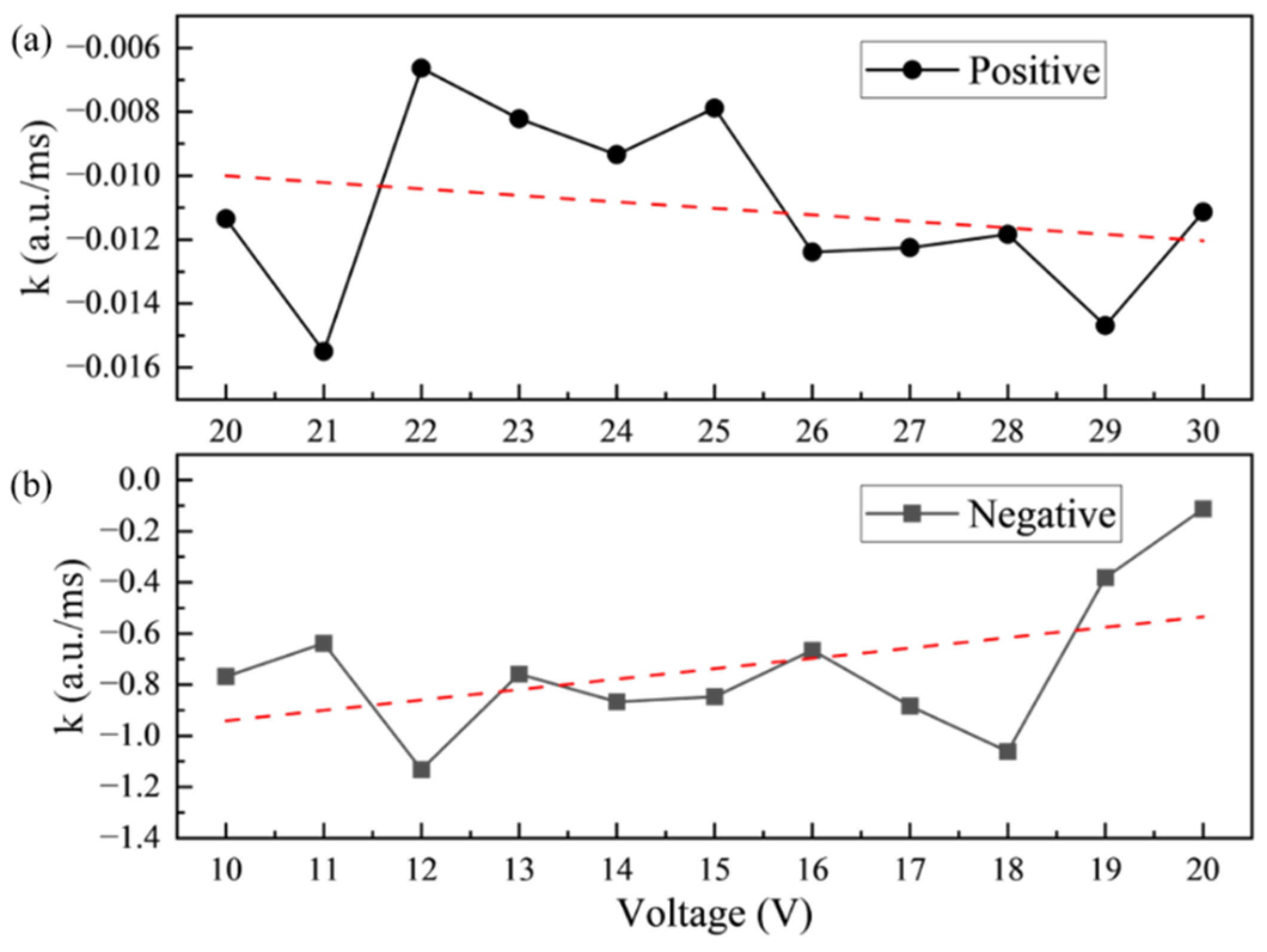

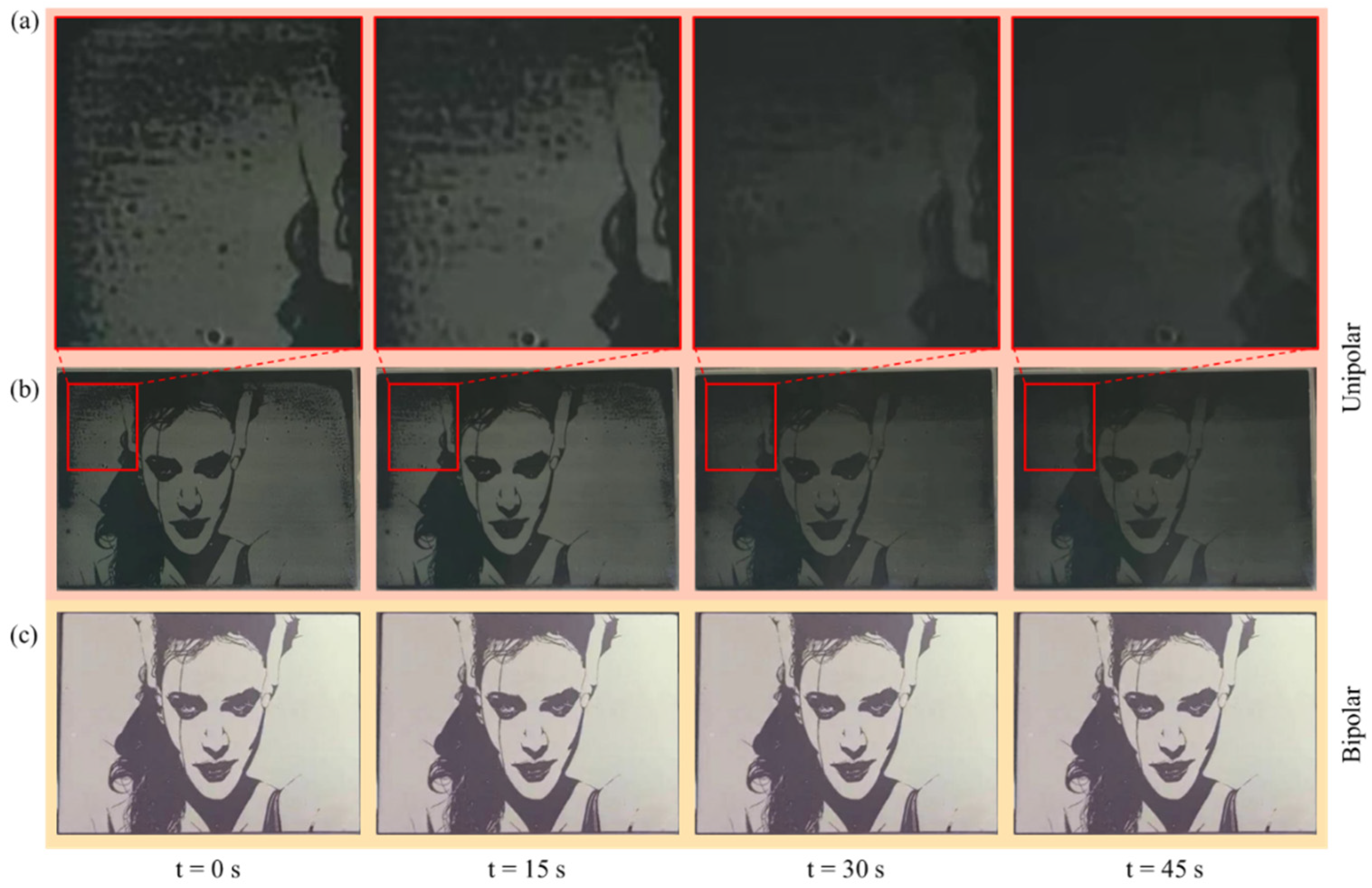

3.2. Oil Backflow under Different Voltage Polarity

3.3. Design of Driving Waveform

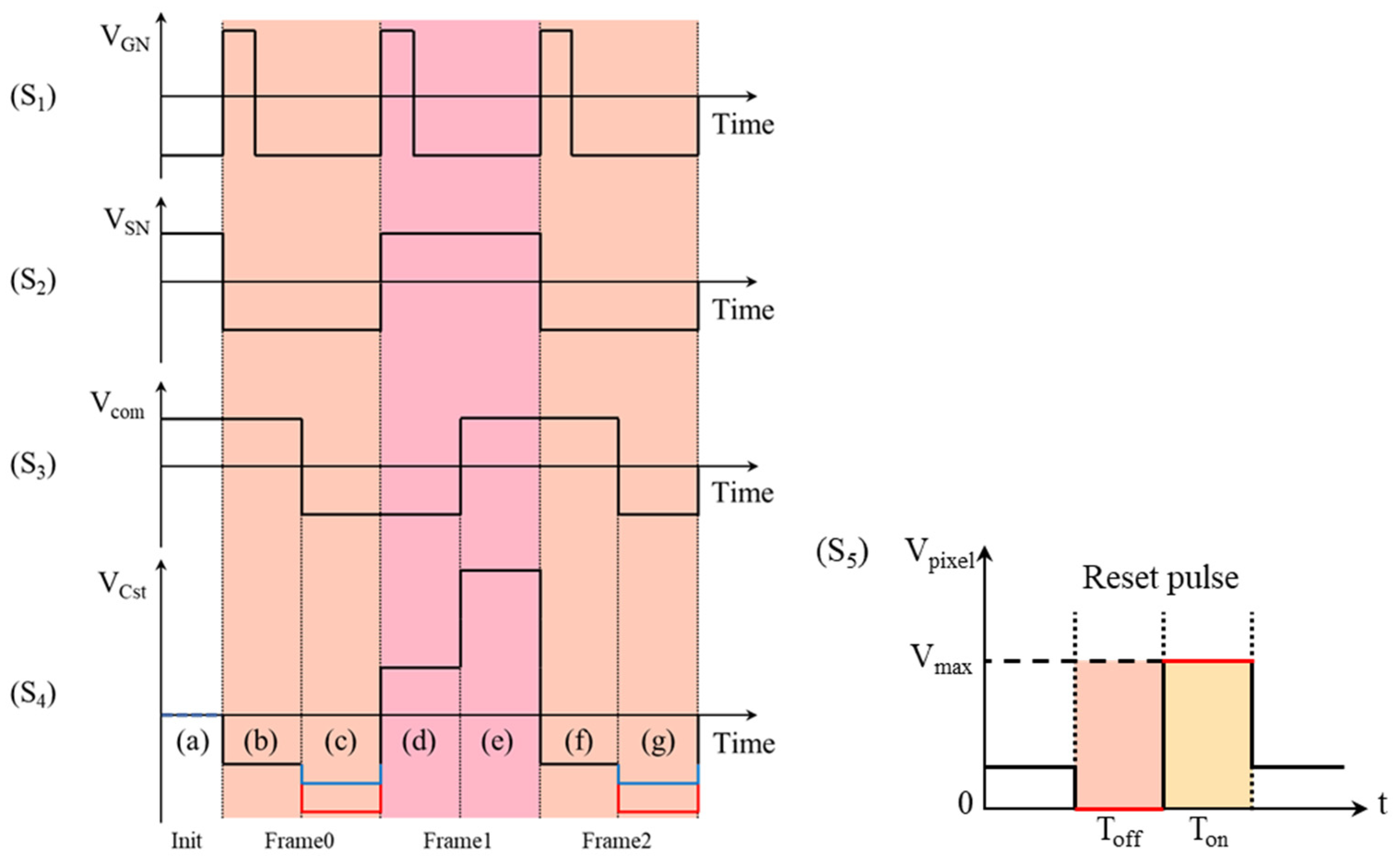

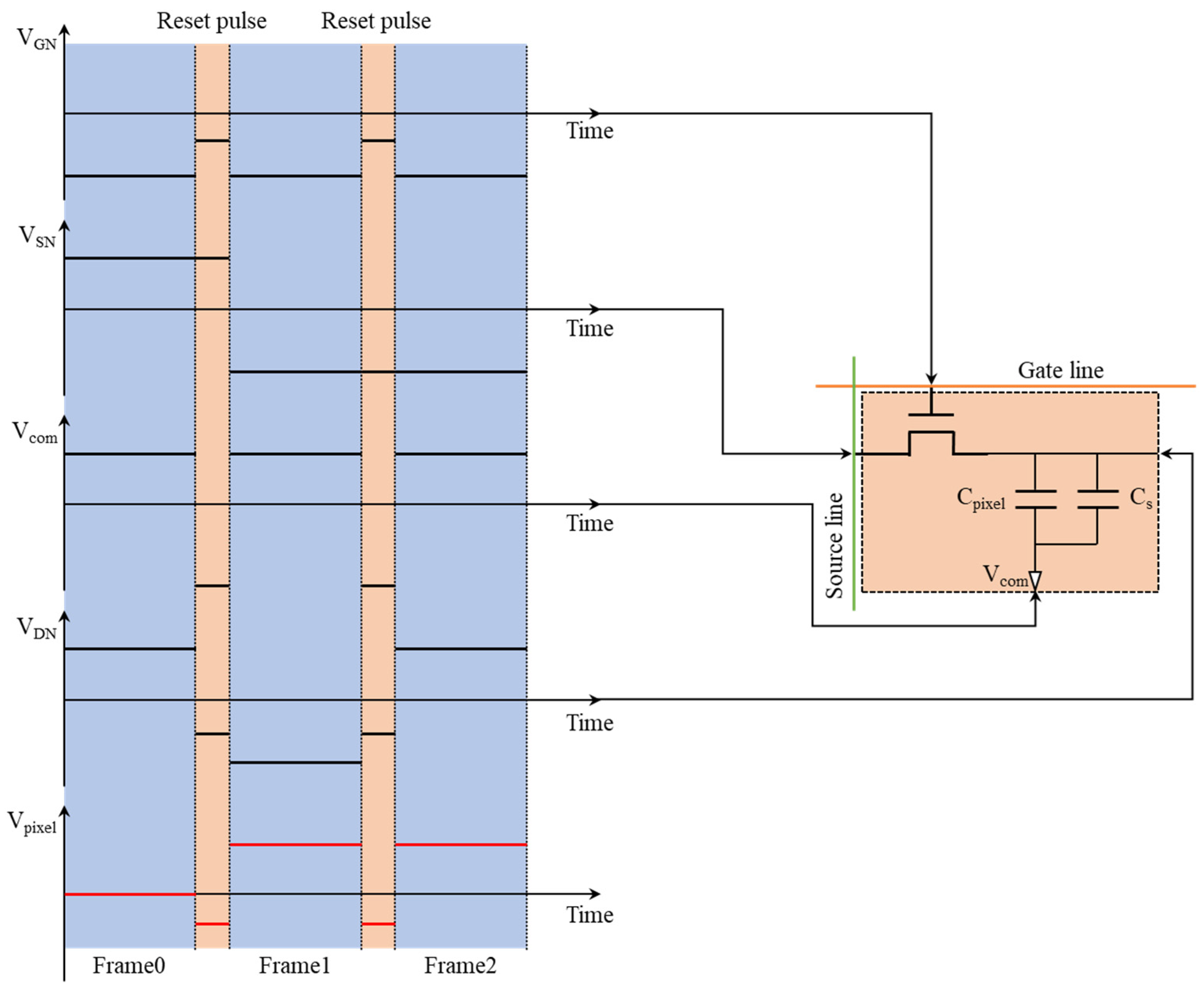

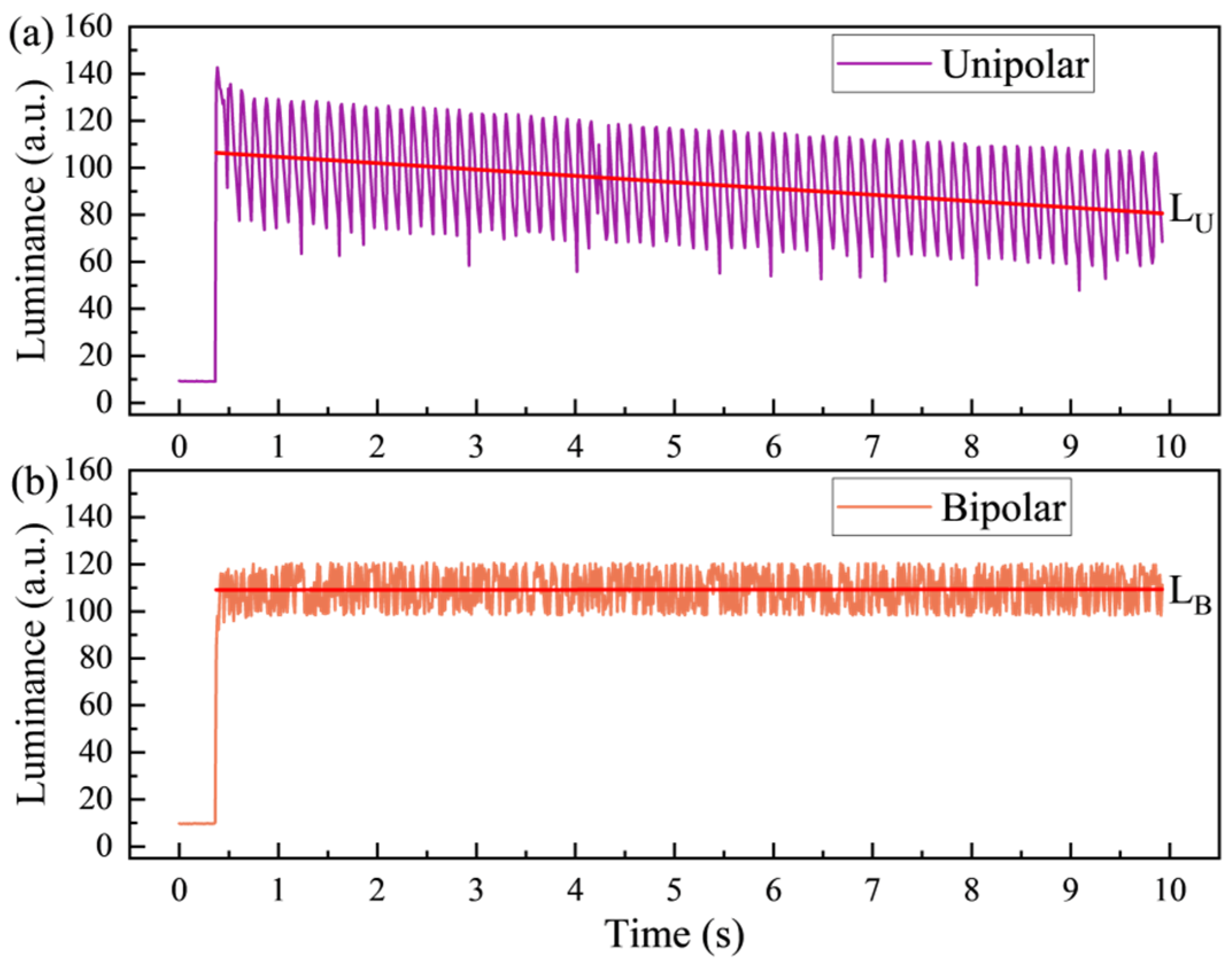

4. Experimental Methods

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Mugele, F.; Baret, J.C. Electrowetting: from basics to applications. J. Phys. Condens. Matter 2005, 17, 28. [Google Scholar] [CrossRef]

- Lo, K.L.; Kao, C.J.; Lan, K.W.; Cheng, W.Y.; Liu, T.J. Ink drop filling by a slot coating die for an electrowetting display panel. J. Soc. Inf. Display 2015, 22, 337–345. [Google Scholar] [CrossRef]

- Dai, X.Y.; Yang, J.K.; Shu, C.; Liang, Q.H.; Han, J.X.; Wu, Y.H.; Chen, M.; Cao, Y.J.; Ju, X.R.; Sun, H.L.; Huang, L.B.; Zhou, G.F. Self-Powered Colorful Dynamic Electrowetting Display Systems Based on Triboelectricity. Small 2024, 20, 2310359. [Google Scholar] [CrossRef] [PubMed]

- Zhou, R.; Ye, Q.L.; Li, H.; Jiang, H.W.; Tang, B.; Zhou, G.F. Experimental study on the reliability of water/fluoropolymer/ITO contact in electrowetting displays. Results Phys. 2019, 12, 1991–1998. [Google Scholar] [CrossRef]

- Zhao, Y.P.; Wang, Y. Fundamentals and applications of electrowetting: A critical review. Rev. Adhes. & Adhes. 2013, 1, 114–174. [Google Scholar] [CrossRef]

- Zhao, H.; Zhang, Y.Y.; Hua, D.X. A review of research progress in microfluidic bioseparation and bioassay. Micromachines 2024, 15, 893. [Google Scholar] [CrossRef]

- Wang, D.P.; Wu, S.Q.; Huang, Q.; Chan g, C.Y.; Xu, L.Q.; Jin, K.; Hu, S.Y.; Yu, J.; Ma, H.B. Active-Matrix Digital Microfluidics Design and Optimization for High-Throughput Droplets Manipulation. IEEE J. Electron Devi. 2023, 11, 411–415. [Google Scholar] [CrossRef]

- Yang, H.; Hong, S.; Koo, B.J.; Lee, D.; Kim, Y.B. High-performance reverse electrowetting energy harvesting using atomic-layer-deposited dielectric film. Nano Energy 2017, 31, 450–455. [Google Scholar] [CrossRef]

- Tan, J.; Sun, S.L.; Jiang, D.Y.; Xu, M.Y.; Chen, X.Y.; Song, Y.C.; Wang, Z.L. Advances in triboelectric nanogenerator powered electrowetting-on-dielectric devices: Mechanism, structures, and applications. Mater. Today 2022, 58, 201–220. [Google Scholar] [CrossRef]

- Clement, C.E.; Thio, S.K.; Park, S.Y. An optofluidic tunable Fresnel lens for spatial focal control based on electrowetting-on-dielectric (EWOD). Sensors Actuat. B: Chem. [CrossRef]

- Dubey, M.C.; Mohanta, D. Low voltage electrowetting microlens of two immiscible liquids. Mater. Today Proc. 2022, 66, 3412–3415. [Google Scholar] [CrossRef]

- Luo, Z.J.; Zhang, W.N.; Liu, L.W.; Xie, S.T.; Zhou, G.F. Portable multi-gray scale video playing scheme for high-performance electrowetting displays. J. Soc. Inf. Display 2016, 24, 345–354. [Google Scholar] [CrossRef]

- Mugele, F.; Klingner, A.; Buehrle, J.; Steinhauser, D.; Herminghaus, S. Electrowetting: a convenient way to switchable wettability patterns. J. Phys. Condens. Matter. 2005, 17, 9. [Google Scholar] [CrossRef]

- Hayes, R.A.; Feenstra, B.J. Video-speed electronic paper based on electrowetting. Nature 2003, 425, 383–385. [Google Scholar] [CrossRef] [PubMed]

- Li, W.; Wang, L.; Zhang, T.Y.; Lai, S.F.; Liu, L.W.; He, W.Y.; Zhou, G.F.; Yi, Z.C. Driving waveform design with rising gradient and sawtooth wave of electrowetting displays for ultra-low power consumption. Micromachines 2020, 11, 145. [Google Scholar] [CrossRef]

- Tian, L.X.; Lai, S.F.; Zhang, T.Y.; Li, W.; Tang, B.; Zhou, G.F. A multi-electrode pixel structure for quick-response electrowetting displays. Micromachines 2022, 13, 1103. [Google Scholar] [CrossRef]

- Luo, Z.J.; Fan, J.J.; Xu, J.Z.; Zhou, G.F.; Shui, L.L. A novel driving scheme for oil-splitting suppression in electrowetting display. Opt. Rev. 2020, 27, 339–345. [Google Scholar] [CrossRef]

- Chen, L.Q.; Bonaccurso, E. Electrowetting — from statics to dynamics. Adv. Colloid Interface Sci. 2014, 210, 2–12. [Google Scholar] [CrossRef] [PubMed]

- Antonis, I.D.; Athanasios, G.P.; Andreas, G.B. On the connection between dielectric breakdown strength, trapping of charge, and contact angle saturation in electrowetting. Langmuir 2009, 25, 147–152. [Google Scholar] [CrossRef]

- Massard, R.; Mans, J.; Adityaputra, A.; Leguijt, R.; Staats, C.; Giraldo, A. Colored oil for electrowetting displays. J. Soc. Inf. Display 2013, 14, 1–6. [Google Scholar] [CrossRef]

- Long, Z.X.; Yi, Z.C.; Zhang, H.; Lv, J.P.; Liu, L.M.; Chi, F.; Shui, L.L.; Zhang, C.F. Toward suppressing oil backflow based on a combined driving waveform for electrowetting displays. Micromachines 2022, 13, 948. [Google Scholar] [CrossRef]

- Buehrle, J.; Herminghaus, S.; Mugele, F. Interface profiles near three-phase contact lines in electric fields. Phys Rev Lett. 2003, 91, 086101. [Google Scholar] [CrossRef]

- Li, X.M.; Tian, H.M.; Shao, J.Y.; Ding, Y.C.; Chen, X.L.; Wang, L.; Lu, B.H. Decreasing the saturated contact angle in electrowetting-on-dielectrics by controlling the charge trapping at liquid-solid interfaces. Adv. Funct. Mater. 2016, 26, 2994–3002. [Google Scholar] [CrossRef]

- Yang, G.S.; Liu, L.W.; Zheng, Z.W.; Henzen, A.; Xi, K.R.; Bai, P.F.; Zhou, G.F. A portable driving system for high-resolution active matrix electrowetting display based on FPGA. J. Soc. Inf. Display 2019, 28, 287–296. [Google Scholar] [CrossRef]

- Verheijen, H.J.J.; Prins, M.W.J. Reversible electrowetting and trapping of charge: model and experiments. Langmuir 1999, 15, 6616–6620. [Google Scholar] [CrossRef]

- Verheijen, H.J.J.; Prins, M.W.J. Contact angles and wetting velocity measured electrically. Rev. Sci. Instrum. 1999, 70, 3668–3673. [Google Scholar] [CrossRef]

- Wang, J.S.; Yi, Z.C.; Jiang, M.H.; Xu, W.Z.; Long, Z.X.; Wan, Q.M.; Liu, L.M.; Chi, F. Driving waveform optimization of electrowetting displays based on pixel’s 2-D model for reducing oil reflux. Opt. Express 2024, 32, 28536–28551. [Google Scholar] [CrossRef]

- Yi, Z.C.; Zhang, H.; Zeng, W.J.; Feng, H.Q.; Long, Z.X.; Liu, L.M.; Hu, Y.F.; Zhou, X.C.; Zhang, C.F. Review of driving waveform for electrowetting displays. Front. Phys. 2021, 16, 728804. [Google Scholar] [CrossRef]

- Lu, Y.; Tang, B.; Yang, G.S.; Guo, Y.Y.; Liu, L.W.; Henzen, A. Progress in advanced properties of electrowetting displays. Micromachines. 2021, 12, 206. [Google Scholar] [CrossRef] [PubMed]

- Zhang, T.Y.; Deng, Y. Driving waveform design of electrowetting displays based on a reset signal for suppressing charge trapping effect. Front. Phys. 2021, 9, 672541. [Google Scholar] [CrossRef]

- Chiu, Y.H.; Liang, C.C.; Chen, Y.C.; Lee, W.Y.; Chen, H.Y.; Wu, S.H. Accurate-gray-level and quick-response driving methods for high-performance electrowetting displays. J. Soc. Inf. Display 2011, 19, 741–748. [Google Scholar] [CrossRef]

- Liu, L.W.; Bai, P.F.; Yi, Z.C.; Zhou, G.F. A separated reset waveform design for suppressing oil backflow in active matrix electrowetting displays. Micromachines 2021, 12, 491. [Google Scholar] [CrossRef] [PubMed]

- Li, S.X.; Xu, Y.J.; Zhan, Z.Y.; Liu, L.W.; Bai, P.F. A high integration electrowetting displays system based on AC driving model. Front. Phys. 2022, 10, 1033076. [Google Scholar] [CrossRef]

- Khanna, M.R.; Roy, S.; Mathur, A.; Dubey, A.K.; Vashisth, R. Analysis of voltage distribution in electrowetting on Dielectric (EWOD) system. Mater. Today Proc. 2021, 38, 179–185. [Google Scholar] [CrossRef]

| Parameters | Value | Unit |

|---|---|---|

| panel size | 6 | inch |

| resolution | 648*480 | px*px |

| width of pixel wall | 12 | um |

| height of pixel wall | 6 | um |

| thickness of dielectric layer | 1 | um |

| thickness of ITO | 25 | um |

| Parameters | Symbol | Value | Unit |

|---|---|---|---|

| voltage of gate electrode | VGH | 20 | V |

| VGL | -20 | V | |

| voltage of source electrode | VSH | 15 | V |

| VSL | -15 | V | |

| voltage of common electrode | VCOM | 15 | V |

| storage capacitance | Cs | 1. 455 | pF |

| pixel capacitance | Cpixel | 0.14-0.45 | pF |

| parasitic capacitance | Cgd | 0.08 | pF |

| Cgs | 0.045 | pF | |

| Cgp | 0.02 | pF |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).