Submitted:

20 September 2024

Posted:

24 September 2024

You are already at the latest version

Abstract

Keywords:

1. Introduction

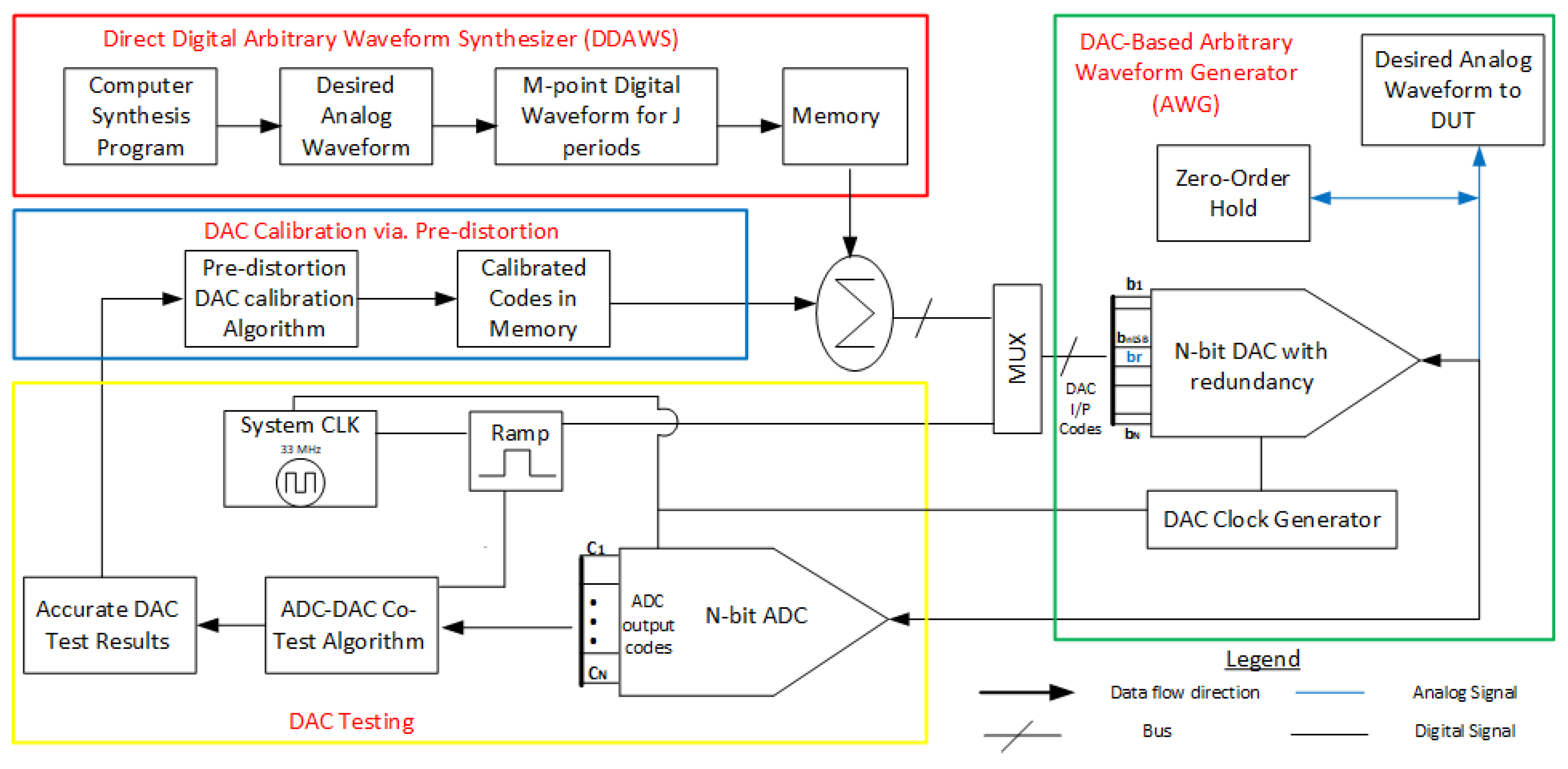

2. Data Converter Testing Based Approach to Waveform Generation

3. Proposed Signal Generator

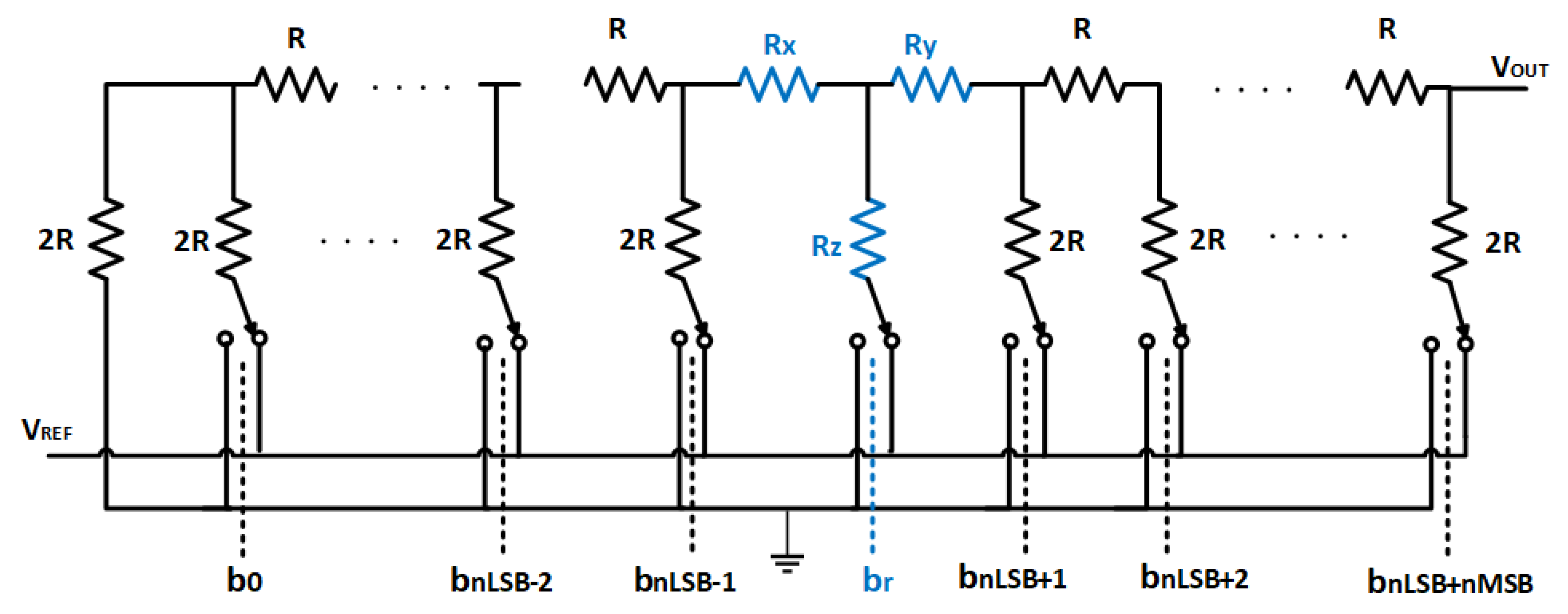

3.1. R-2R DAC with Redundancy

3.2. ADC Model

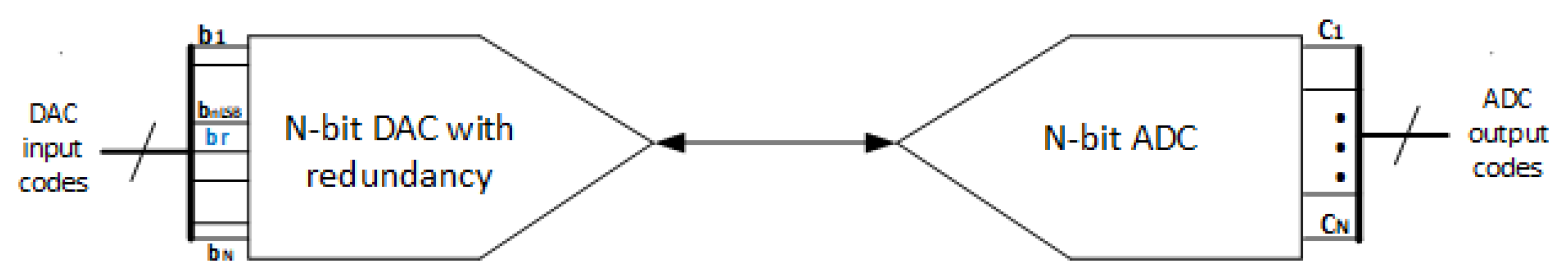

3.3. ADC DAC Simultaneous Test Scheme

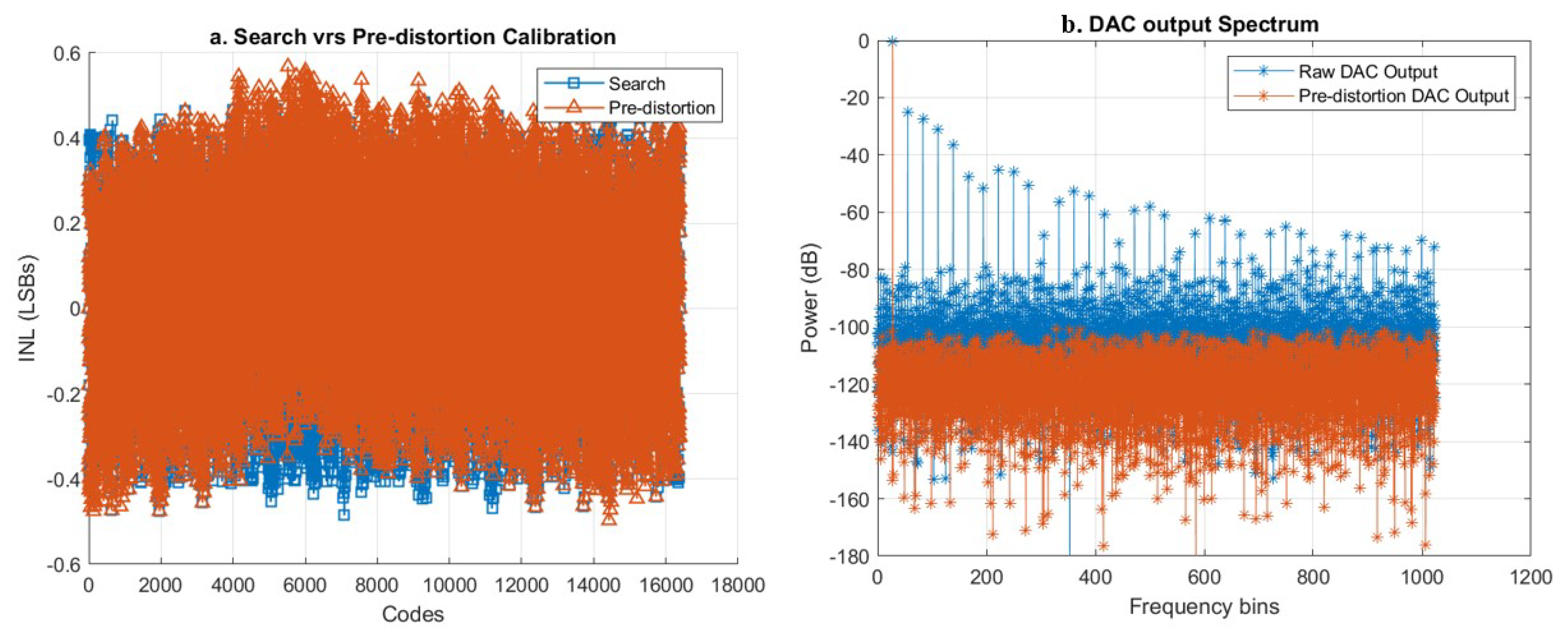

3.4. DAC Calibration via Pre-Distortion

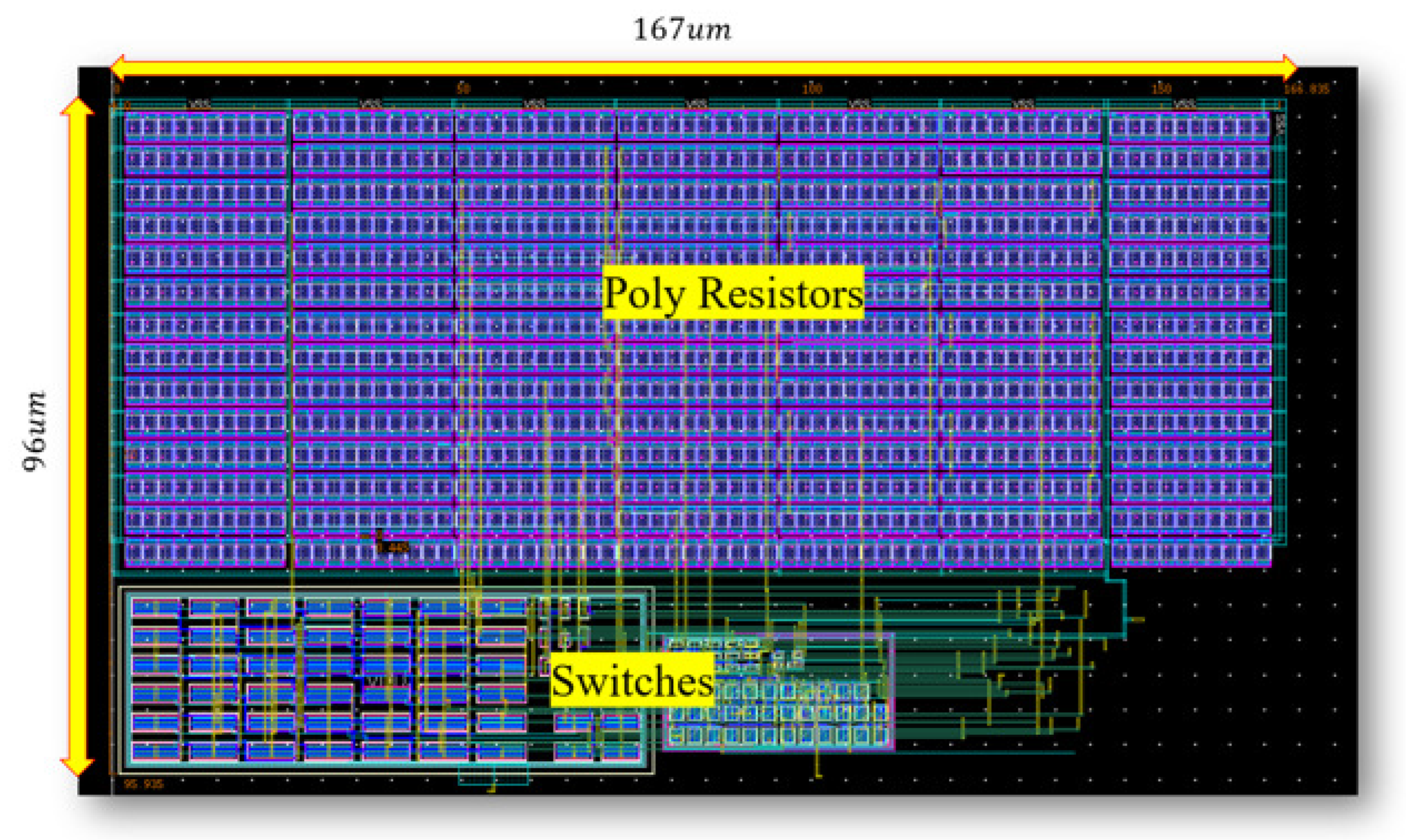

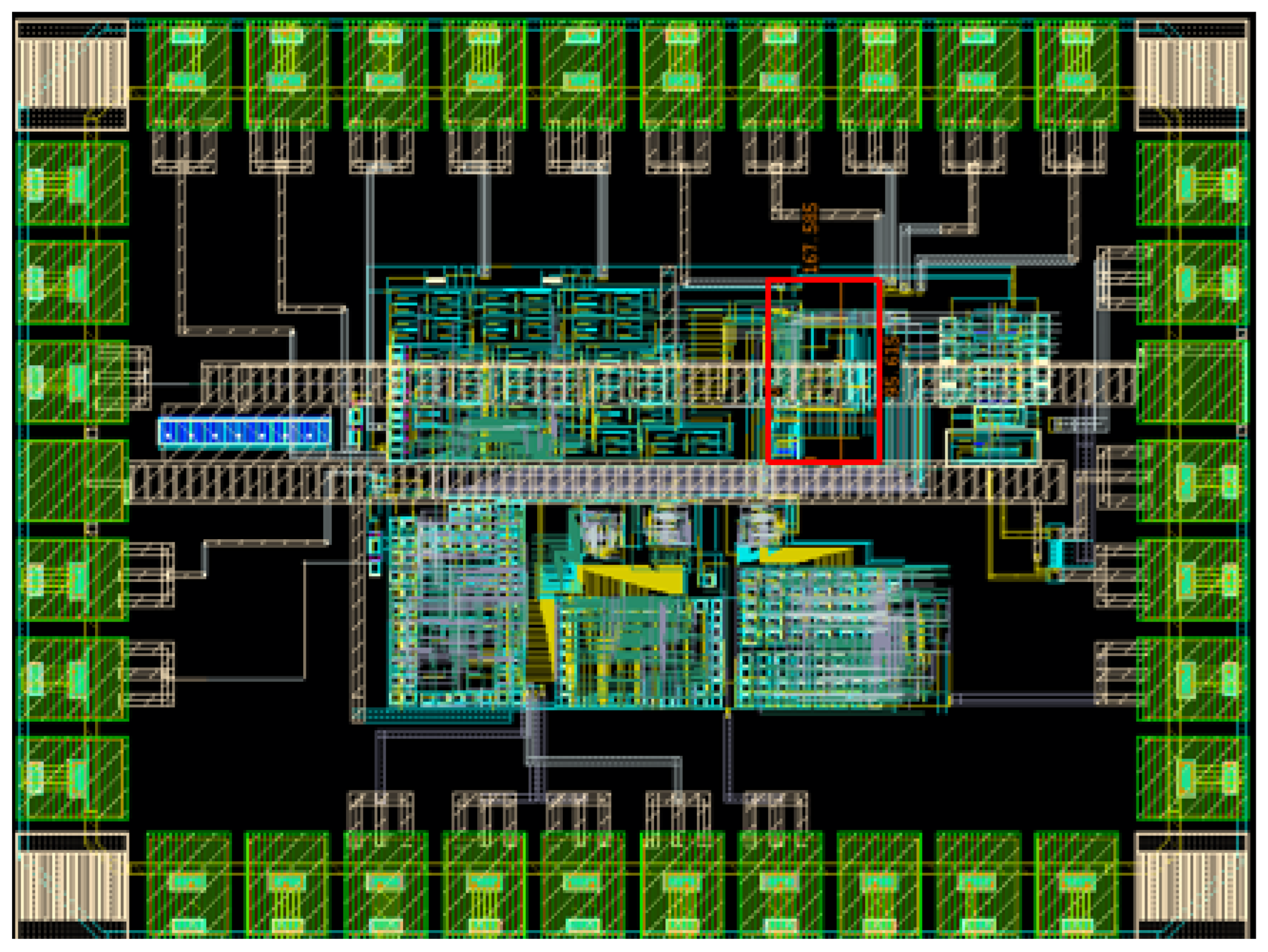

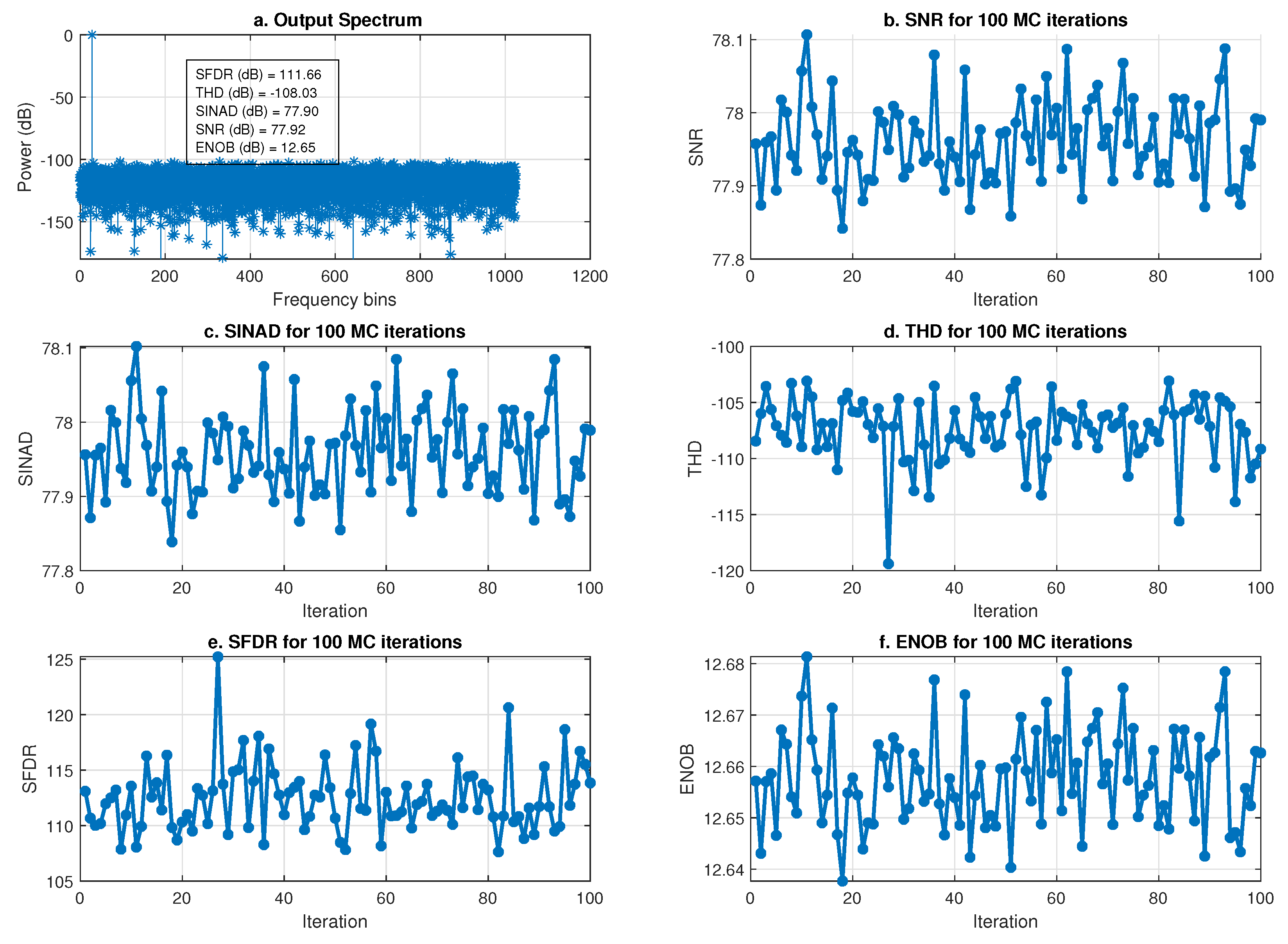

4. Implementation and Results

5. Discussions

6. Conclusions

Funding

Data Availability Statement

Conflicts of Interest

References

- Burns, M.; Roberts, G.W. An Introduction to Mixed-Signal IC Test and Measurement. Oxford University Press, 2000.

- Pavlidis, A.; Louërat, M.-M.; Faehn, E.; Kumar, A.; Stratigopoulos, H.-G. SymBIST: Symmetry-Based Analog and Mixed-Signal Built-In Self-Test for Functional Safety. IEEE Transactions on Circuits and Systems I: Regular Papers 2021, 68, 2580–2593. [CrossRef]

- Mishra, P.; Farahmandi, F. Post-Silicon Validation and Debug. Springer, 2019, 301.

- Brindley, K. Automatic Test Equipment. Elsevier, Amsterdam, The Netherlands, 2013, October.

- R. R. Cordesses and B. Murmann, "Analog-to-Digital Converter Testing," in Maxim Integrated Application Note 6803, 2014. [Online]. Available: https://www.maximintegrated.com.

- "IEEE Standard for Terminology and Test Methods for Analog-to-Digital Converters," IEEE Std 1241-2010 (Revision of IEEE Std 1241-2000), pp.1-139, Jan. 14, 2011, . [CrossRef]

- Maeda, A. A Method to Generate a Very Low Distortion, High Frequency Sine Waveform Using an AWG. In Proceedings of the 2008 IEEE International Test Conference, Santa Clara, CA, USA, 2008, pp. 1–8. [CrossRef]

- Vasan, B. K.; Sudani, S. K.; Chen, D. J.; Geiger, R. L. Low-Distortion Sine Wave Generation Using a Novel Harmonic Cancellation Technique. IEEE Transactions on Circuits and Systems I: Regular Papers 2013, 60, 1122–1134. [CrossRef]

- Malloug, H.; Barragan, M. J.; Mir, S. Practical harmonic cancellation techniques for the on-chip implementation of sinusoidal signal generators for mixed-signal BIST applications. J. Electron. Test. 2018, 34, 263–279. [CrossRef]

- Sato, K.; et al. Low Distortion Sinusoidal Signal Generator with Harmonics Cancellation Using Two Types of Digital Pre-distortion. In Proceedings of the 2023 IEEE International Test Conference (ITC), Anaheim, CA, USA, 2023, pp. 47–55. [CrossRef]

- Katayama, S.; et al. Low Distortion Sine Wave Generator With Simple Harmonics Cancellation Circuit and Filter for Analog Device Testing. IEICE Electronics Express 2023, 20, 20220470.

- Elsayed, M. M.; Sanchez-Sinencio, E. A Low THD, Low Power, High Output-Swing Time-Mode-Based Tunable Oscillator Via Digital Harmonic-Cancellation Technique. IEEE Journal of Solid-State Circuits 2010, 45, 1061–1071. [CrossRef]

- Suryavanshi, R.; Sridevi, S.; Amrutur, B. A comparative study of direct digital frequency synthesizer architectures in 180nm CMOS. In Proceedings of the 2017 International Conference on Microelectronic Devices, Circuits and Systems (ICMDCS), Vellore, India, 2017, pp. 1–5. [CrossRef]

- Ryabov, I. V. Pryamoy tsifrovoy sintez signalov dlya zadach radiolokatsii, navigatsi i svyazi [Direct Digital Synthesis of Signals for Tasks of Radiolocation, Navigation and Communication]. Yoshkar-Ola: VSUT, 2016, 151 p.

- Bochkarev, D. N.; Ryabov, I. V.; Strelnikov, I. V.; Degtyarev, N. V. Direct Digital Synthesizers of Frequency and Phase-Modulated Signals. In Proceedings of the 2019 Systems of Signal Synchronization, Generating and Processing in Telecommunications (SYNCHROINFO), Russia, 2019, pp. 1–4. [CrossRef]

- Strelnikov, I. V.; Ryabov, I. V.; Klyuzhev, E. S. Direct Digital Synthesizer of Phase-Manipulated Signals, Based on the Direct Digital Synthesis Method. In Proceedings of the 2020 Systems of Signal Synchronization, Generating and Processing in Telecommunications (SYNCHROINFO), Svetlogorsk, Russia, 2020, pp. 1–3. [CrossRef]

- Irfansyah, A. Sine wave synthesis with harmonic-cancellation and single-bit sigma-delta modulation. In Proceedings of the International Symposium on Electronics Smart Devices (ISESD), Oct. 2017, pp. 150–153.

- Huang, J.; Zhou, T.; Liu, H.; Qi, L.; Yan, L.; Li, Y. Low Noise, High Linearity Sine Wave Generation Using Noise-Shaping Phase-Switching Technique. IEEE Transactions on Instrumentation and Measurement 2021, . [CrossRef]

- IEEE Standard for Digitizing Waveform Recorders. IEEE Std 1057-2017 (Revision of IEEE Std 1057-2007) 2018, pp. 1–0. [CrossRef]

- Zhuang, Y.; Unnithan, A.; Joseph, A.; Sudani, S.; Magstadt, B.; Chen, D. Low cost ultra-pure sine wave generation with self calibration. In Proceedings of the 2016 IEEE International Test Conference (ITC), Phoenix, AZ, USA, 2016, pp. 1–9. [CrossRef]

- Zhuang, Y.; Magstadt, B.; Chen, T.; Chen, D. High-Purity Sine Wave Generation Using Nonlinear DAC With Predistortion Based on Low-Cost Accurate DAC–ADC Co-Testing. IEEE Transactions on Instrumentation and Measurement 2018, 67, 279–287. [CrossRef]

- Bhatheja, K.; et al. Low Cost High Accuracy Stimulus Generator for On-chip Spectral Testing. In Proceedings of the 2022 IEEE International Test Conference (ITC), Anaheim, CA, USA, 2022, pp. 514–518. [CrossRef]

- M. J. M. Pelgrom, A. C. J. Duinmaijer, and A. P. G. Welbers, "Matching properties of MOS transistors," in IEEE Journal of Solid-State Circuits, vol. 24, no. 5, pp. 1433-1439, Oct. 1989, . [CrossRef]

- M. Pelgrom, Analog-to-Digital Conversion, Cham: Springer International Publishing, 2017.

- M. P. Kennedy, "On the robustness of R-2R ladder DACs," in IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, vol. 47, no. 2, pp. 109-116, Feb. 2000, . [CrossRef]

- T. Bharath, R. Narula, and P. Tadeparthy, "Generalized Resistive DAC Analysis Through Unitized T-Network Element," in 2022 IEEE International Symposium on Circuits and Systems (ISCAS), Austin, TX, USA, 2022, pp. 2797-2801, . [CrossRef]

- Bhatheja, K.; Chaganti, S.; Leisinger, J.; Darko, E. N.; Bruce, I.; Chen, D. A BIST Approach to Approximate Co-Testing of Embedded Data Converters. IEEE Design & Test 2024. [CrossRef]

- Sekyere, M.; Darko, E. N.; Bruce, I.; Odion, E. O.; Bhatheja, K.; Chen, D. Ultra-Small Area, Highly Linear Sub-Radix R-2R Digital-To-Analog Converters with Novel Calibration Algorithm. In Proceedings of the 2023 IEEE 66th International Midwest Symposium on Circuits and Systems (MWSCAS), Tempe, AZ, USA, 2023, pp. 604–608. [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).