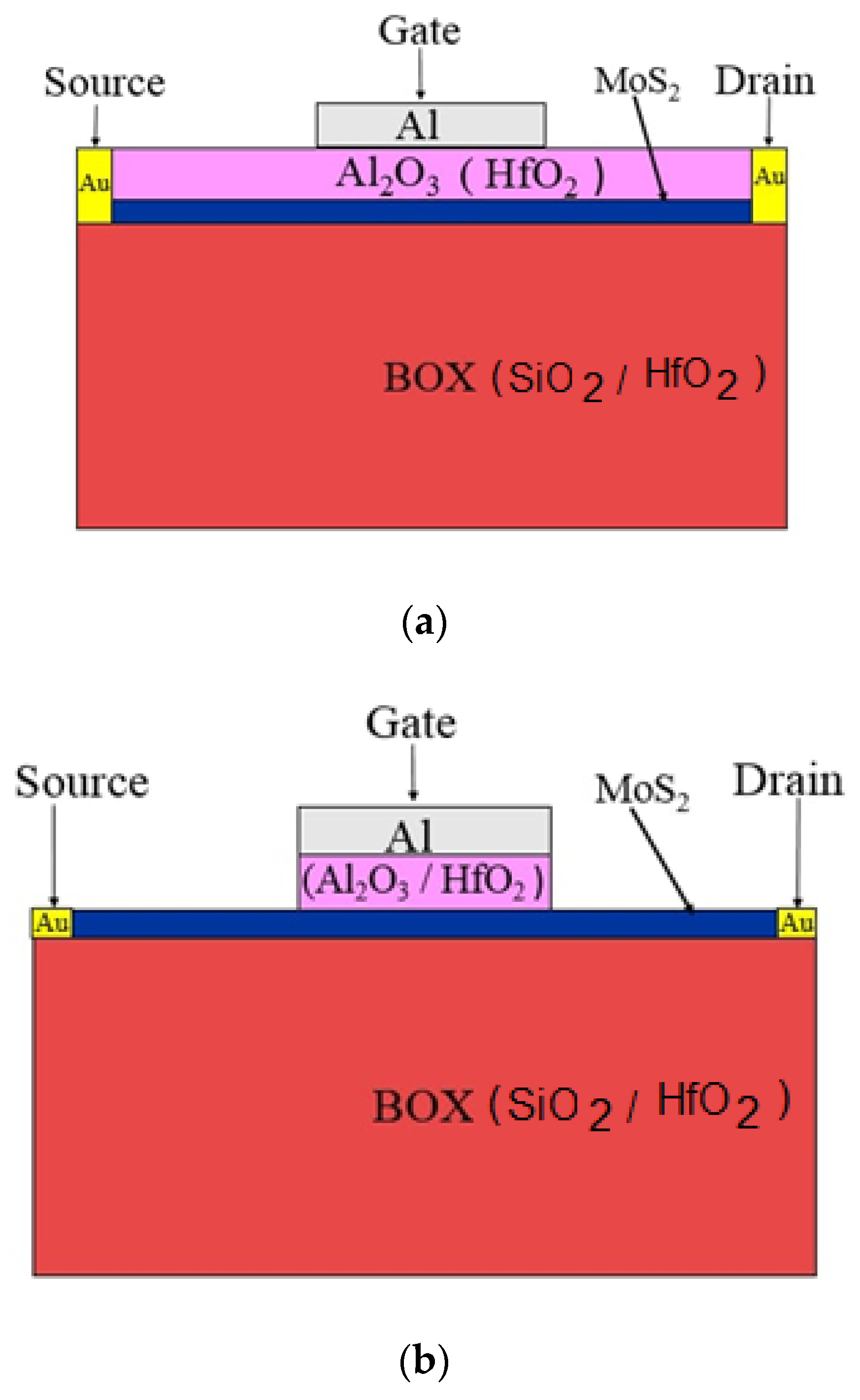

3.1. SHE for different combinations of the gate oxide and back oxide materials

One of the main parameters of the SHE effect is the temperature in the center of the channel. The resulting temperature in the center of the channel is defined by the heat generation rate as well as by the rate of heat dissipation through the oxide surrounding the channel. In this study we will consider only heat dissipation, having assumed that heat generation is similar in all considered cases. The heat generation rate similarity is provided by choice of the appropriately applied voltages at the gate and drain. The resulting heat dissipation rate is defined by the configuration of the transistor structure as well as by oxide materials surrounding the channel. Different structures are presented in the two cases mentioned above and using the different oxide materials are presented by combinations from 1 to 4 shown in

Table 1.

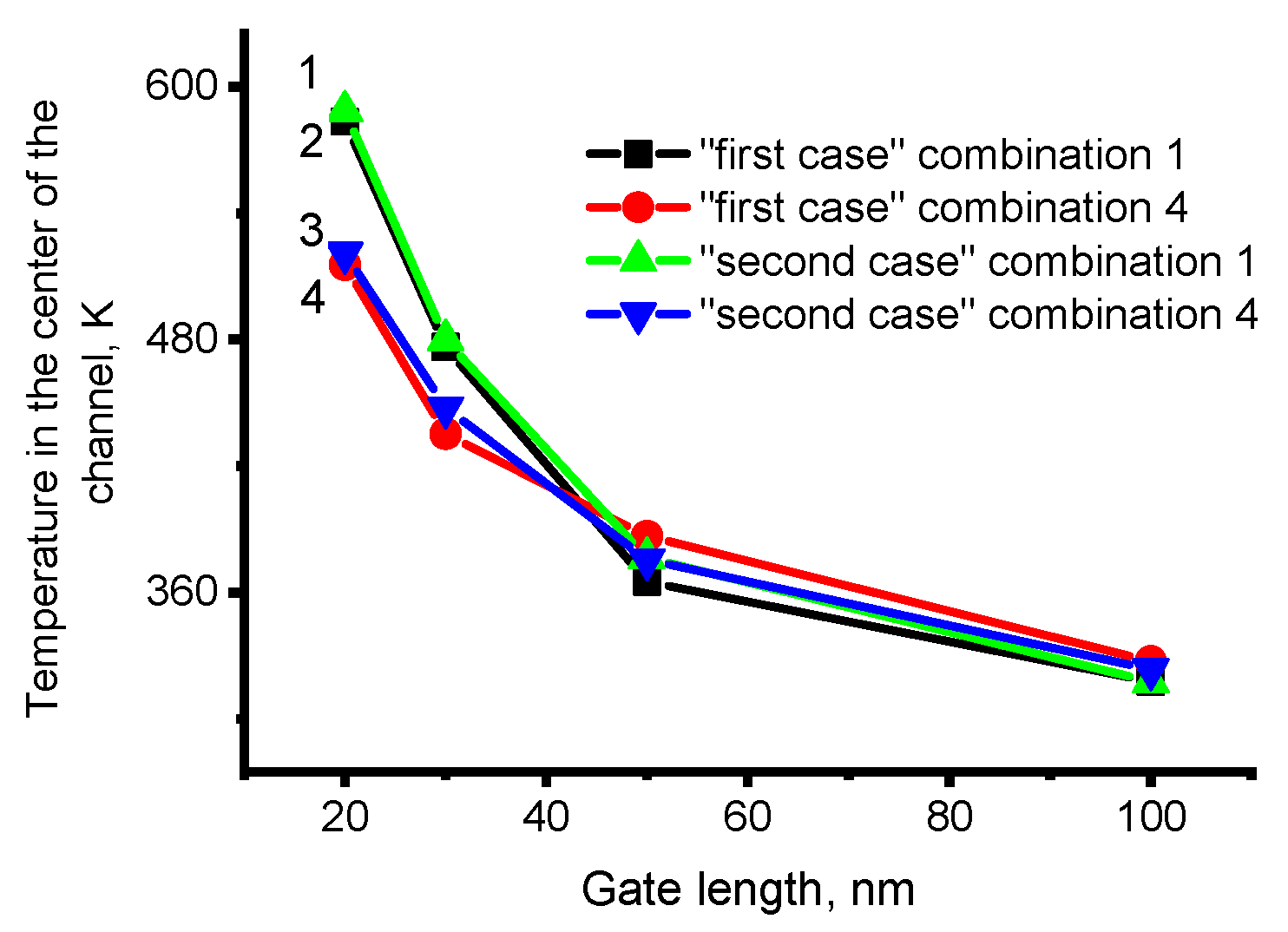

Results of the simulation of the lattice temperature dependence of the gate length in the middle of the channel for case 1 (fully covered channel top surface) and case 2 (partly covered channel top surface) are shown in

Figure 3.

For all transistors, the temperature distributions along the channel were simulated at the same gate and drain voltages: Vg = 0.1 V and Vd = 0.4 V. Therefore, the drain current for long-channel transistors is lower than for short-channel transistors. This results in a higher mid-channel temperature for short-channel transistors than for long-channel transistors. The more significant role of the heat generation rate is observed in short-channel transistors, where for both cases and for both combinations the mid-channel temperature is higher. Besides it, the resulting temperature depends on the transistor structure (case 1 and case 2) as well as gate oxide and BOX materials (combinations 1 and 4).

With a gate length of less than 40 nm, for both 1 and 4 combinations, the lattice temperature in the middle of the channel is slightly higher for transistors where the channel is covered by gate oxide only under the gate (second case) than for transistors of the first case. This is related to the quite different thermal conductivity of gate oxide materials and air covering the upper part of the channel not covered by the gate oxide (

Figure 2b). The thermal conductivity of air has values from 0.0084 to 0.0915 W/(m K) in the temperature range between 90 K and 1473 K, the thermal conductivity of aluminum- and hafnium- oxide is 2-3 orders of magnitude higher than the thermal conductivity of air.

At increasing a gate length of more than 40 nm relations between a mid-channel temperature for transistors of combination 1 and 4 are changed: the temperature for transistors of the first case became higher than for transistors of the second case. It means that the impact of oxide materials in establishing the resulting temperature is increased for the long-channel transistors in comparison with the impact of the transistor structure.

For long-channel transistors, the temperature tends to be equal for all types of considered transistor structures. In this case, it is observed more sufficient role in the heat generation rate than the heat dissipation rate, because the resulting temperature is the same for both structures (case 1 and case 2) and for both combinations 1 and 4.

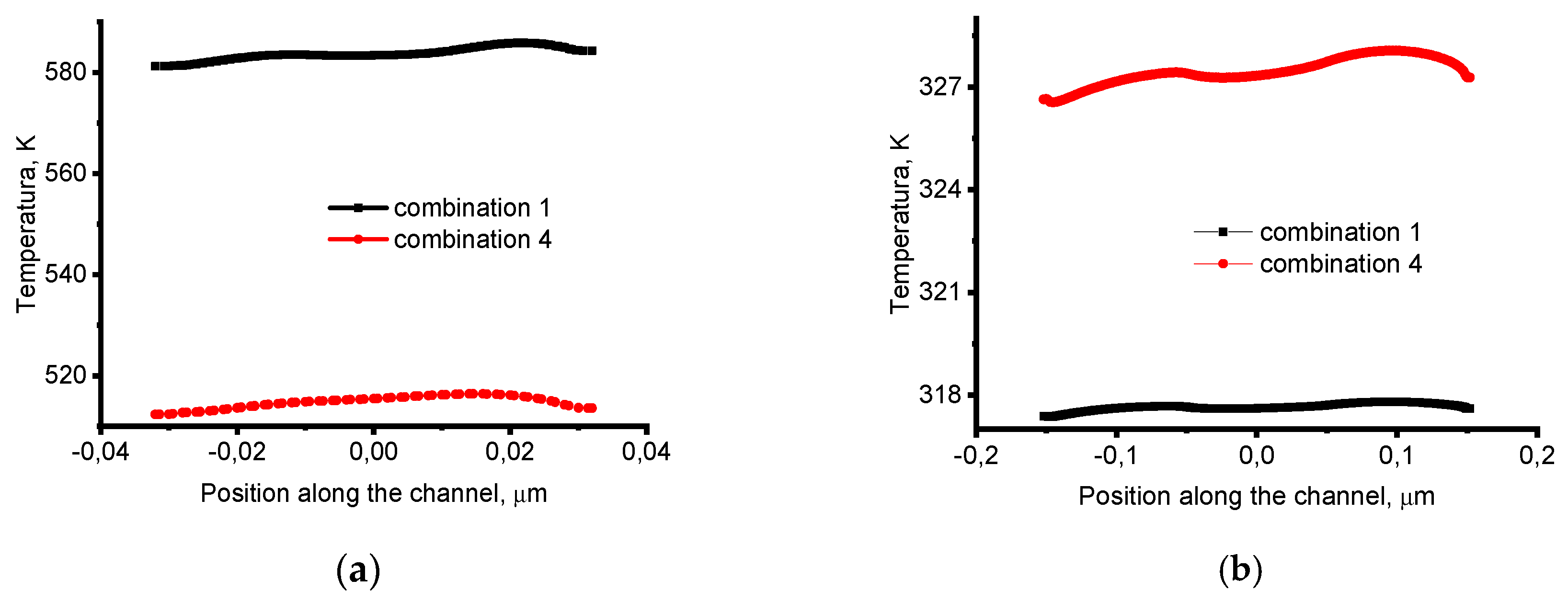

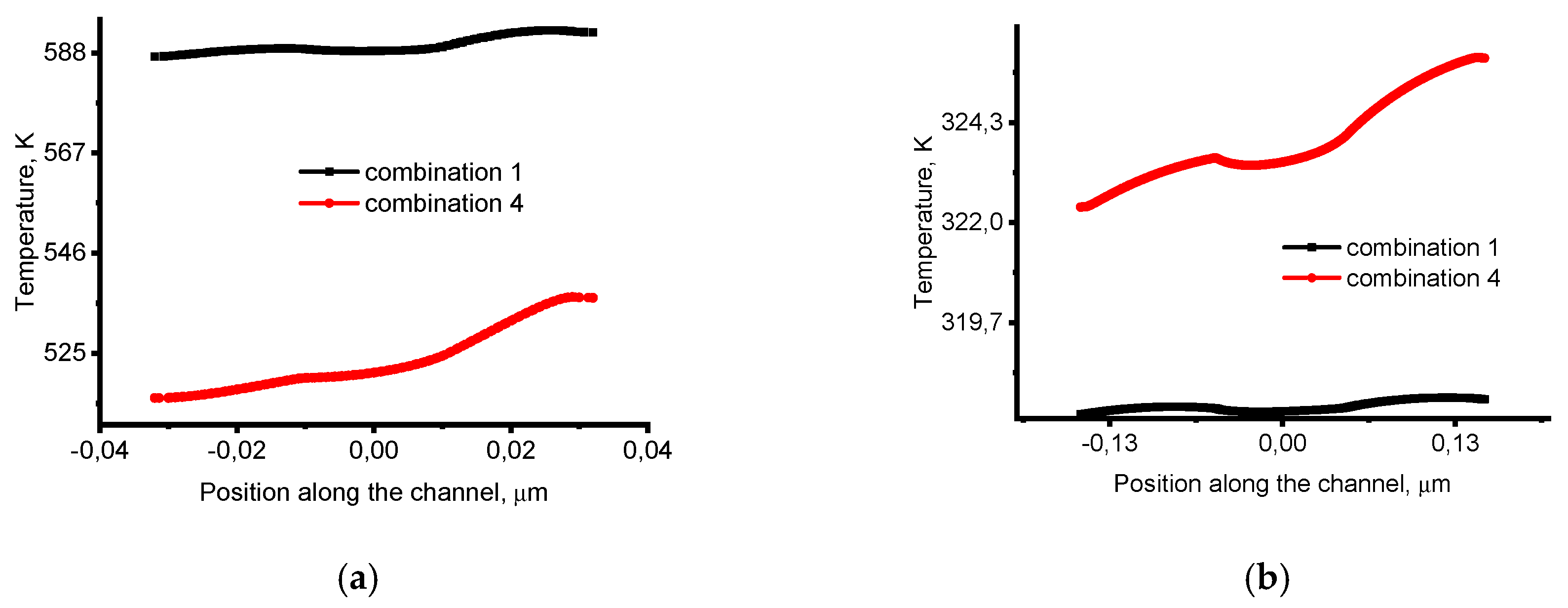

From the distribution of temperature along the channel for case 1 (fully covered channel top surface) and case 2 (partly covered channel top surface), it can be seen that with the same applied gate and drain voltages, the temperature change, when lengthening the gate, is higher for the transistor with combination number one than for transistor with combination number four (

Table 1) (

Figure 4 and

Figure 5). Change of the mid-channel temperature is 264 K and 192 K in the first case, 270 K and 194 K in the second case for combinations 1 and 4 respectively. Apparently, this is mainly related to the higher thermal conductivity of Al

2O

3 compared to the thermal conductivity of HfO

2 (

Table 2) used as gate oxide materials in combinations number one and four, respectively. Although the thermal conductivity of SiO

2 used as BOX material in transistor combination number one is lower than the thermal conductivity of HfO

2 used as BOX material in combination number four, it differs only by 1.5- fold, while the thermal conductivity of gate oxide materials is approximately five times different (

Table 2).

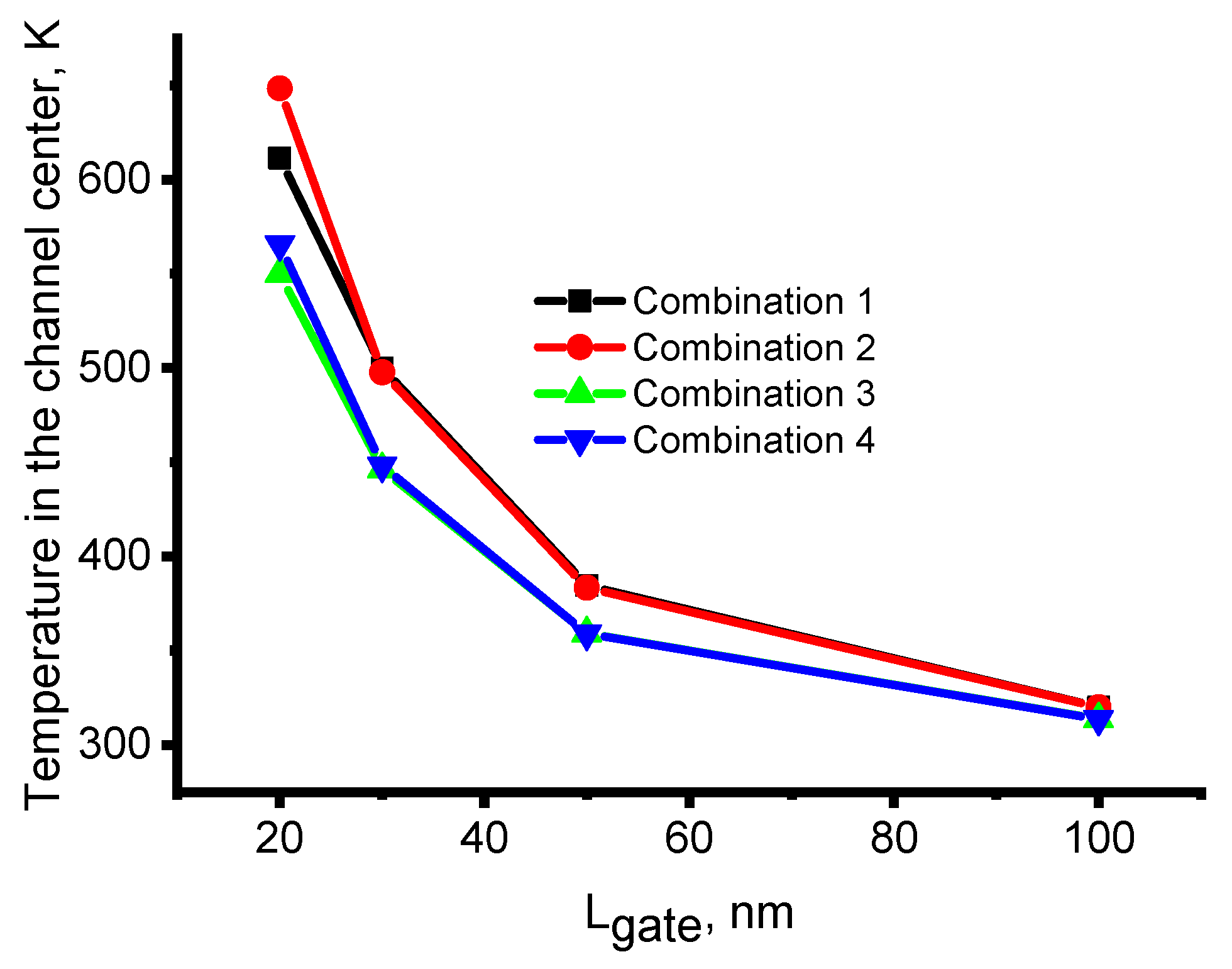

The results of simulating for more range of oxide materials combinations show that SHE is sensitive to gate length for all combinations of the gate and back oxide materials in the transistor

(

Figure 6). SHE dependence on the gate length was shown only for transistors for the first case because, for transistors for the second case, this dependence is the same. The sensitivity of SHE to the gate length can be explained by the dependence of the drain current on the channel length, which in our analysis is based on the gate length. As the drain current defines the heat generation rate, therefore at a long channel (small drain current) heat generation rate is decreased. Decreasing the temperature at long channel transistors and their tendency to the equal value for all four oxide materials combinations prove our assumption that at long channel main mechanism responsible for establishing the resulting temperature is the heat generation rate.

The temperature behavior shown in

Figure 6 can be explained by heat dissipation through the gate oxide and BOX. It is known that low thermal conductivity of oxide materials results in slow heat dissipation from the material and the formation of a higher equilibrium temperature in the channel than materials with higher thermal conductivity. Therefore, the thermal conductivity of the gate oxide and BOX materials is a very important parameter in SHE. Depending on the thickness, the thermal conductivity of HfO

2 films has values in the range of 0.27–4.3 W/(m∙K) at temperatures between 300 and 500 °C [

13,

14]. The values of the thermal conductivity of SiO

2 are in the range between 0.5 and 2.5 W/(m∙K) [

15,

16]. In our simulation, we used thermal conductivity values presented in

Table 2.

For gate lengths up to 100 nm, the mid-channel temperature for transistors with combinations 1 and 2 is higher than for combinations 3 and 4. Apparently, it is mainly related to a lower thermal conductivity of BOX material in combinations 1 and 2 (which is SiO2 ) than the thermal conductivity of BOX material in combinations 3 and 4 (which is HfO2). With the smallest gate length, lower than 30 nm, for combinations with the same BOX material, the temperature is higher for combinations with HfO2 as gate oxide material. At gate lengths between 30 and 100 nm the temperature for combinations with the same BOX material approximately is the same and practically is not dependent on the gate oxide material. At gate length 100 nm the temperature practically is the same for all four combinations, which means that at high gate lengths, the resulting mid-channel temperature is not dependent on gate oxide as well as BOX materials.

3.2. DIBL effect for different combinations of the gate oxide and back oxide materials

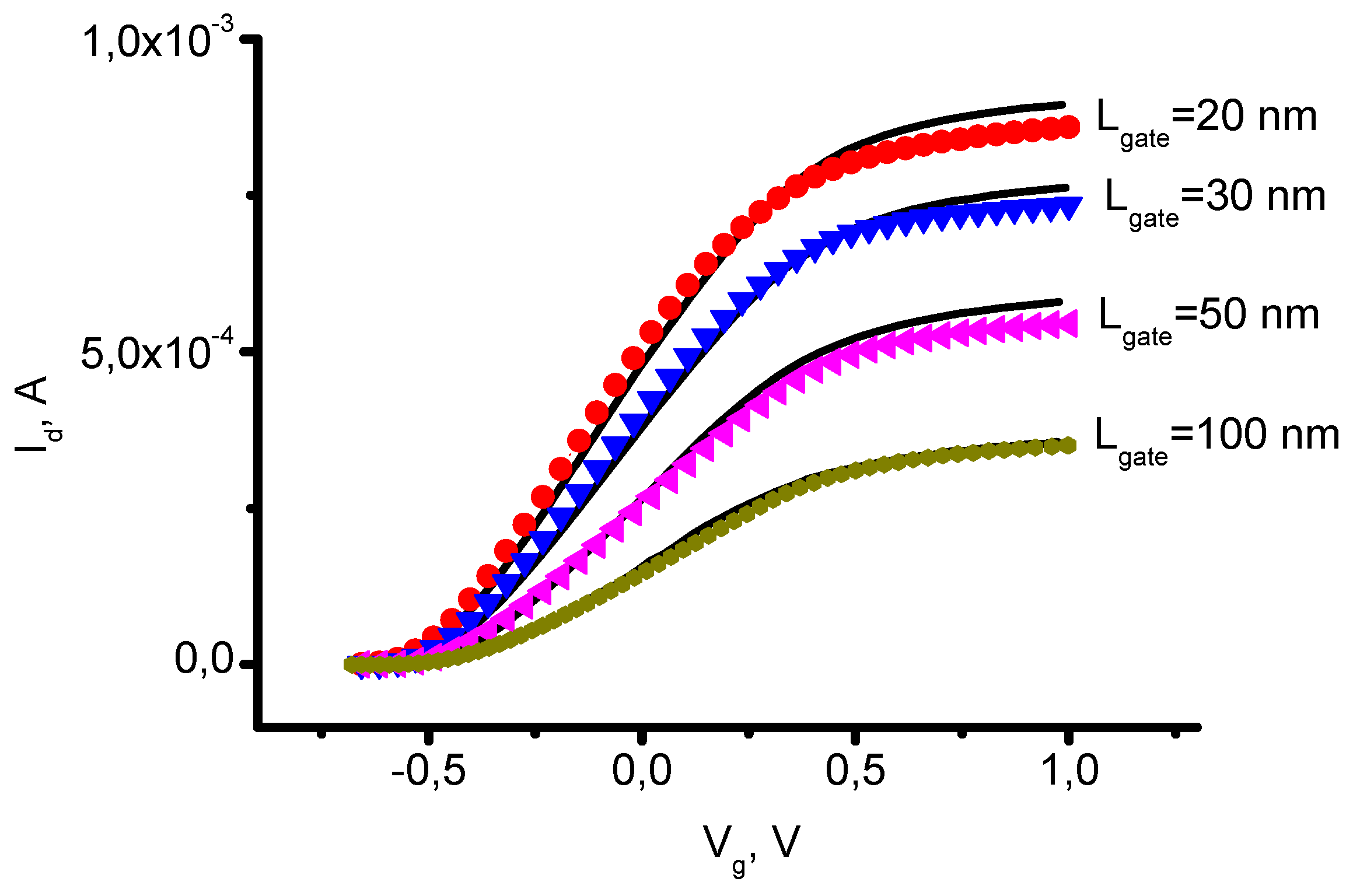

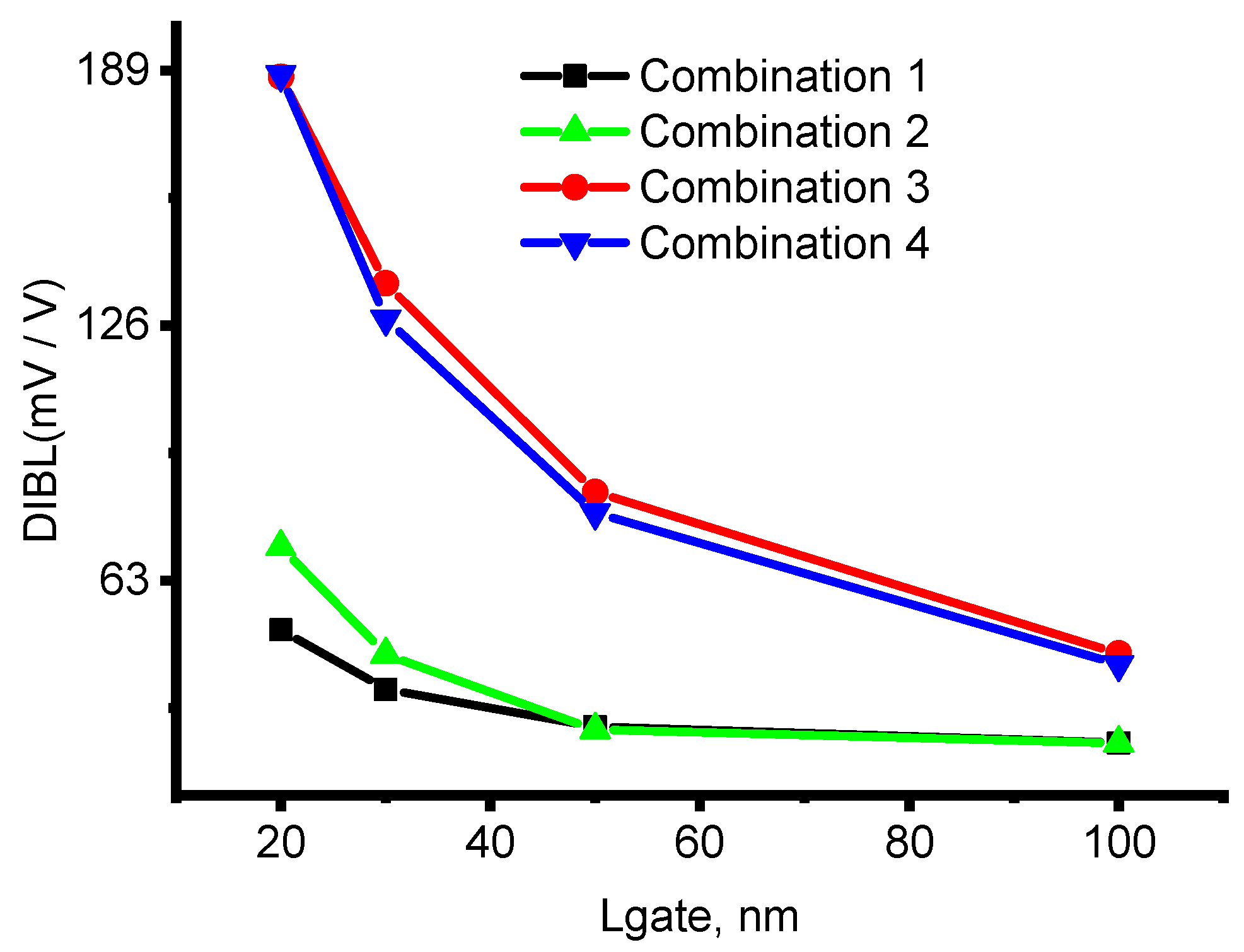

DIBL effect is one of the degradation effects similar to SHE, and also depends on the properties of the gate oxide and BOX materials. For comparison with the SHE effect, it was simulated the DIBL effect in a MOSFET with 2D-MoS2 as a transistor channel, with mentioned above four combinations of the gate oxide and BOX materials.

The results of the simulating show that the DIBL effect is more sensitive to the gate length for transistors with combinations number 3 and 4 (

Figure 7). In all ranges of transistor length, the DIBL effect for transistors with combination numbers 3 and 4 is higher than for transistors with combination numbers 1 and 2. It can be understood in the framework of a simple model describing the capacitive coupling between the channel and the device electrodes, proposed in [

11]. Within this model, the modified expression for DIBL given by [

11] is expressed as follows:

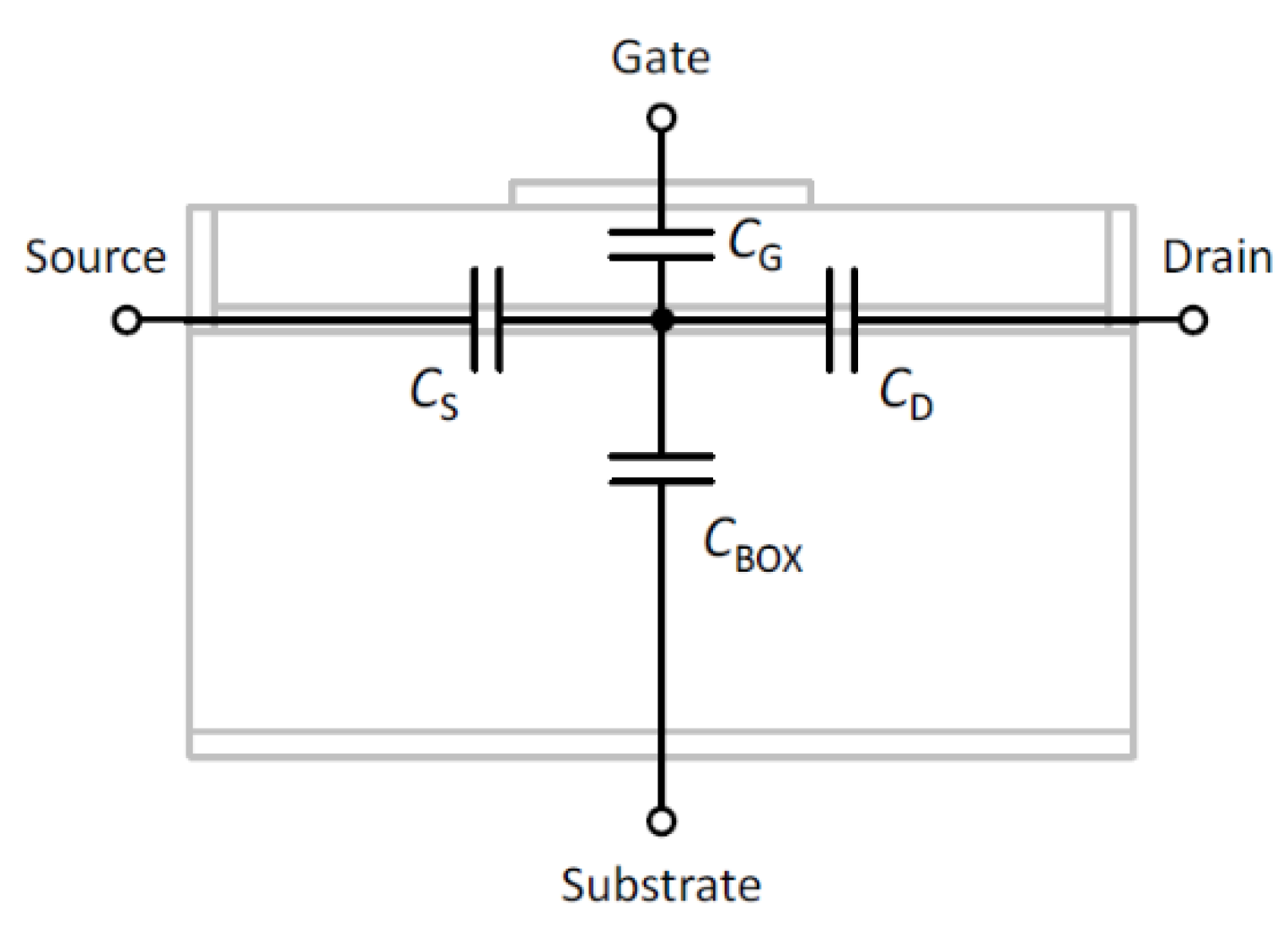

where

CD and C

G are drain-channel and gate-channel capacitances, respectively (

Figure 8). Three components contribute to the drain-channel capacitance (

CD): the capacitive coupling through the channel layer (

CD.ch), the coupling through the BOX (

CDbox), and the coupling through the gate oxide (

CD.ox). Therefore the drain-channel capacitance (

CD) is expressed as follows:

The capacitance components C

G , C

D.ch , C

D.ox depend on the dielectric constant of the channel 𝜀

MoS2 , while C

D.box is unaffected by 𝜀

MoS2 and depends on the dielectric constant of the BOX material. In our case

,

and

and

. Therefore, because the dielectric constant of the channel

is smaller, the gate capacitance C

G and the components C

D.ch and C

D.ox are reduced, and the DIBL effect is mainly will defined by C

D.box. Thus, for the transistors considered, the DIBL effect is defined by the dielectric constant of the BOX. In the range of combinations, the BOXs with the highest dielectric constant are in combinations number 3 and 4, where oxide materials are HfO

2 with

, so these combinations should have the highest DIBL effects. Therefore, while for transistors with combinations 1 and 2, the BOX material is SiO

2 with a lower dielectric constant (

); the DIBL effect for these transistors should have a lower DIBL effect. These proposals are in perfect agreement with

Figure 7. It is also seen in

Figure 7, that the gate oxide material does have not a considerable impact on the DIBL effect in the considered range of gate length.

3.3. Optimization of the combination of gate oxide and back oxide materials

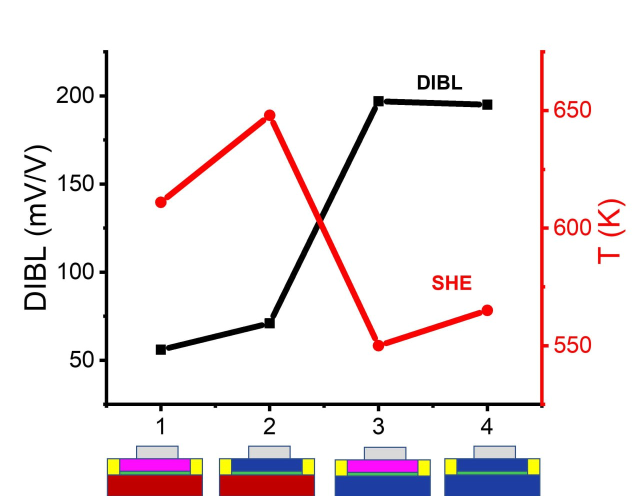

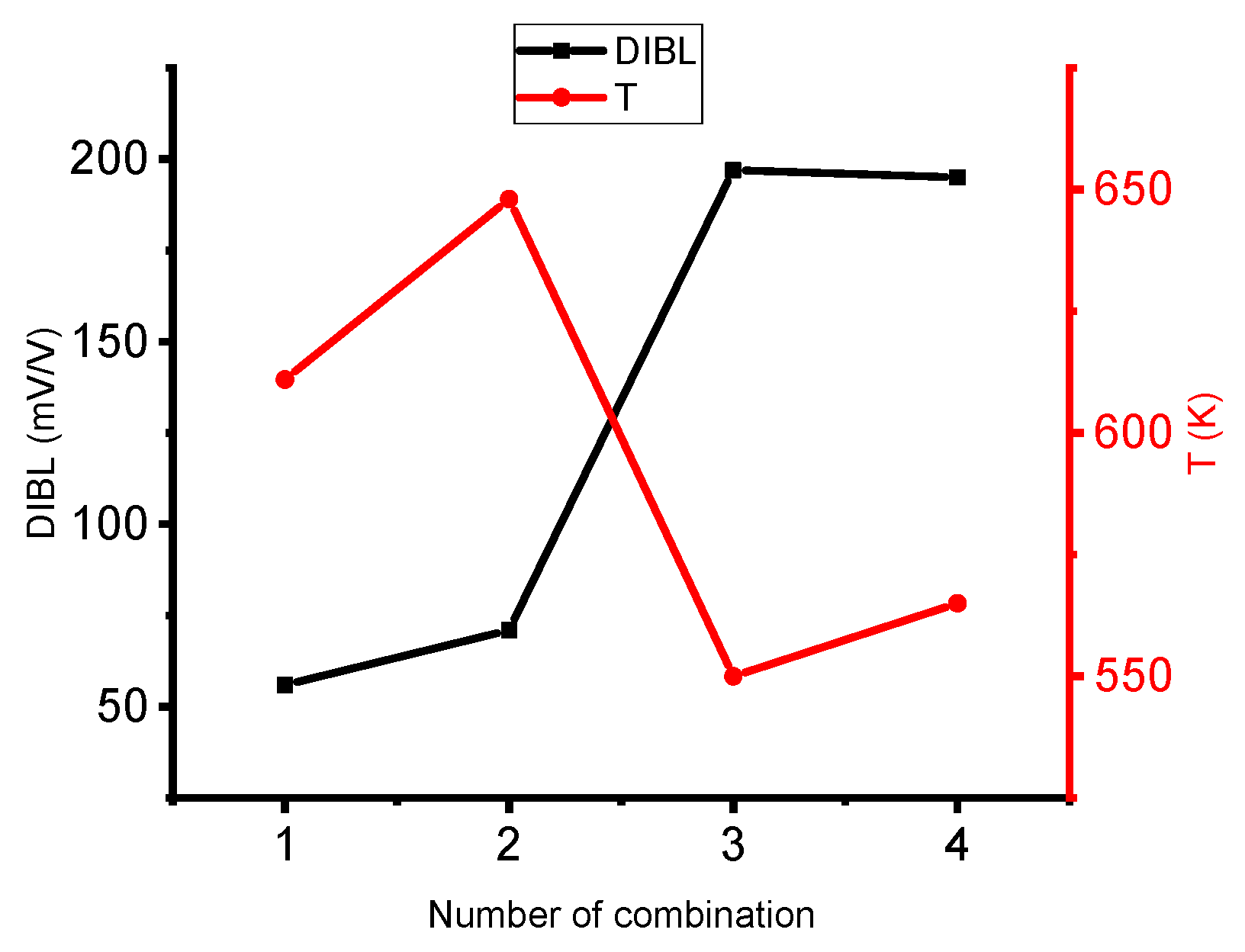

The dependence of the lattice temperature and DIBL on the combination number carried out from

Figure 6 and

Figure 7 for a gate length of 20 nm is shown in Fig 9. From the figure it can be seen that the SHE and the DIBL effect compete for the combination of the oxide materials. As we discussed above, the electrical and thermal properties of the back oxide material, namely the dielectric constant and the thermal conductivity, are mainly responsible for the SHE and DIBL effect in considered 2D-MoS

2 MOSFETs.

Figure 9.

DIBL effect and SHE dependence of combinations of gate oxide and back oxide materials in MOSFET.

Figure 9.

DIBL effect and SHE dependence of combinations of gate oxide and back oxide materials in MOSFET.

Achieving the small DIBL effect requires a low dielectric constant back oxide material, while reducing the lattice temperature in the transistor channel requires a high thermal conductivity back oxide material. We have considered two popular, conventional used, back oxide materials: SiO2 and HfO2. When the back oxide material is SiO2, it has a small dielectric constant, which leads to a reduction in DIBL; at the same time, it also has a small thermal conductivity, which leads to a high lattice temperature in the transistor channel. Conversely, in the case of using HfO2 material as the back oxide material, it has a high dielectric constant, leading to a high DIBL effect, while it also has a relatively high thermal conductivity, leading to a reduction in the lattice temperature in the transistor channel.

From our results, it is possible to define the range of electrical and thermal parameters of oxide materials that allow reaching optimal immunity against SHE as well as the DIBL effect. From

Figure 7, it can be concluded that using the BOX material with a relative dielectric constant in the range between 3.9 and 25, and with thermal conductivity between 1.4 and 2.3 W/Km is the choice for reaching optimal immunity. to degradation effects such as SHE and DIBL effects in 2D-MoS2-based MOSFET. Gate oxide material practically does not considerably impact to SHE as well as to DIBL effect.