1. Introduction

Although amplifiers are useful on their own, the design of an amplifier allows for the evaluation of various circuit design and analysis methods. When designing an amplifier, circuit design and PCB architecture should always consider amplifier stability. However, there are times when an amplifier is pushed to its absolute limit and fails to perform as expected, resulting in output signal distortion. Several publications in specialized journals investigate amplifier stability [

1,

2,

3].

A variety of criteria, including Bode, are used to assess amplifier stability [

1,

4].

Because amplifier stability is a complex problem, many mathematical modelling methods have been developed to investigate it [

2]. A computer tool that enables a mathematical examination of the physical stability of the bipolar transistor in the design of amplifiers is described in [

2]. Users can set values for voltage gain, output impedance, input impedance, transistor current gain, and power supply current gain, and the software will return resistance values as a result. The study concluded that the power wasted in a bipolar transistor amplifier is inversely related to the magnitude of the input signal and directly proportional to the distance of the half of the input signal from the operating point. It has been determined that the operation point should be located higher than 0.05 and lower than 0.95, with 90% of the load line used for amplification.

In our study we used LabVIEW software to simulate various amplifier types. This program is useful and appropriate for simulating analogue electronic circuits [

5].

Other software programs for modelling electronic circuits are described in specialized literature. Multisim simulation software is one example [

6]. Multisim was used to study an amplifier used as a second order filter in the paper [

6]. Multisim software can be used to create a circuit with inputs and outputs. Multisim was used in [

6] to simulate a Bode plotter component and generate a frequency signal graph. Bode plotter simplifies the examination of circuits, signal magnitude, and phase shape, and it can compare variations between circuits.

In [

7], amplifiers were analysed using another software package, this time one written in Java. The software presented in [

7] is a learning tool that enhances understanding of multi-stage amplifiers. This makes it possible for it to serve as a virtual guide with a user-friendly graphical interface that facilitates learning.

Several publications have proposed the common emitter (CE) amplifier design as a method for obtaining suitable amplifier performance parameters. The authors of [

3] presented an amplifier that would perform well for devices that operate at low frequencies. The PSPICE program was used to research the proposed amplifier in [

3,

8]. For the investigation of amplifiers, the PSPICE program is useful. This bipolar junction transistor SPICE model from [

8] was created to help students better understand amplifier design and analysis methods.

Because there is a need in technology to amplify electrical signals, i.e. to obtain on a load circuit higher power signals but identical in form of time variation with those of low power available, amplifiers are used [

9,

10,

11,

12,

13,

14]. Electronic amplifiers are constructed using bipolar or field effect transistors, either as discrete circuits or as integrated circuits.

In practice, there is a wide range of amplifiers. Their classification can be done using a variety of criteria, [

15].

According to the frequency range of the amplified signals, there are direct current amplifiers, where the lower limit of the frequency of the amplified signal is 0 Hz, low frequency amplifiers, where the frequency band is in the range n x 10 Hz ÷ n x 10 kHz, broadband amplifiers, where the frequency band can be in the range 0 Hz ÷ n x 10 MHz, and narrowband amplifiers, in which the ratio between the maximum and minimum frequency of the signal to be processed is of the order units.

According to the amplitude of the signal applied to the input, there are small signal amplifiers, where the amplitude of the input signal is small enough for the static operating point of the transistor to remain in a linear region of the dynamic or transfer characteristic, and large signal amplifiers, where the amplitude of the input signal is large enough for the static operating point of the transistor to remain in a linear region of the dynamic or transfer characteristic at which the amplitude of the input signal exits the linear region of the dynamic or transfer characteristic.

In dynamic mode, there are three types of connections made by the terminal of the bipolar transistor that is common at the input and output: common emitter connection, common collector connection, and common base connection.

According to the operating regime of the transistor, materialized by the conduction duration during a period of the signal, the amplifiers can operate in class A, where there is collector current throughout the period of the input signal, class B, where the current collector exists only on one half-period of the input signal, class C, where the transistor conducts less than one half-period of the input signal, and class AB, which represents an intermediate category between classes A and B.

According to the type of coupling between stages, there are amplifiers with direct coupling, capacitive coupling, transformer coupling, optical coupling, and so on, depending on the type of coupling between stages.

The following main characteristics are used to evaluate and compare amplifier quality, [

15,

16]: amplification, linear distortions such as frequency distortions, phase distortions, and transient distortions, nonlinear distortions, and noises.

The main characteristics of an amplification stage can be determined using the transistor’s quadrupole parameters: current amplification, voltage amplification, input impedance or resistance, and output impedance or resistance. In this regard, the quadrupole parameters selected based on the frequency of the input signal can be used. For low frequencies, the parameters ”h”, considered in this paper to have real values, the parameters ”π” or the parameters ”r” are particularly useful. For high frequencies, the parameters ”y” or the natural equivalent circuit parameters, ”g”, are used [

15,

16,

17,

18].

Because the functioning of amplification stages with bipolar transistors at low and medium frequencies was studied in this paper, the quadrupole ”h” parameters, which are valid for any type of transistor connection, were taken into account.

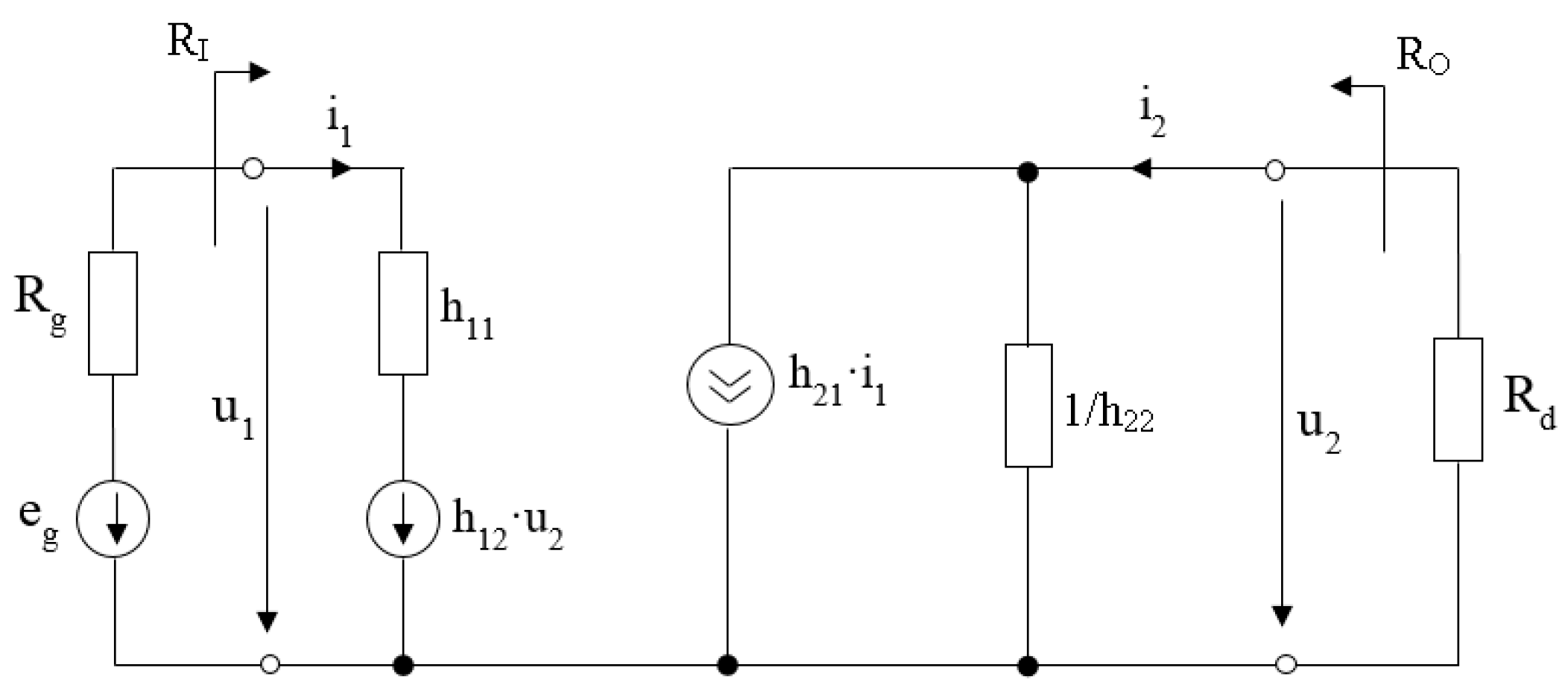

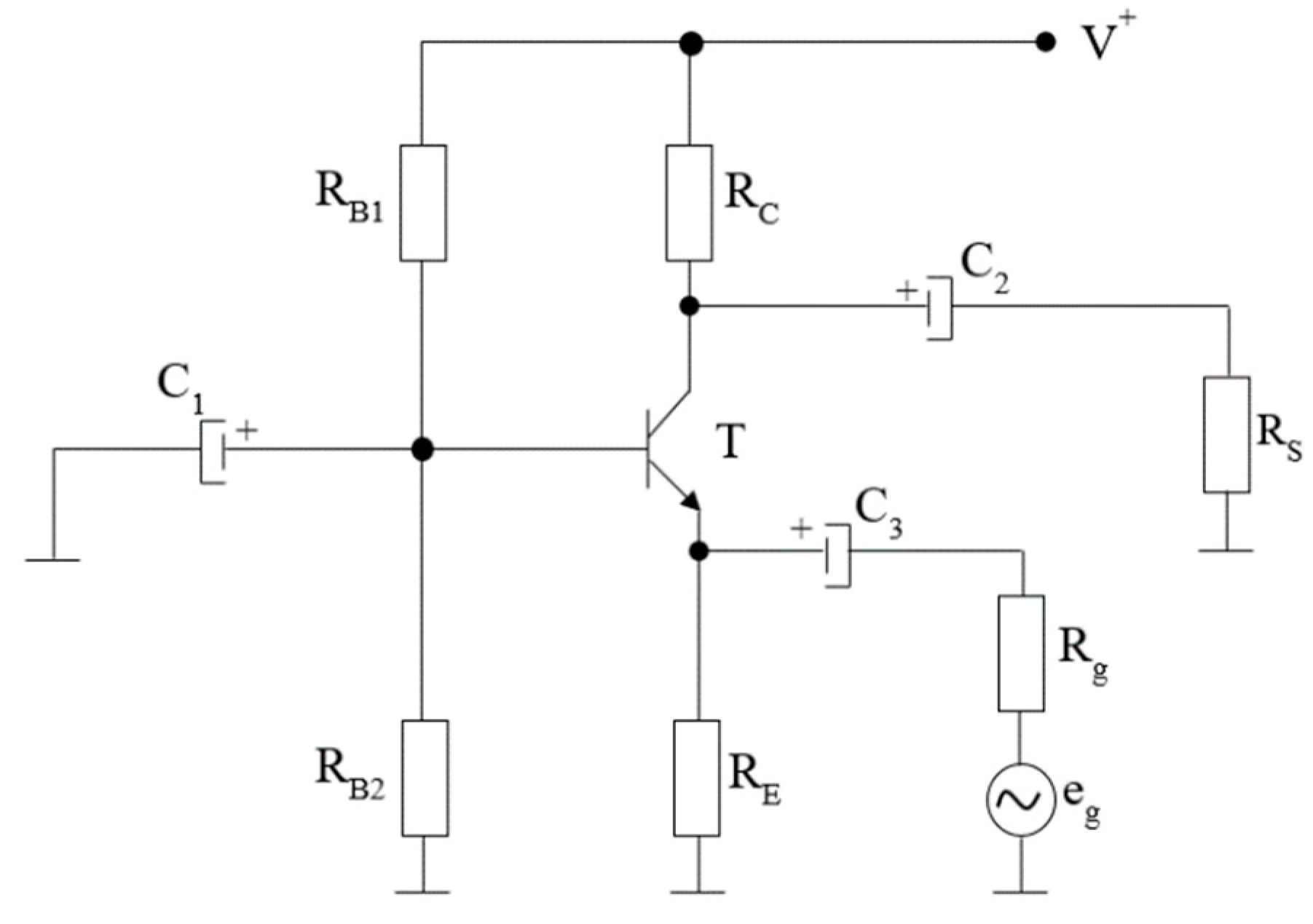

Figure 1 depicts the equivalent circuit of the amplifier stage with bipolar transistor using the quadrupole parameters ”h”, [

15].

The transistor’s quadrupole equations are given by relation (1).

Because the usual values of the quadrupole parameters h12 and h22 have no significant influence on the values of an amplifier’s main characteristics, these parameters were ignored in the application.

The effects of capacitors coupling between the signal generator and the amplifier, as well as between the amplifier and the load circuit, are independent and are included in the amplification expression in conventional amplification schemes. These effects consist of each capacitor introducing a low cut pulsation into the Bode diagram. The use of a bipolar transistor in the scheme of an amplification stage, on the other hand, generates a high cut pulsation due to the transistor’s parasitic capacitances [

15].

The Bode diagrams gain-pulsation and phase-pulsation can be used to study the behaviour of an amplifier while accounting for these pulsations. The use of these diagrams also provides the benefit of determining the amplifier’s stability area, [

15,

16].

The amplifier for that is represents the gain-pulsation and phase-pulsation characteristics has a single amplification stage. Common emitter, common collector, and common base connections were all considered. In the case of each connection, the values of the elements in the diagram can be selected and used to calculate the parameters of the amplification stages, [

14,

15,

16]. The values of the signal generator and load circuit elements, as well as the coupling elements, will be determined.

4. Results of simulation and experimentation

This section contains simulation and experimentation results for the amplifier operating in the connections presented in section 2: common emitter, common collector, and common base, [

31,

32,

33,

34,

35,

36,

37].

In order to validate the simulation results using the LabVIEW application, a specialized program Multisim was used, as well as experimental measurements using the Electronics Explorer Board. Bode characteristics can be determined using both Multisim and the Electronics Explorer Board. In both simulations and experimental amplifiers, the same transistor was used.

4.1. Simulation and experimentation results for common emitter connection

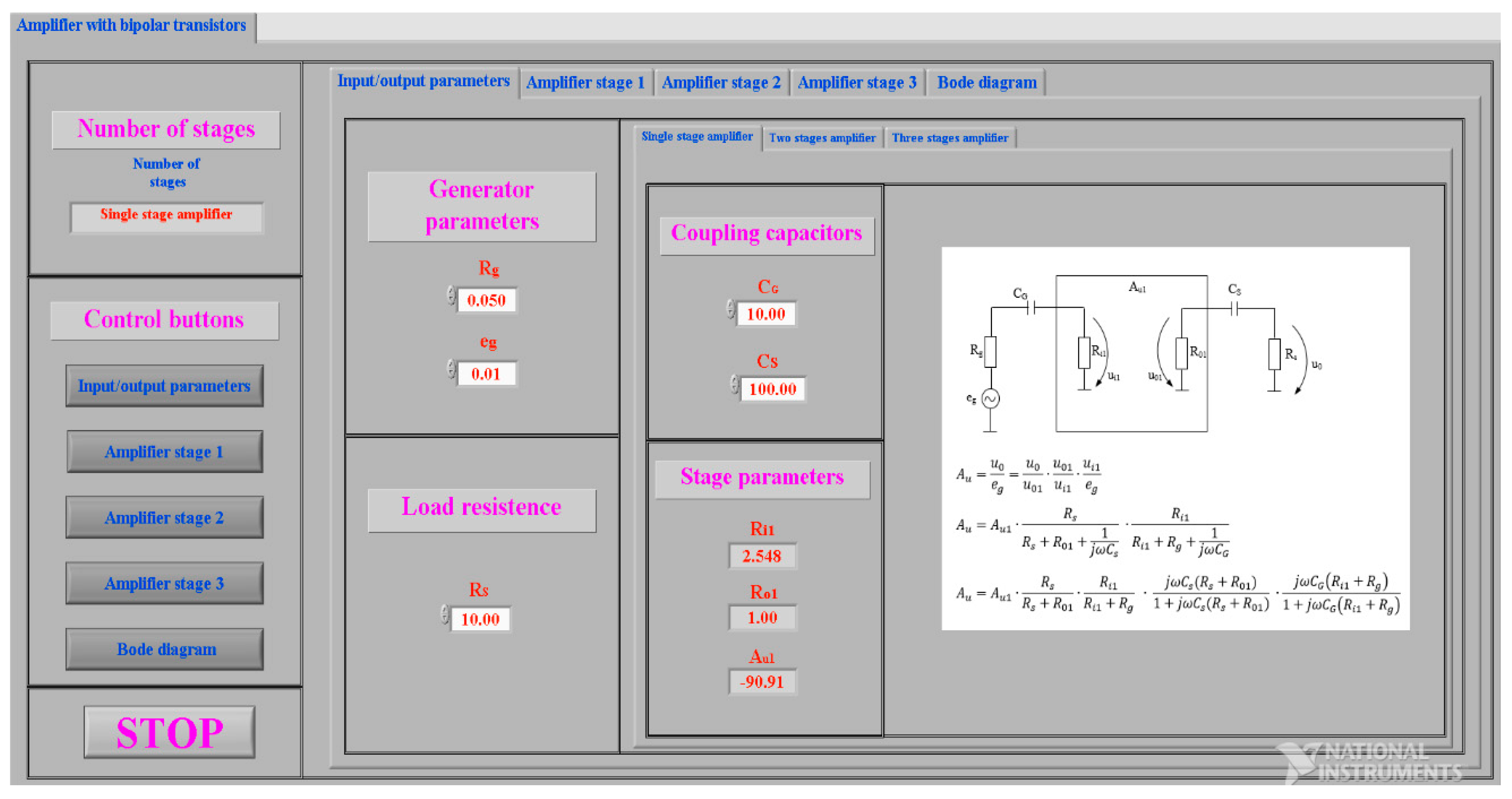

The input parameter values for this connection were chosen in such a way that the Bode diagram presented two different low pulsations, [

15,

16]. These values are: for generator parameters, R

g = 0.05 kΩ and e

g = 10 mV, for load resistance, Rs = 10 kΩ, for coupling capacitors between the generator and the amplifier stage, C

G = 10 µF and for coupling capacitors between amplifier stage and the load, Cs = 100 µF.

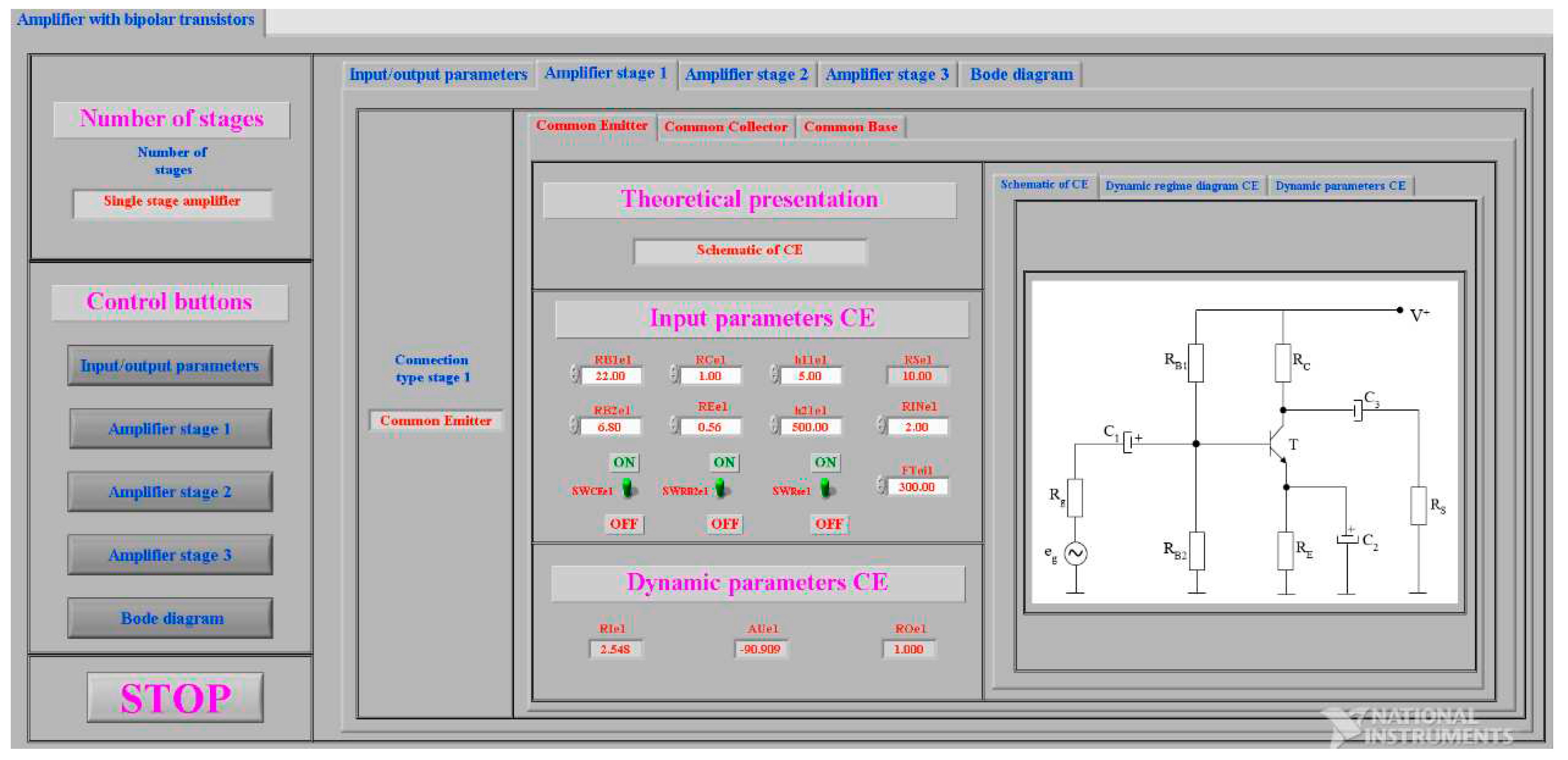

The parameters values for the common emitter connection are presented in

Figure 9.

As previously stated, the structure of the amplifier stage can be modified using the switches SW

CEe1, SW

RB2e1 and SW

RSe1.

Table 1 present the values of the output parameters, R

Ie1, A

Ue1 and R

Oe1 for all situations in which SW

CEe1, SW

RB2e1 and SW

RSe1 can be established.

Table 1 reveals some conclusions regarding the effect of the three switches on the values of the output parameters.

1. Connecting the capacitor C2 from figure 20 with the switch SWCEe1 in the ON state results in a significant increase of AUe1 and a decrease of RIe1.

2. Selecting the polarization mode of the transistor base with resistive divider by connecting the switch SWRB2e1 in ON state causes the input resistance RIe1 to decrease.

3. Switching SWRSe1 in ON state conduct to increasing of AUe1 with about 35%.

4. None of the three switches have any effect on the ROe1 value.

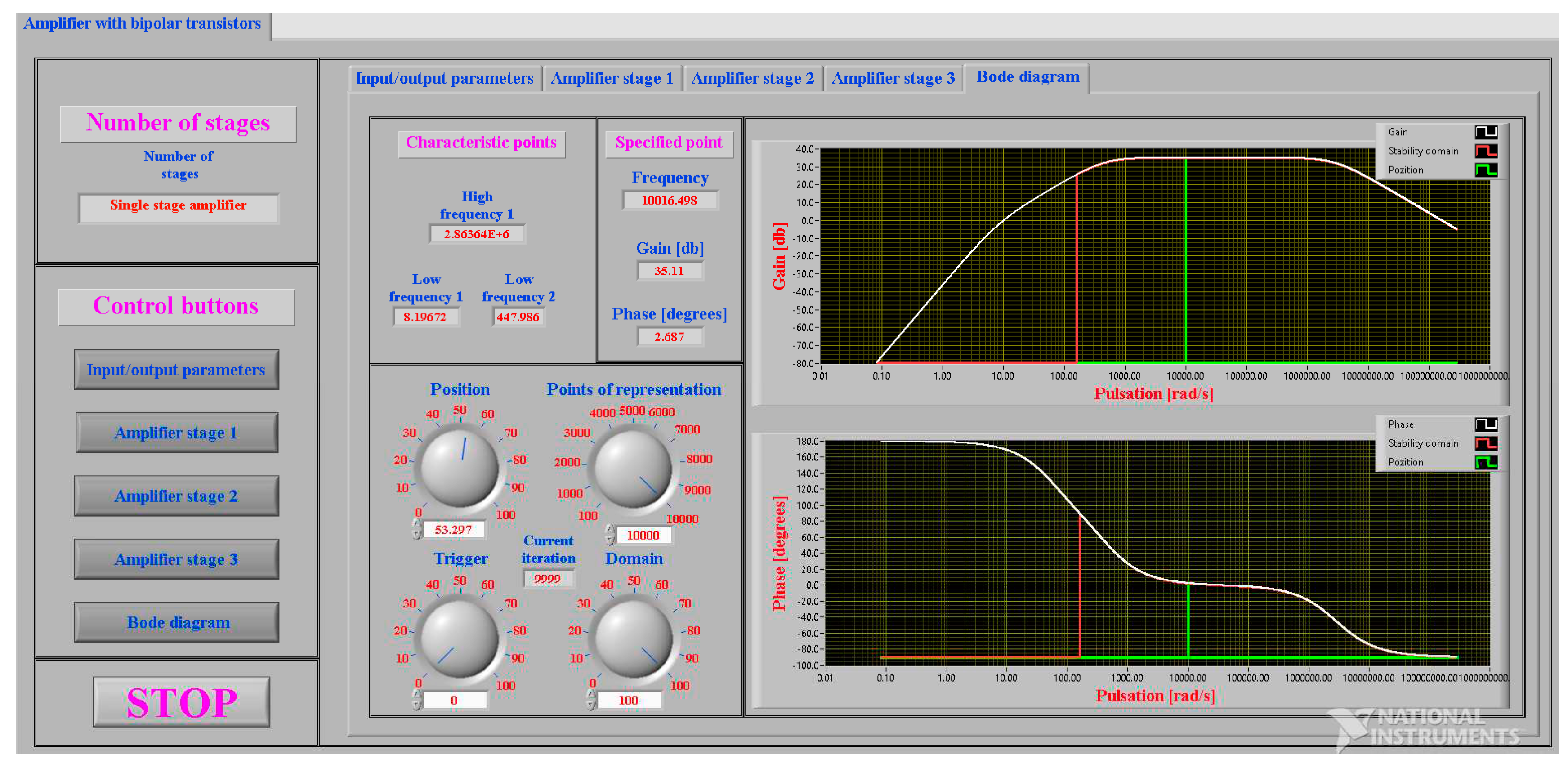

The effect of switch SW

CEe1 can be seen in the Bode diagrams in

Figure 20,

Figure 21 and

Figure 22 for SW

CEe1 to ON, line 8 from

Table 1, and in

Figure 26 for SW

CEe1 to OFF, line 4 from

Table 1. All of these figures were obtained through simulations with the presented application and allow for the low and high cut frequency to be determined. These frequencies were determined as the points where the gain was reduced by 3 decibels.

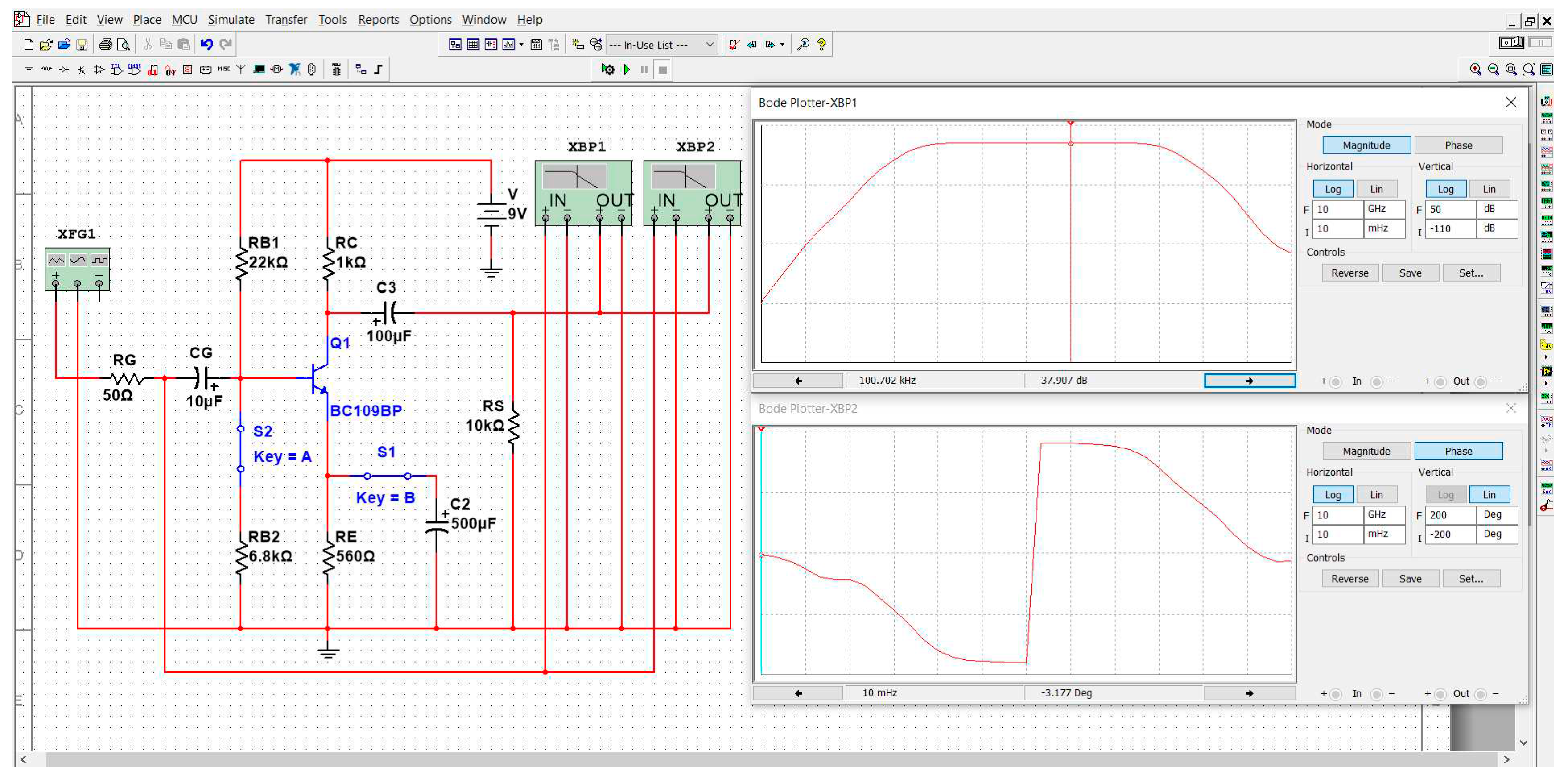

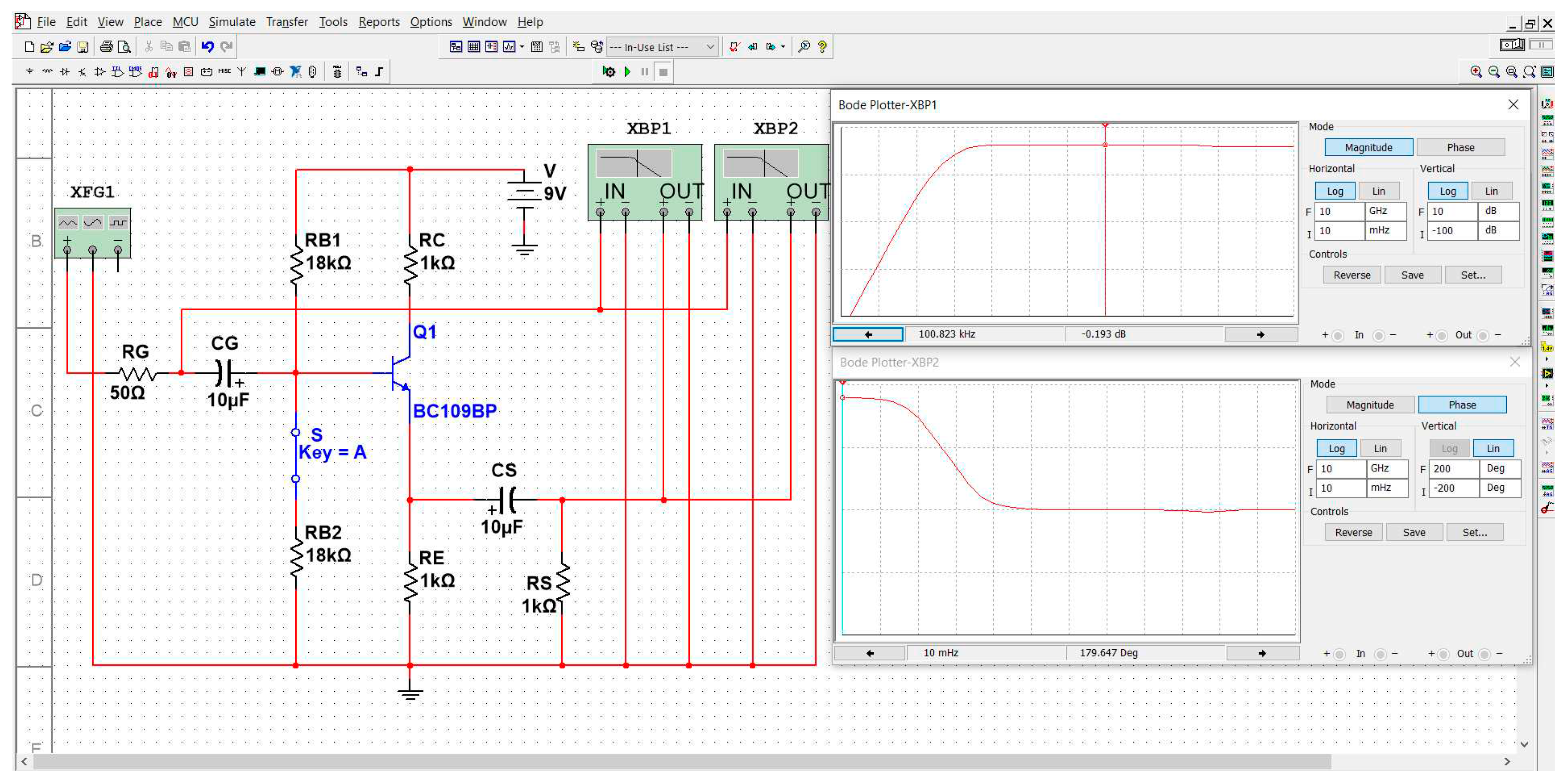

Multisim, a specialized simulation program, was used to verify the LabVIEW simulation results.

The simulation results obtained with Multisim are shown in

Figure 23.

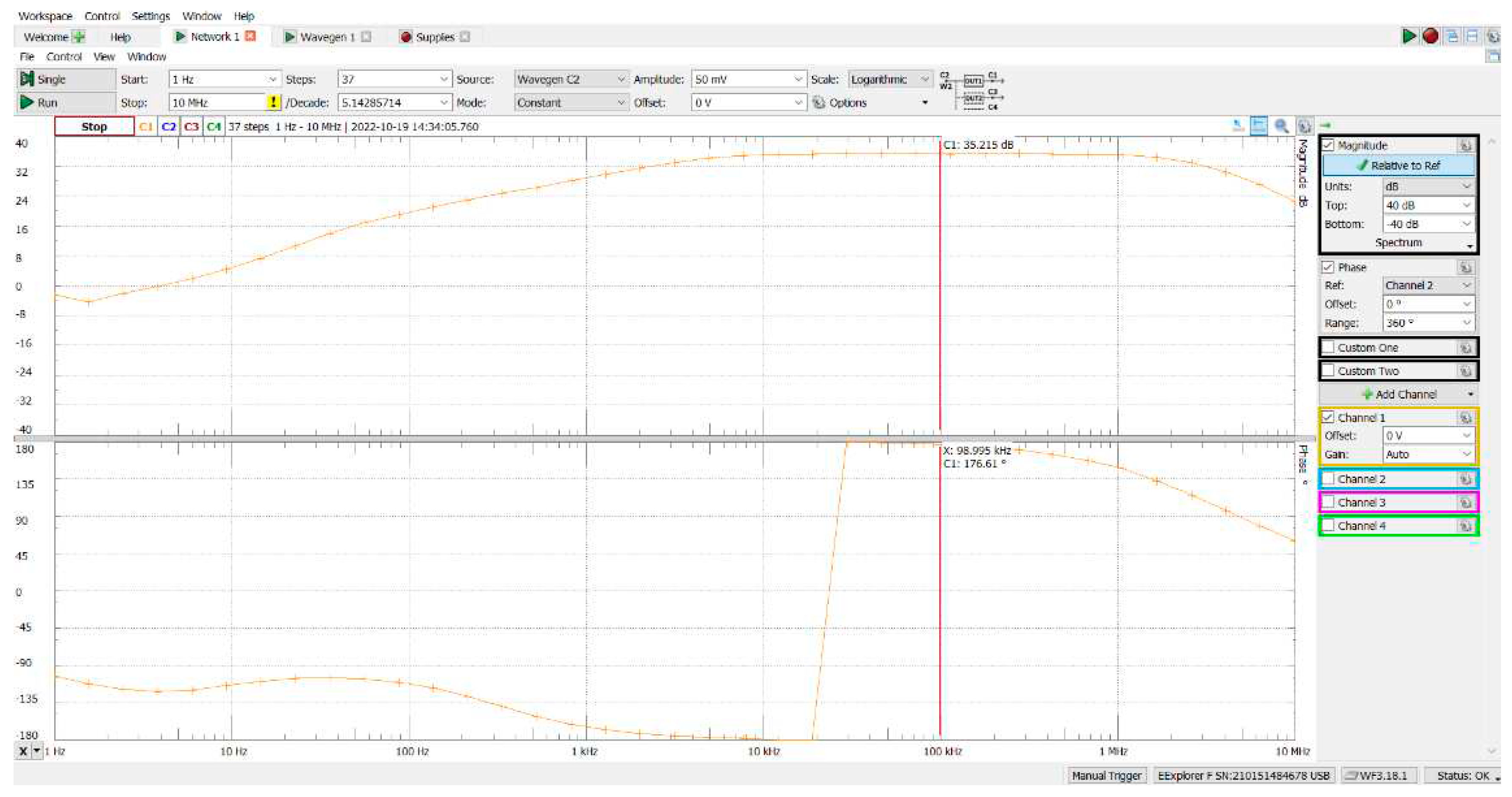

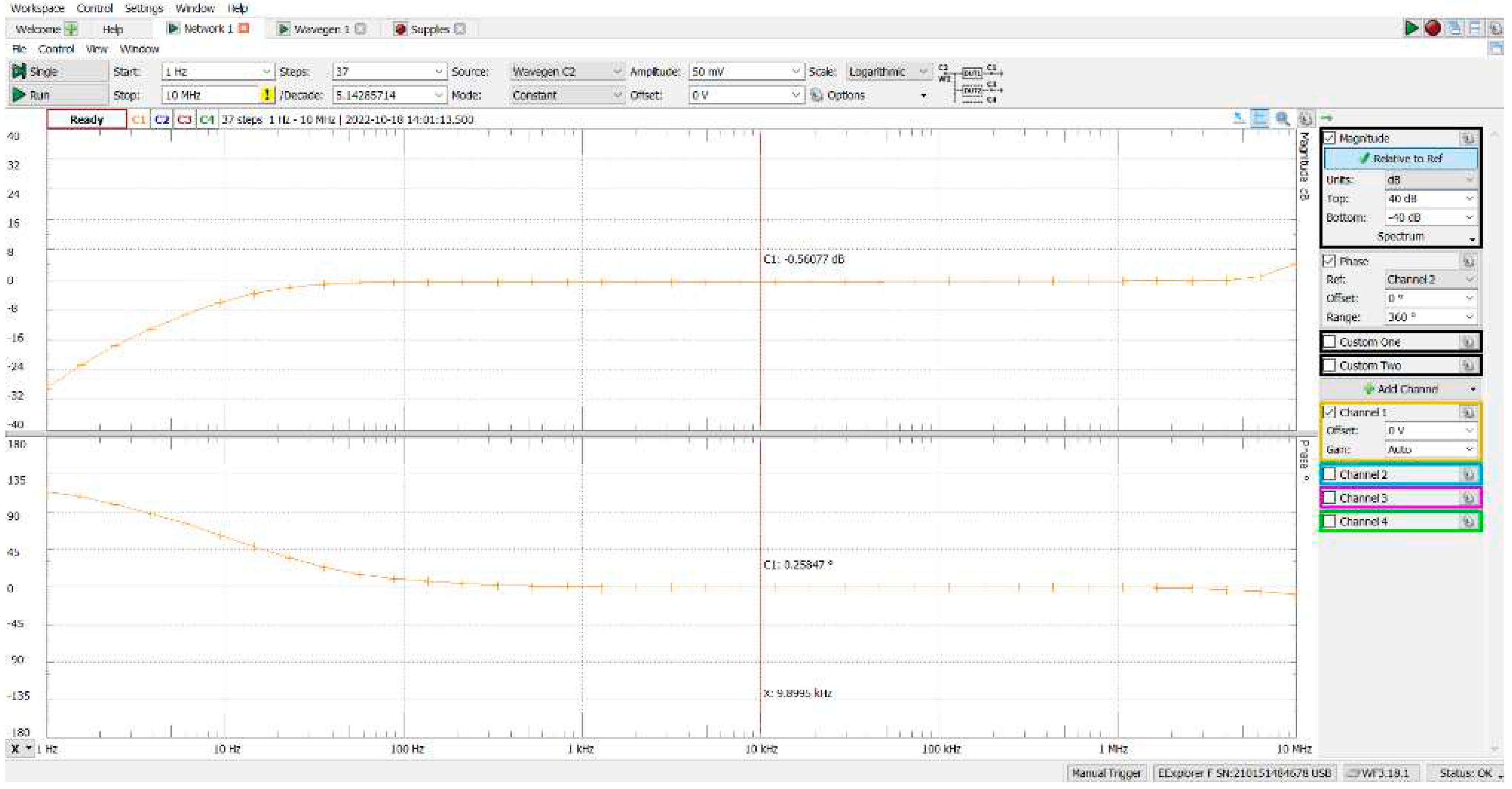

In order to validate the simulation results produced by LabVIEW and Multisim, experimental measurements were performed on a real circuit using an Electronic Explorer Board, which can also be used to determine the Bode characteristics. The Electronic Explorer Board has a frequency range of up to 10 MHz.

The measurement results obtained with Electronic Explorer Board are presented in

Figure 24.

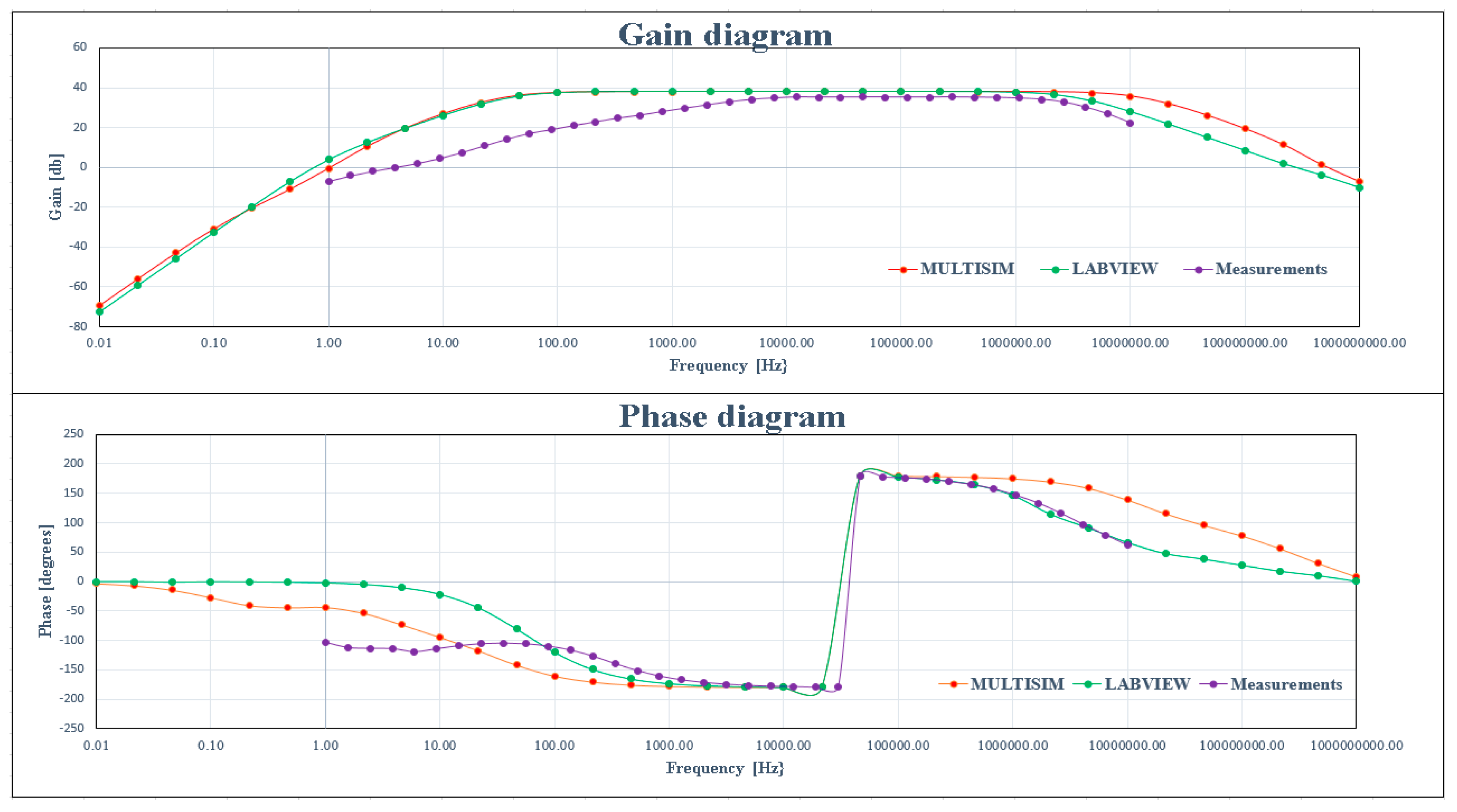

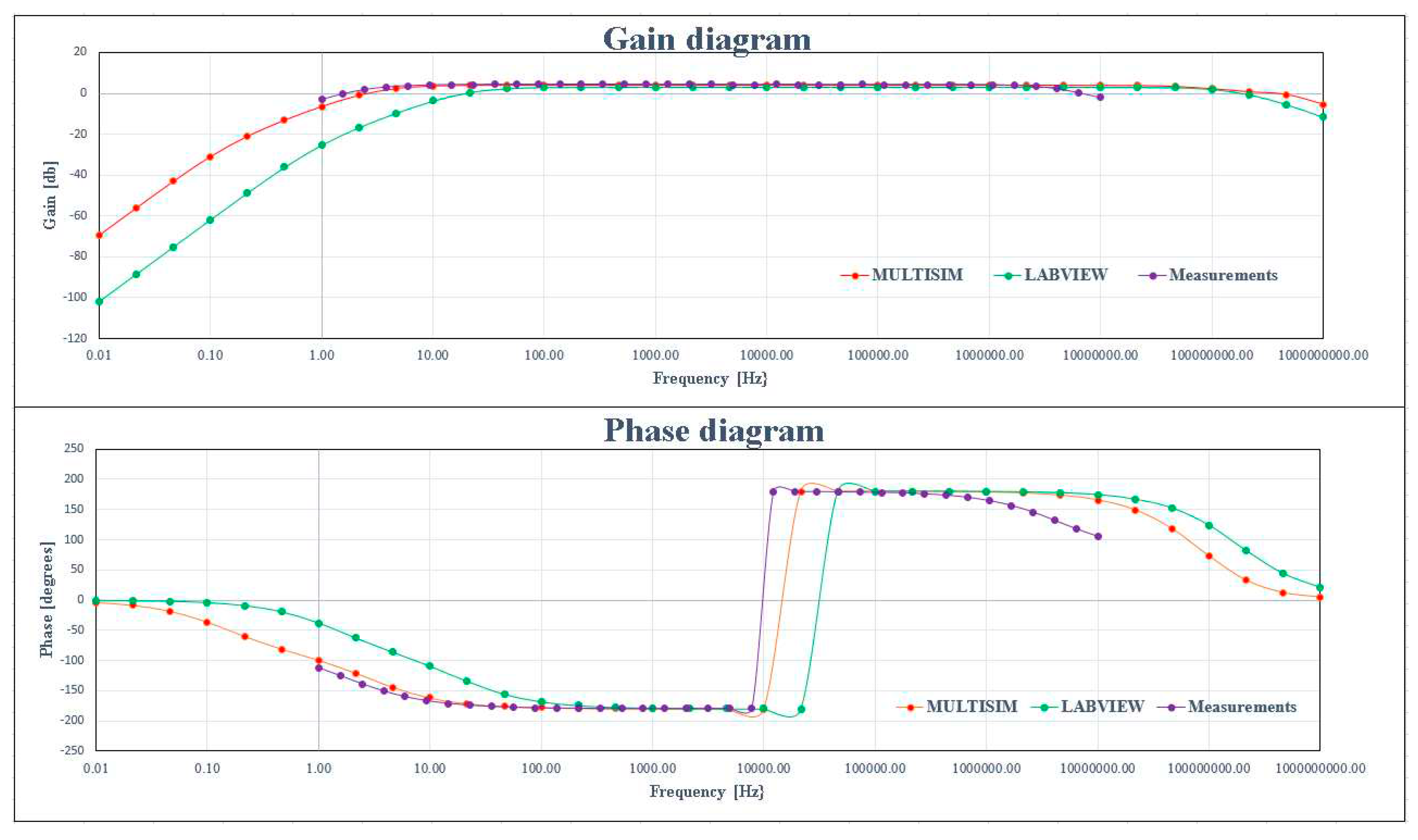

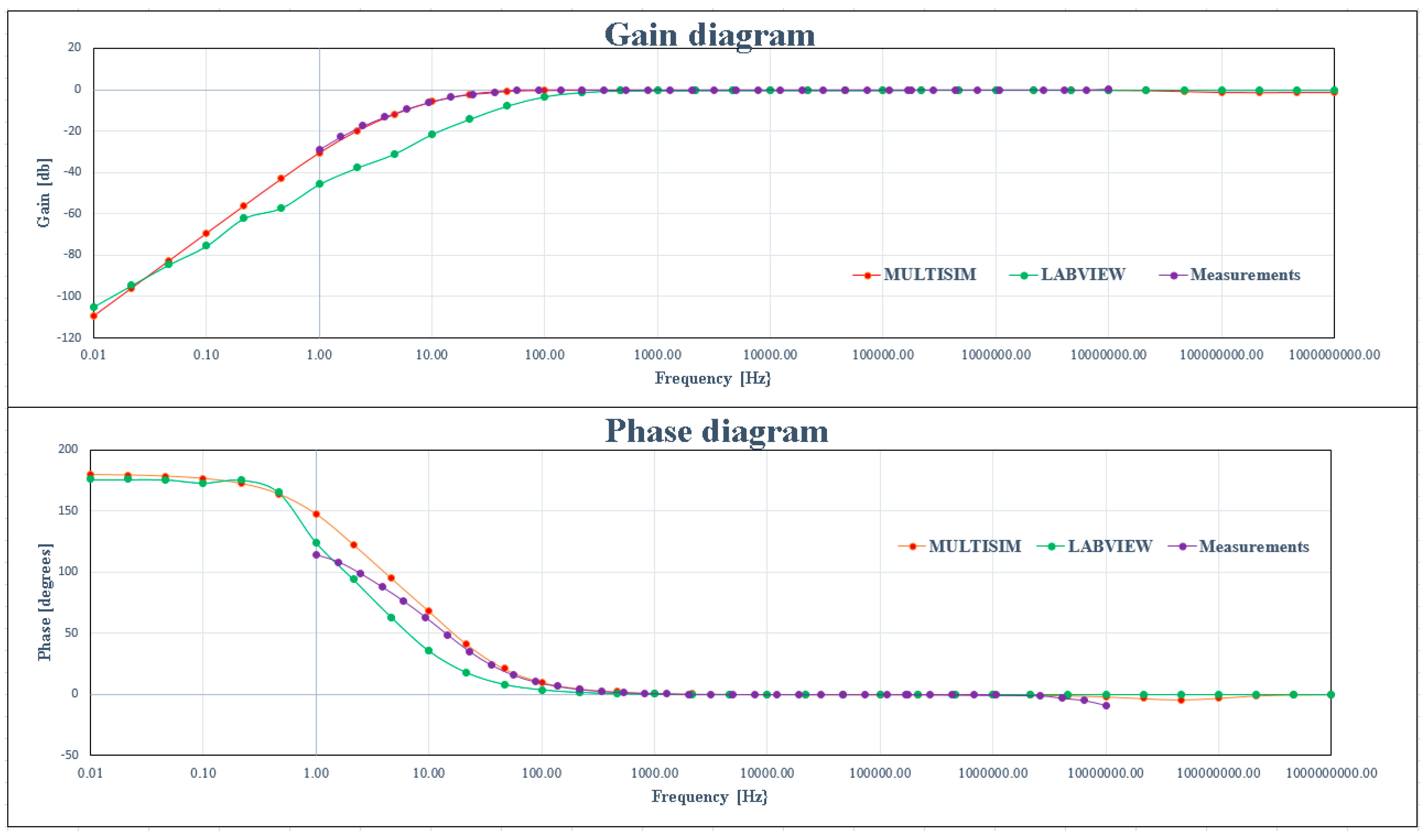

A comparison between the simulations and experimental results can be seen in

Figure 25.

Analyzing the gain diagram reveals that the simulation and experimental results are very similar at medium and high frequencies. In terms of the phase diagram, both simulations and measurements achieve the same crossing from -180 to 180 degrees, and the LabVIEW simulations and measurements are nearly identical at medium and high frequencies.

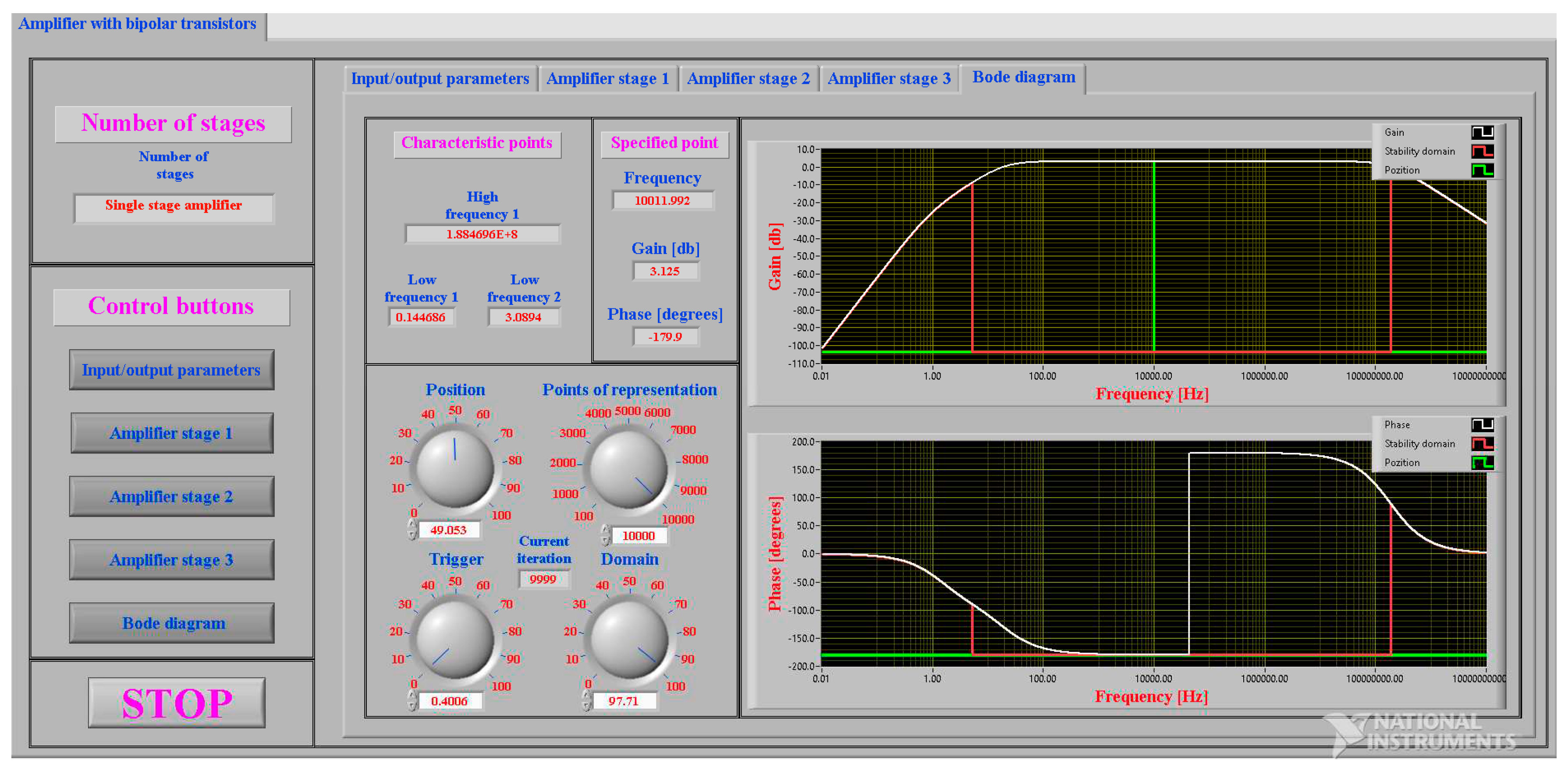

Figure 26.

Bode diagram for line 4 from

Table 1, for SW

CEe1 to OFF, for 10 kHz frequency.

Figure 26.

Bode diagram for line 4 from

Table 1, for SW

CEe1 to OFF, for 10 kHz frequency.

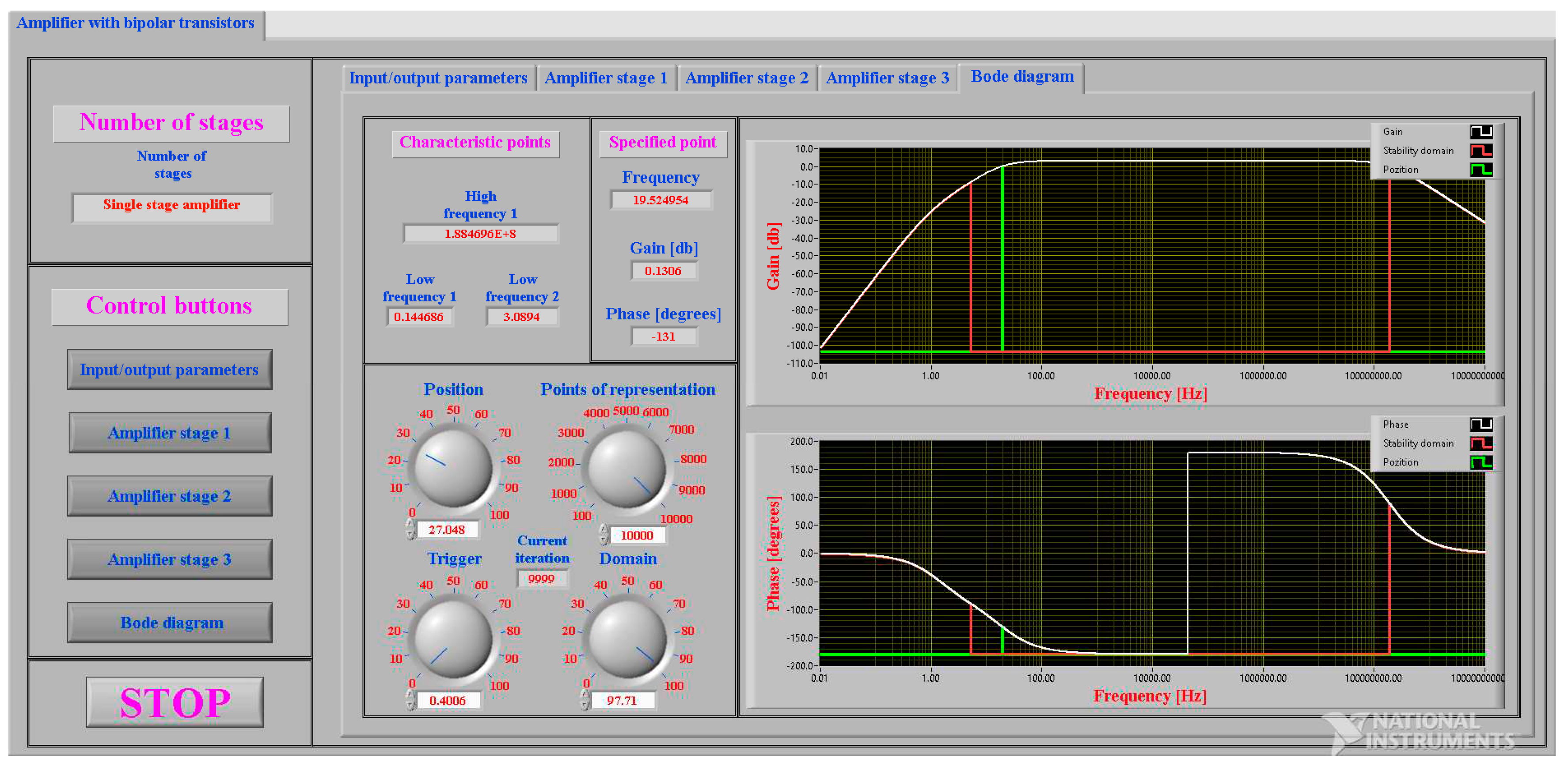

Figure 27.

Bode diagram for line 4 from

Table 1, for SW

CEe1 to OFF, for low cut frequency of 19.5 Hz.

Figure 27.

Bode diagram for line 4 from

Table 1, for SW

CEe1 to OFF, for low cut frequency of 19.5 Hz.

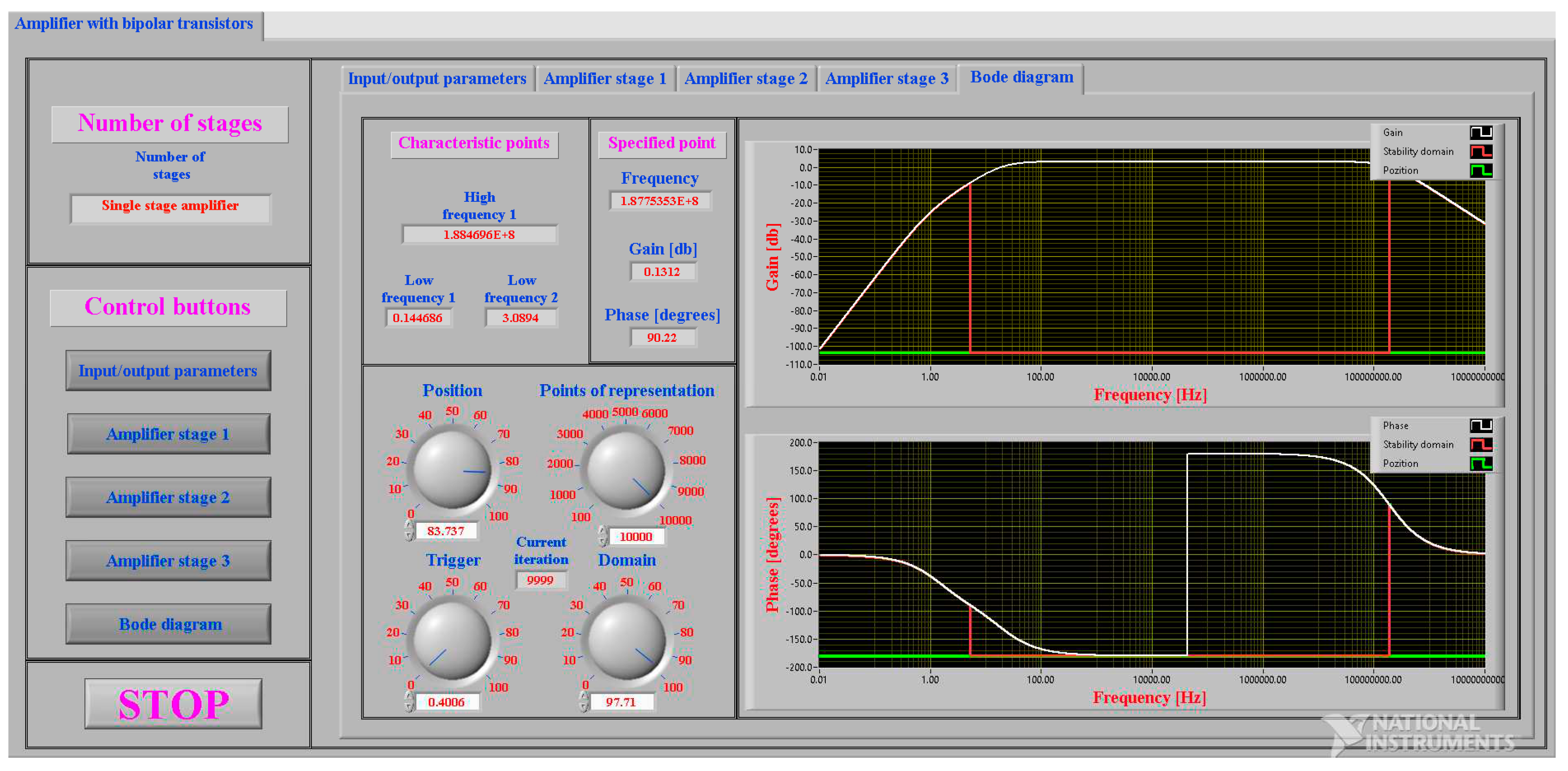

Figure 28.

Bode diagram for line 4 from

Table 1, for SW

CEe1 to OFF, for high cut frequency of 188.7 MHz.

Figure 28.

Bode diagram for line 4 from

Table 1, for SW

CEe1 to OFF, for high cut frequency of 188.7 MHz.

As in previous situation when SW

CEe1 was ON, a similar comparison between the simulations and experimental results can be made when SW

CEe1 was OFF. The comparison results can be seen in

Figure 29.

Analyzing the gain diagram reveals that the simulation results are very similar at medium and high frequencies. At medium frequencies both the simulations and measurements are very closed.

In terms of the phase diagram, both simulations and measurements achieve similar values to crossing from -180 to 180 degrees, and the LabVIEW simulations and measurements are nearly identical at medium frequencies.

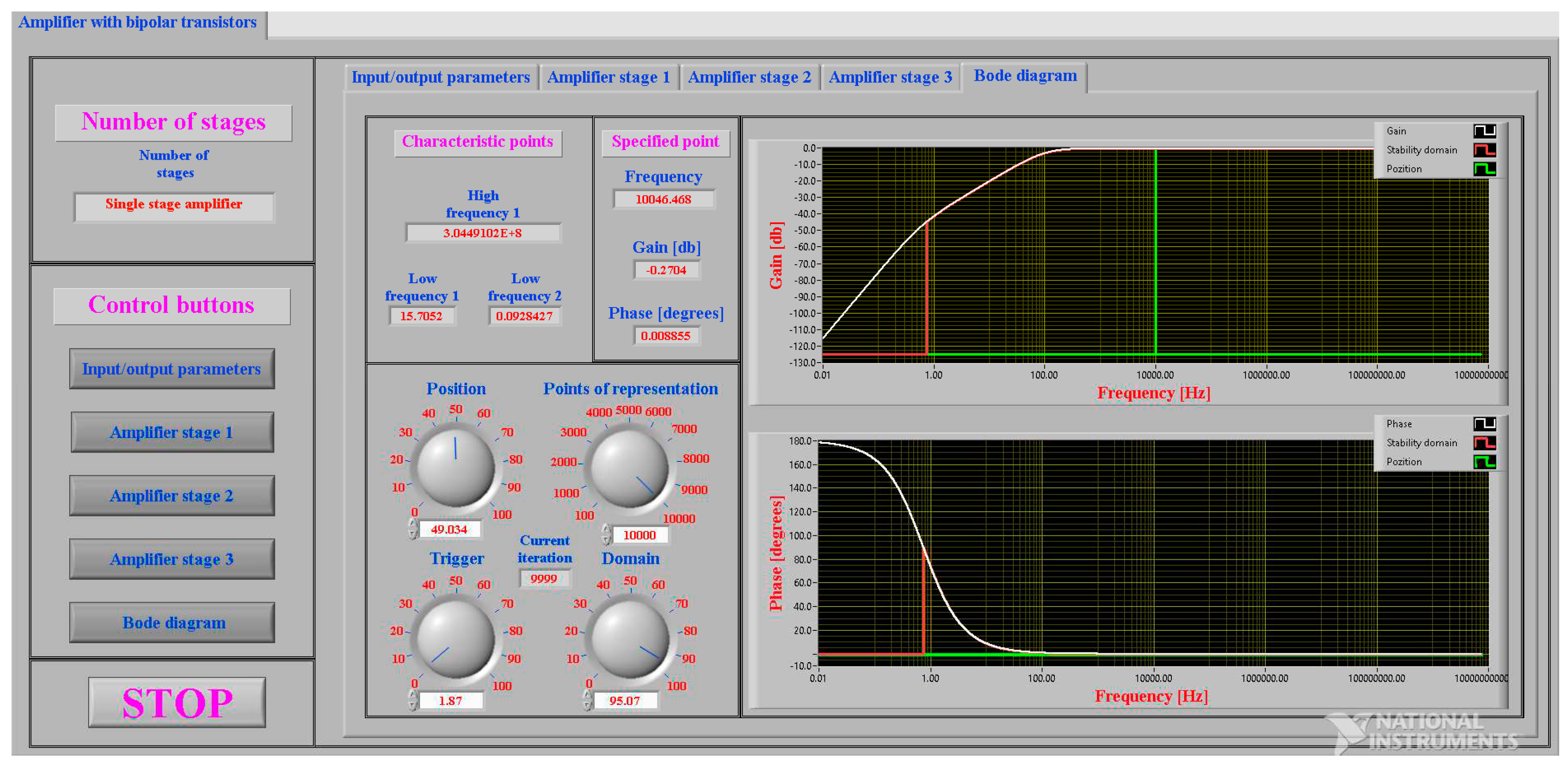

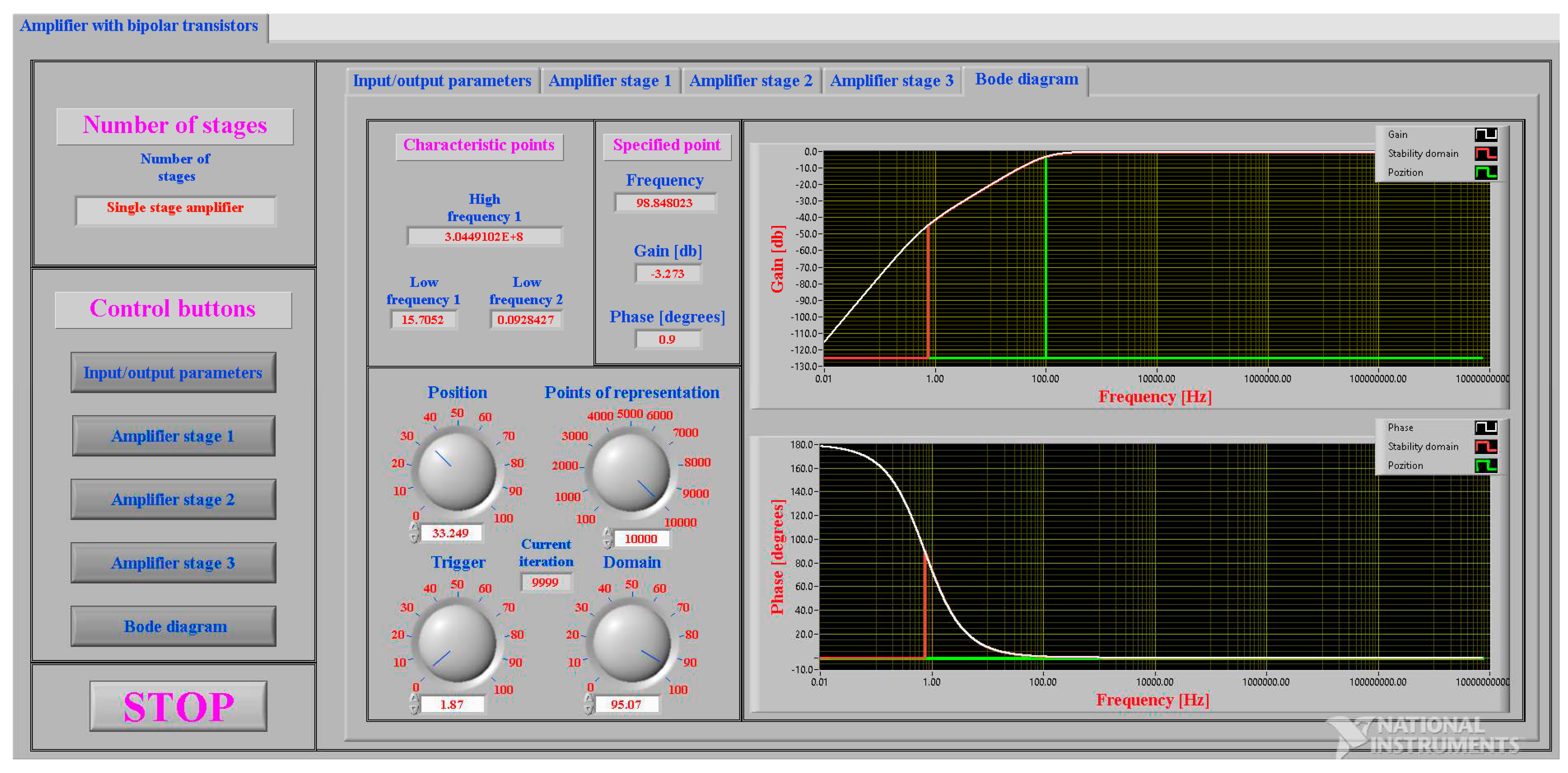

4.2. Simulation and experimentation results for common collector connection

The input parameter values for this connection were chosen, like in previous section, in such a way that the Bode diagram presented two different low pulsations, [

14,

15,

16]. These values are: for generator parameters, R

g = 0.05 kΩ and e

g = 10 mV, for load resistance, Rs = 1 kΩ, for coupling capacitors between the generator and the amplifier stage, C

G = 10 µF and for coupling capacitors between amplifier stage and the load, Cs = 10 µF.

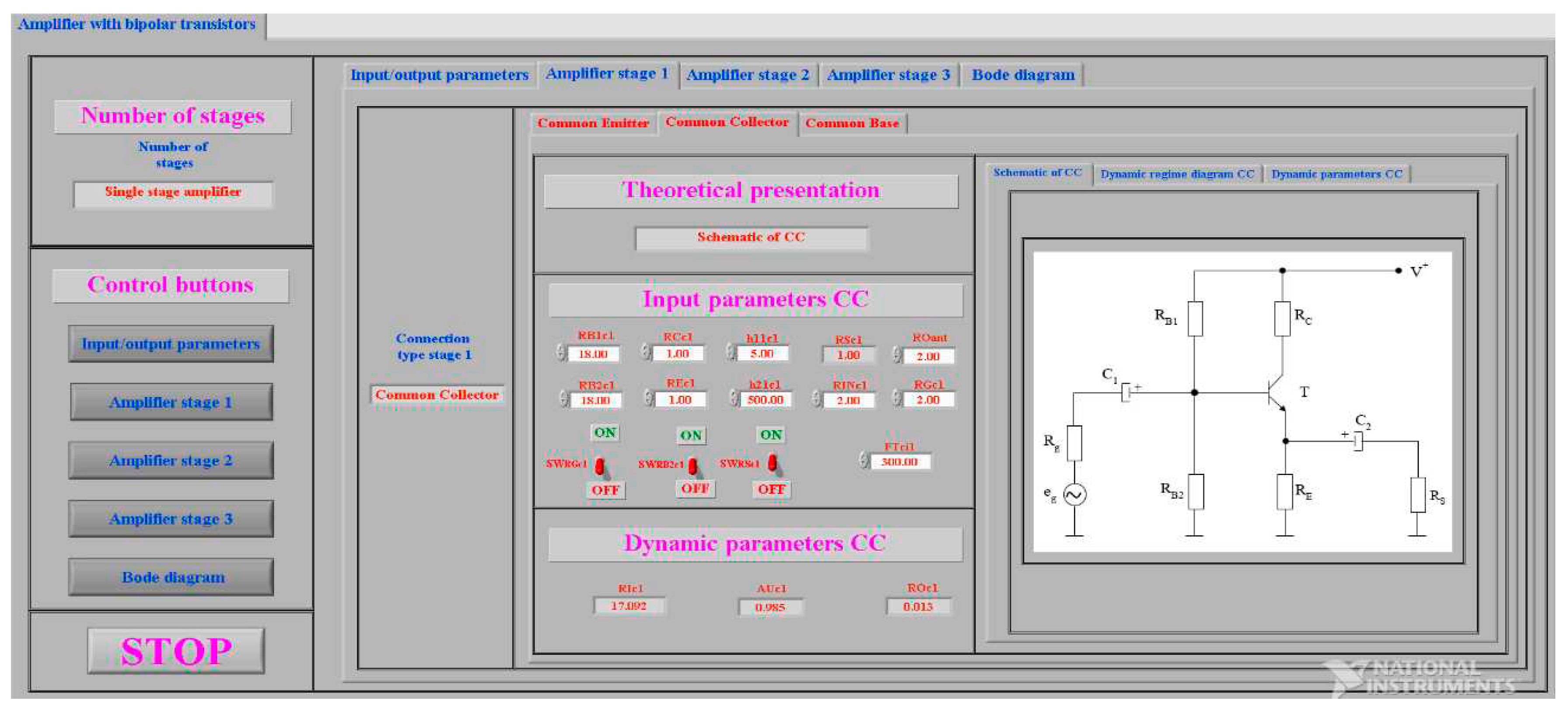

The parameters values for the common collector connection are presented in

Figure 12.

As previously stated, the structure of the amplifier stage can be modified using the switches SW

RGc1, SW

RB2c1 and SW

RSc1.

Table 2 present the values of the output parameters, R

Ic1, A

Uc1 and R

Oc1 for all situations in which SW

RGc1, SW

RB2c1 and SW

RSc1 can be established.

Table 2 reveals some conclusions regarding the effect of the three switches on the values of the output parameters.

1. Selecting the polarization mode of the transistor base with resistive divider by connecting the switch SWRB2c1 in ON state causes the input resistance RIc1 to decrease.

2. None of the three switches have any effect on the AUc1 value.

3. None of the three switches have any effect on the ROc1 value.

The simulation results for common collector connection obtained with Multisim are shown in

Figure 32.

Experimental measurements were performed on a real circuit using an Electronic Explorer Board, which can also be used to determine the Bode characteristics. The measurement results obtained with Electronic Explorer Board are presented in

Figure 33.

A comparison between the simulations and experimental results can be seen in

Figure 34.

Analyzing the gain diagram reveals that the simulation and experimental results are similar at all frequencies.

4.3. Simulation and experimentation results for common base connection

The input parameter values for this connection were chosen, like in previous sections, in such a way that the Bode diagram presented two different low pulsations, [

14,

15,

16]. These values are: for generator parameters, R

g = 0.05 kΩ and e

g = 10 mV, for load resistance, Rs = 10 kΩ, for coupling capacitors between the generator and the amplifier stage, C

G = 1 µF and for coupling capacitors between amplifier stage and the load, Cs = 100 µF.

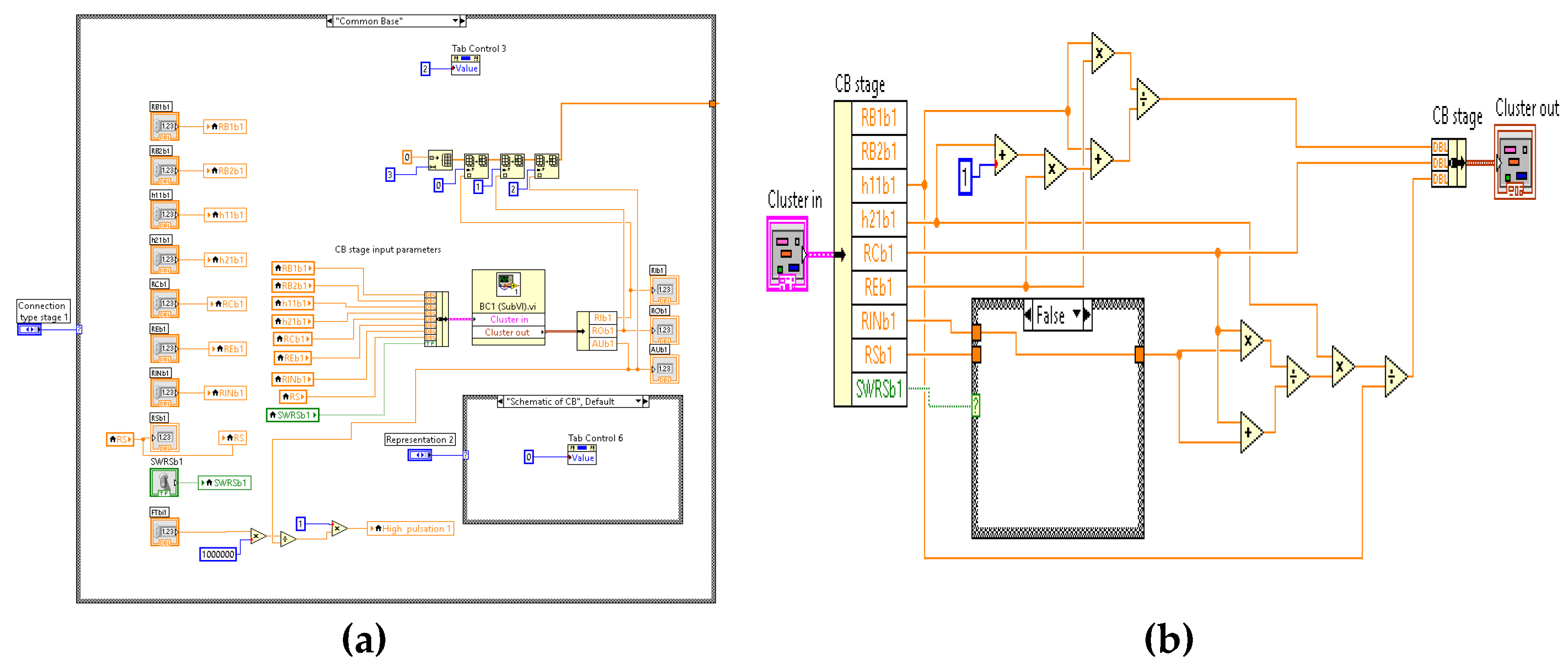

The parameters values for the common base connection are presented in

Figure 15.

As previously stated, the structure of the amplifier stage can be modified using the switch SW

RSb1.

Table 3 present the values of the output parameters, R

Ib1, A

Ub1 and R

Ob1 for the two situations in which SW

RSb1 can be established.

Table 3 reveals some conclusions regarding the effect of the switch SW

RSb1 on the values of the output parameters.

1. The state of the switch SWRSb1 has no effect on the input resistance RIb1 or the output resistance ROb1.

2. The ON state of switch SWRSb1 causes the AUb1 value to increase.

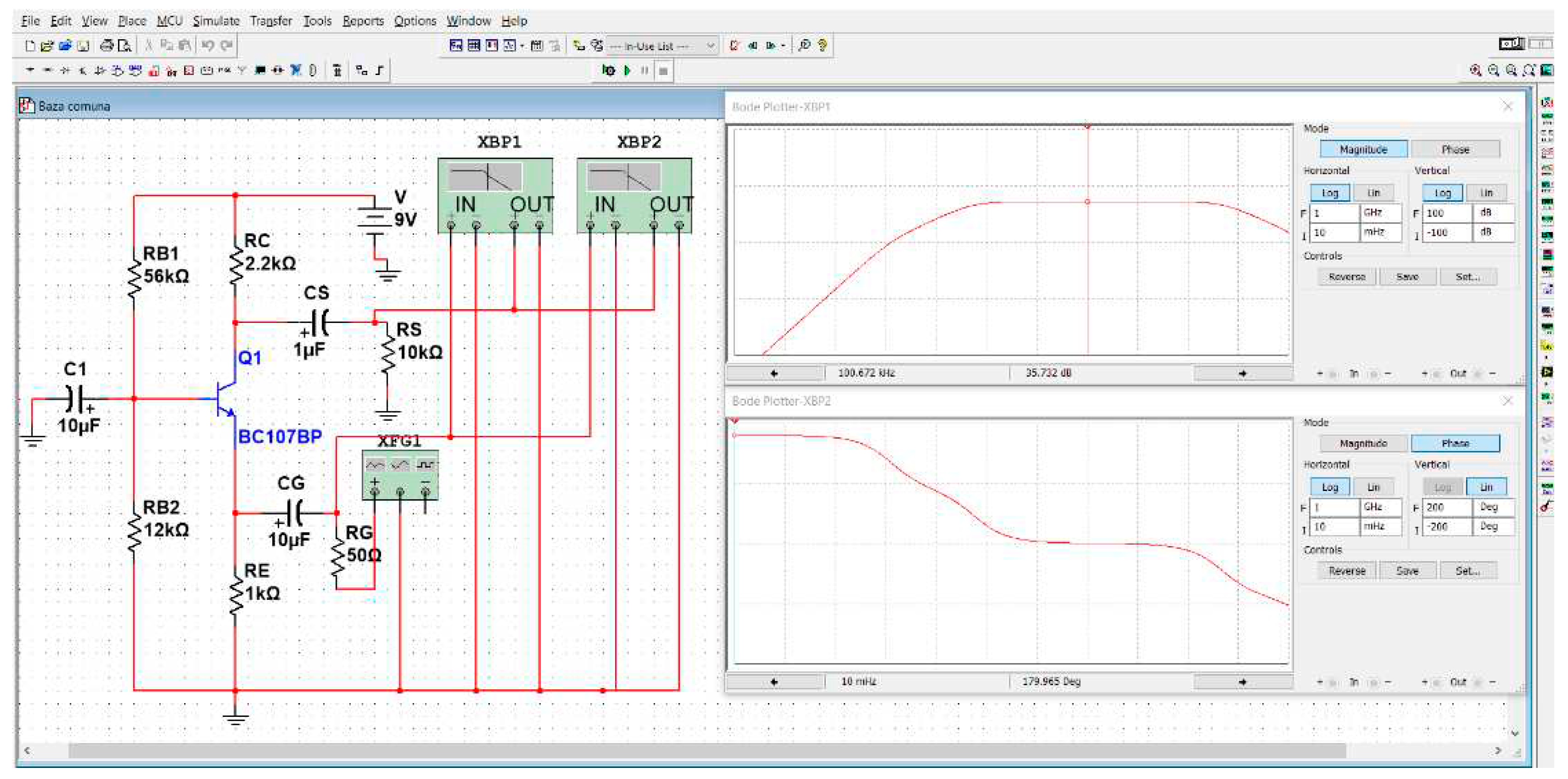

The simulation results obtained with Multisim are shown in

Figure 38.

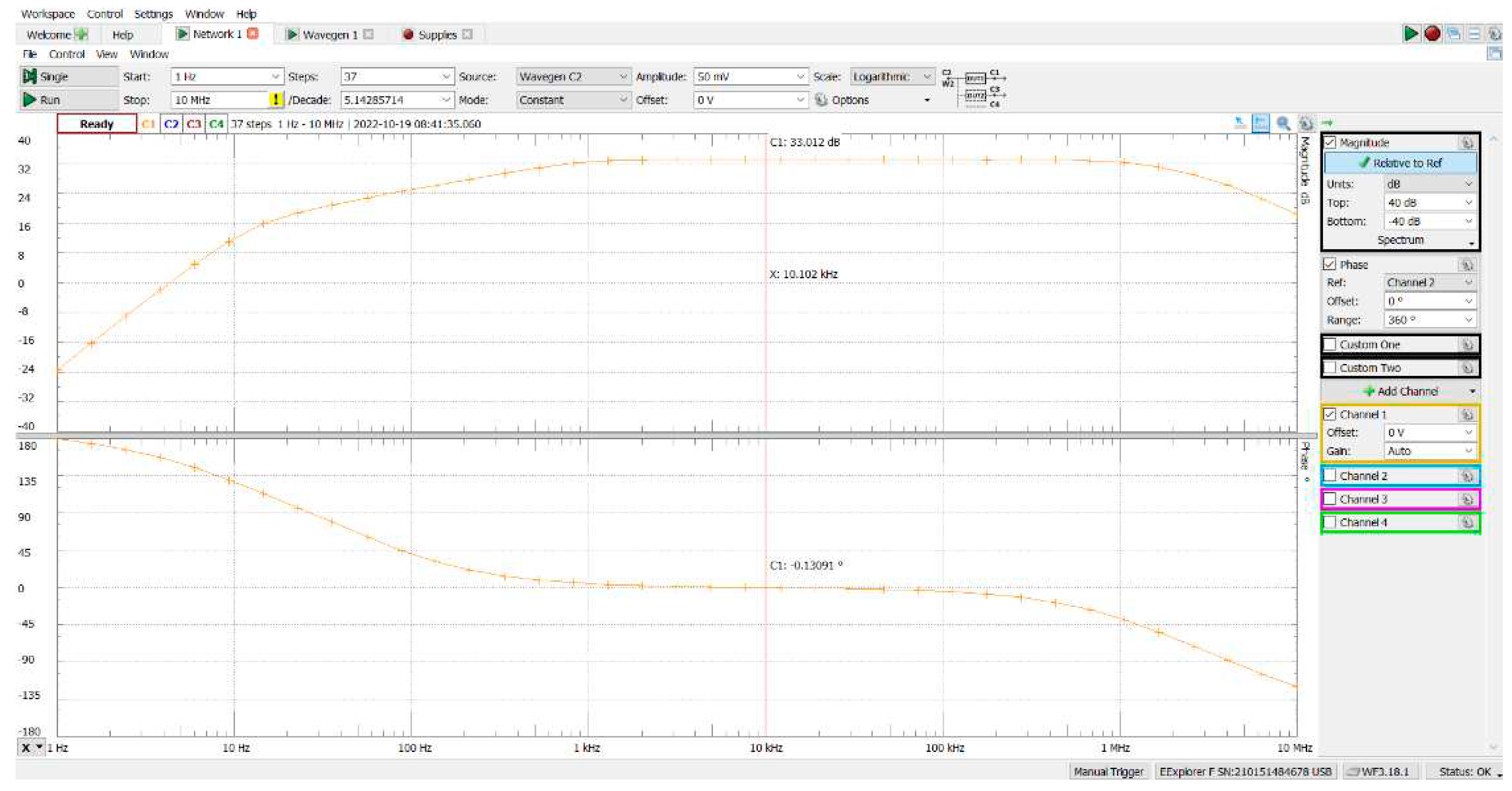

As in previous connections, to validate the simulation results produced by LabVIEW and Multisim, experimental measurements were performed on a real circuit using an Electronic Explorer Board.

The measurement results obtained with Electronic Explorer Board are presented in

Figure 39.

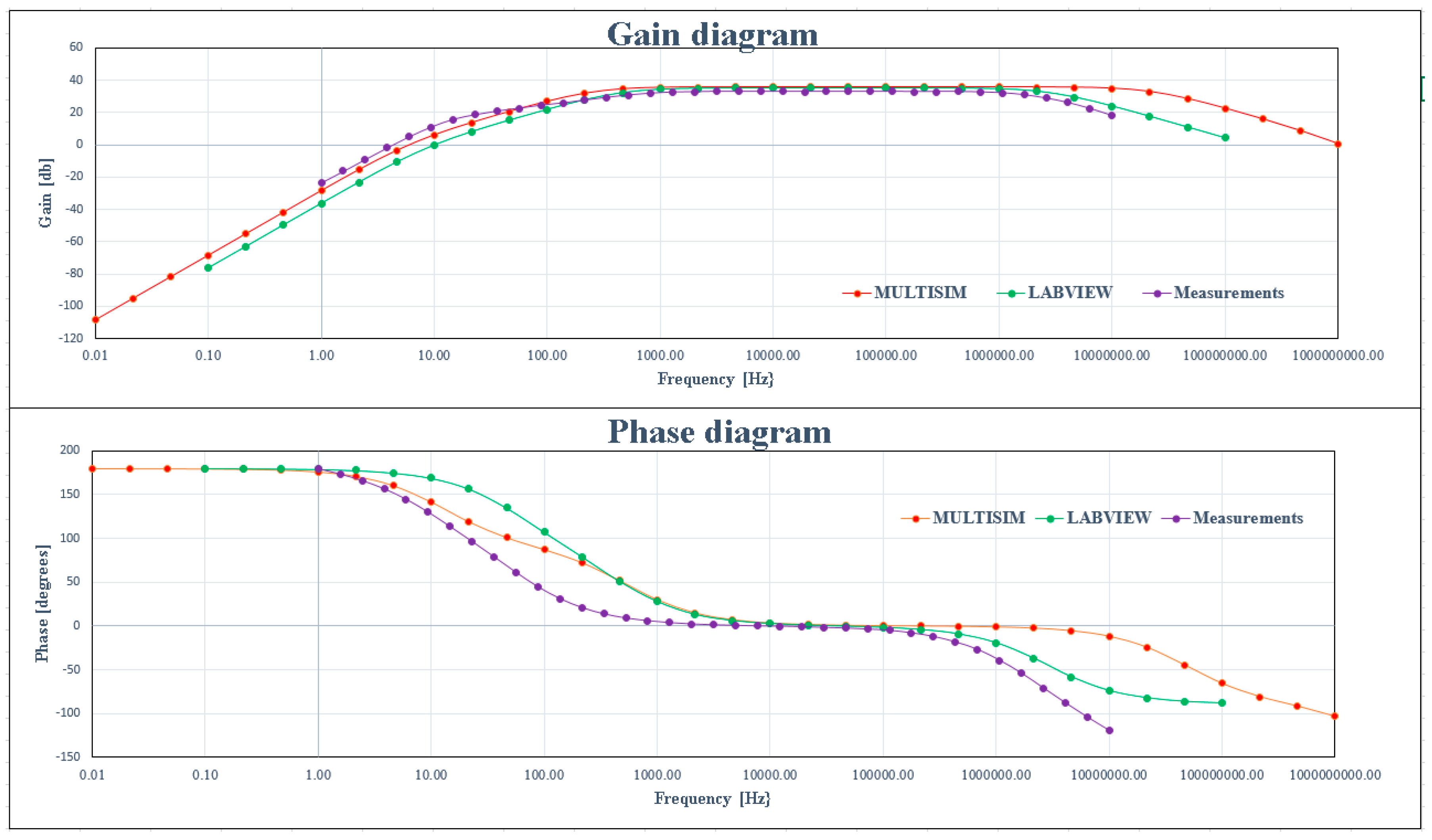

A comparison between the simulations and experimental results can be seen in figure 40.

Analyzing the gain diagram reveals that the simulation and experimental results are similar at low and medium frequencies. At high frequencies the LabVIEW simulations and measurements are nearly identical.

In terms of the phase diagram, both simulations and measurements have the same behavior from 180 to -180 degrees.

5. Conclusions

The investigation of the functionality of an amplifier with discrete components in various connections is a complex process due to the large number of circuit elements whose values influence the amplifier’s output parameters.

This paper describes a LabVIEW application that calculates the output parameters of a single stage amplifier, such as input and output resistance, voltage amplification, gain-frequency and phase-frequency Bode diagrams.

The stage amplifier can be studied in three different configurations: common emitter, common collector and common base. Different transistor polarisation possibilities can be selected for each connection. The application allows for the generation of various transistor polarization schemes by coupling some circuit elements with switches.

The amplifier’s stability zone, as well as the gain and phase amplifier for a given frequency value, can be determined using Bode diagrams.

A specified single stage amplifier can be designed by changing both the configuration of the amplifier as well as the value of some circuit element.

Because the application allows each connection to visualize the electronic scheme, the mathematical relations for determining the output parameters, and the dynamical scheme, it can be used for educational purposes.

In order to validate the simulation results using the LabVIEW application, a specialized program Multisim was used, as well as experimental measurements using the Electronics Explorer Board. Both Multisim and Electronics Explorer Board can determine Bode characteristics. In both simulations and experimental amplifiers, the same schemes with the same transistor was used.

This paper demonstrated that the LabVIEW application can produce similar simulate results using Multisim and also measured results using Electronics Explorer Board.The application described in this article is an innovative type tool that may be used as a learning tool because it performs circuit analysis in simulation software and experiments comparisons.

Figure 1.

The equivalent circuit of the amplifier stage using the quadrupole ”h” parameters.

Figure 1.

The equivalent circuit of the amplifier stage using the quadrupole ”h” parameters.

Figure 2.

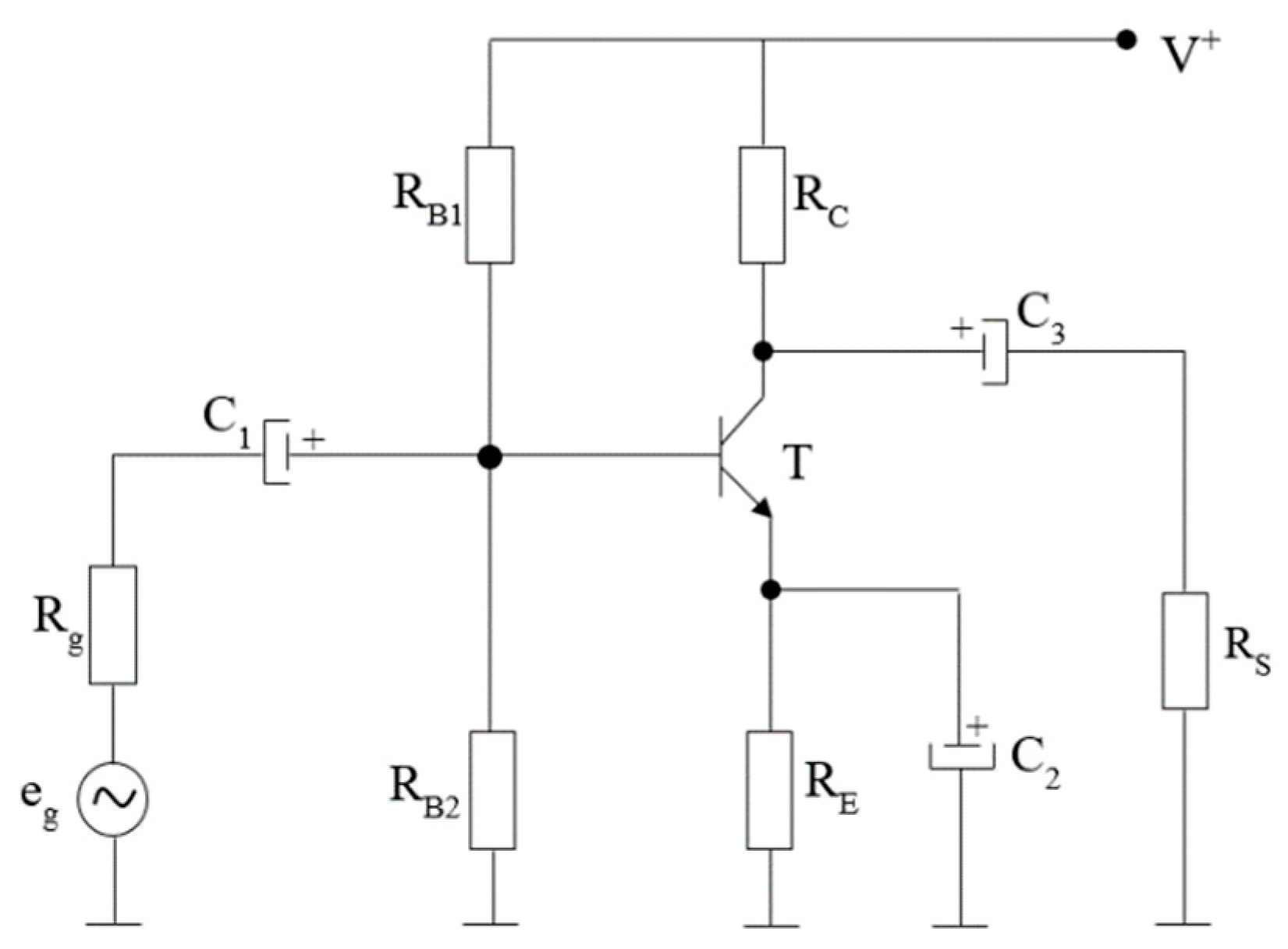

Electronic scheme for common emitter connection.

Figure 2.

Electronic scheme for common emitter connection.

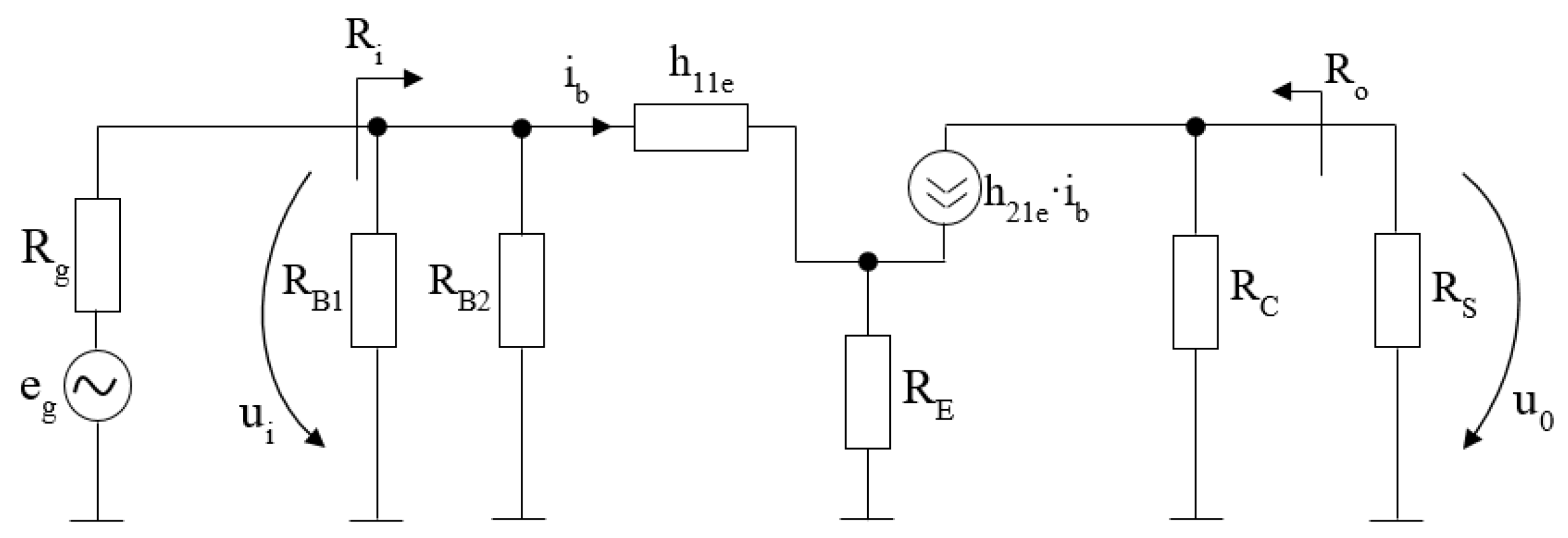

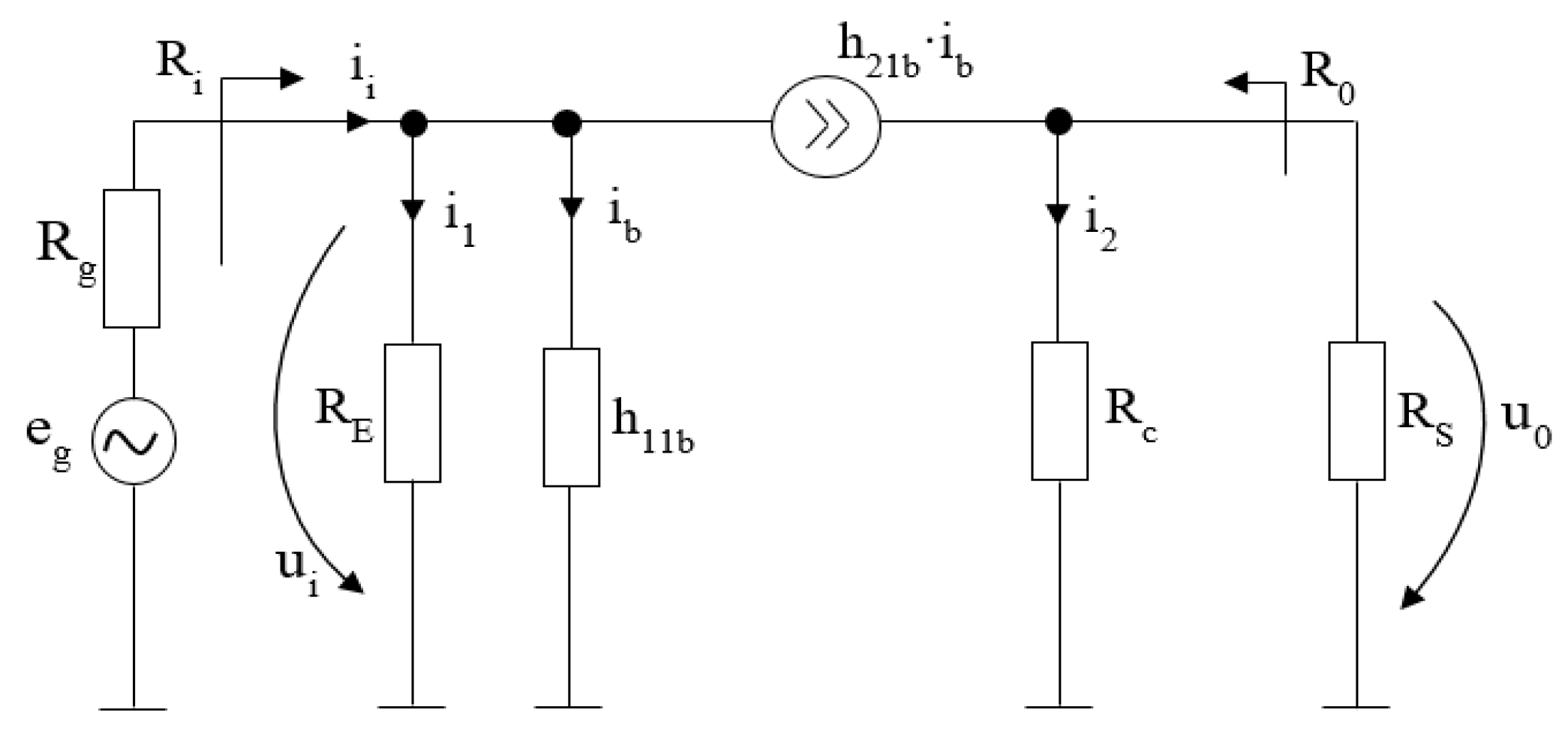

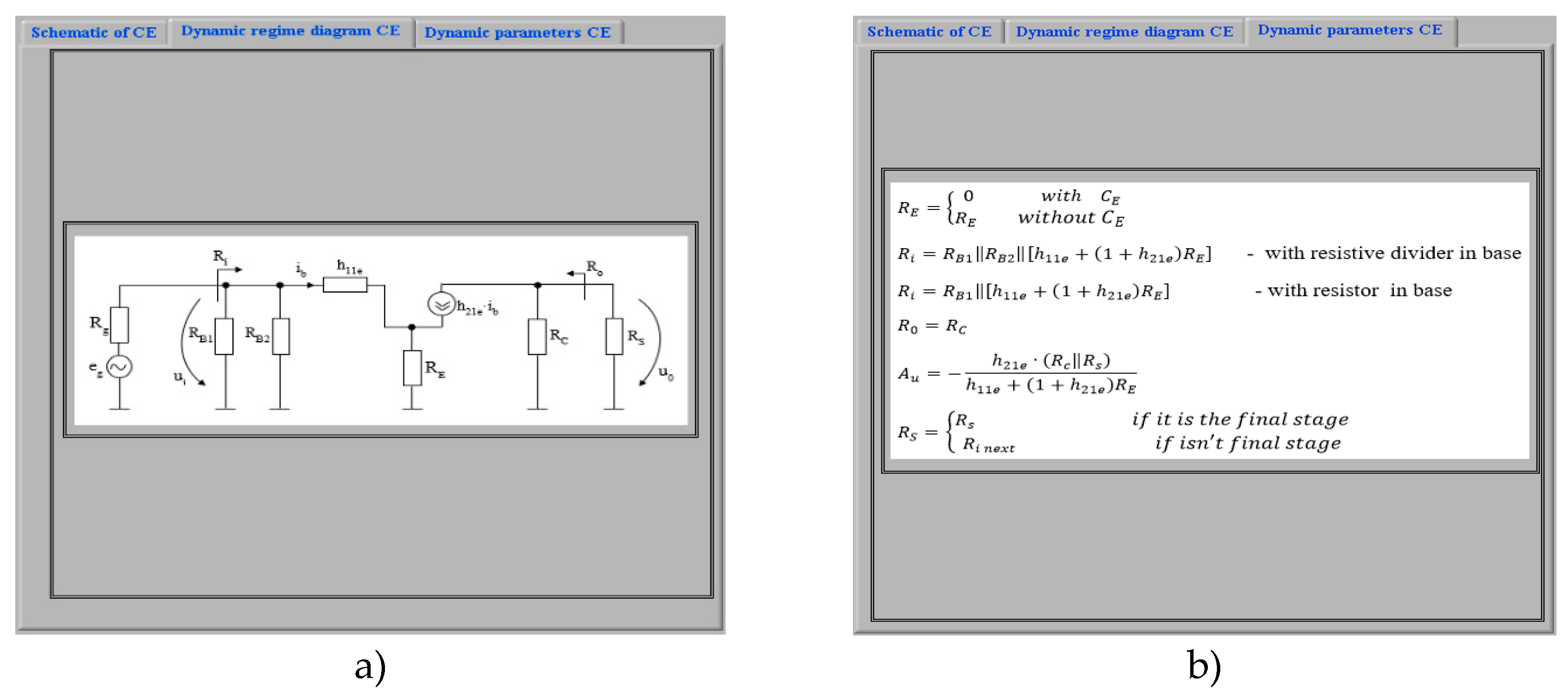

Figure 3.

The equivalent scheme in dynamical regime for common emitter connection.

Figure 3.

The equivalent scheme in dynamical regime for common emitter connection.

Figure 4.

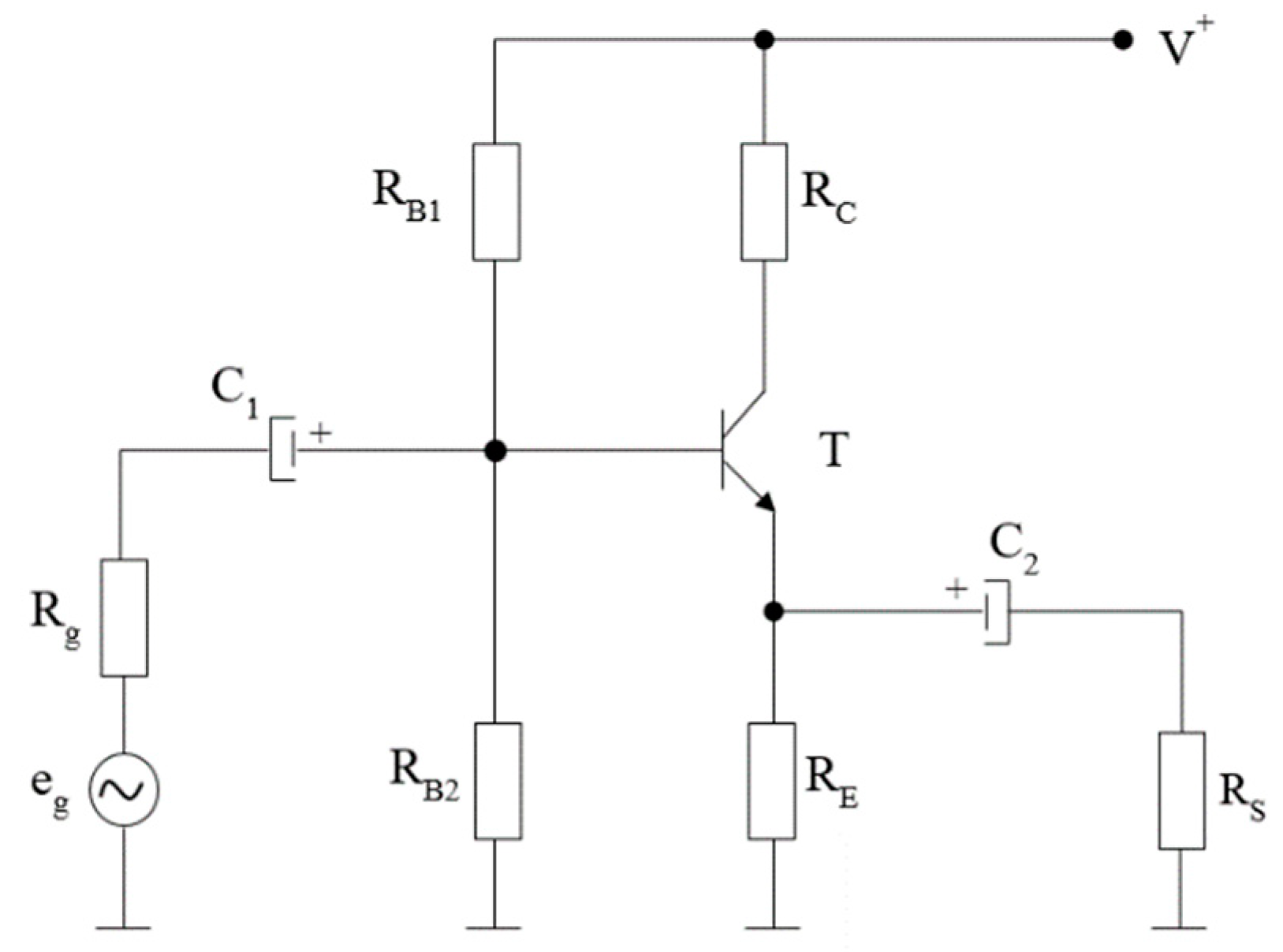

Electronic scheme for common collector connection.

Figure 4.

Electronic scheme for common collector connection.

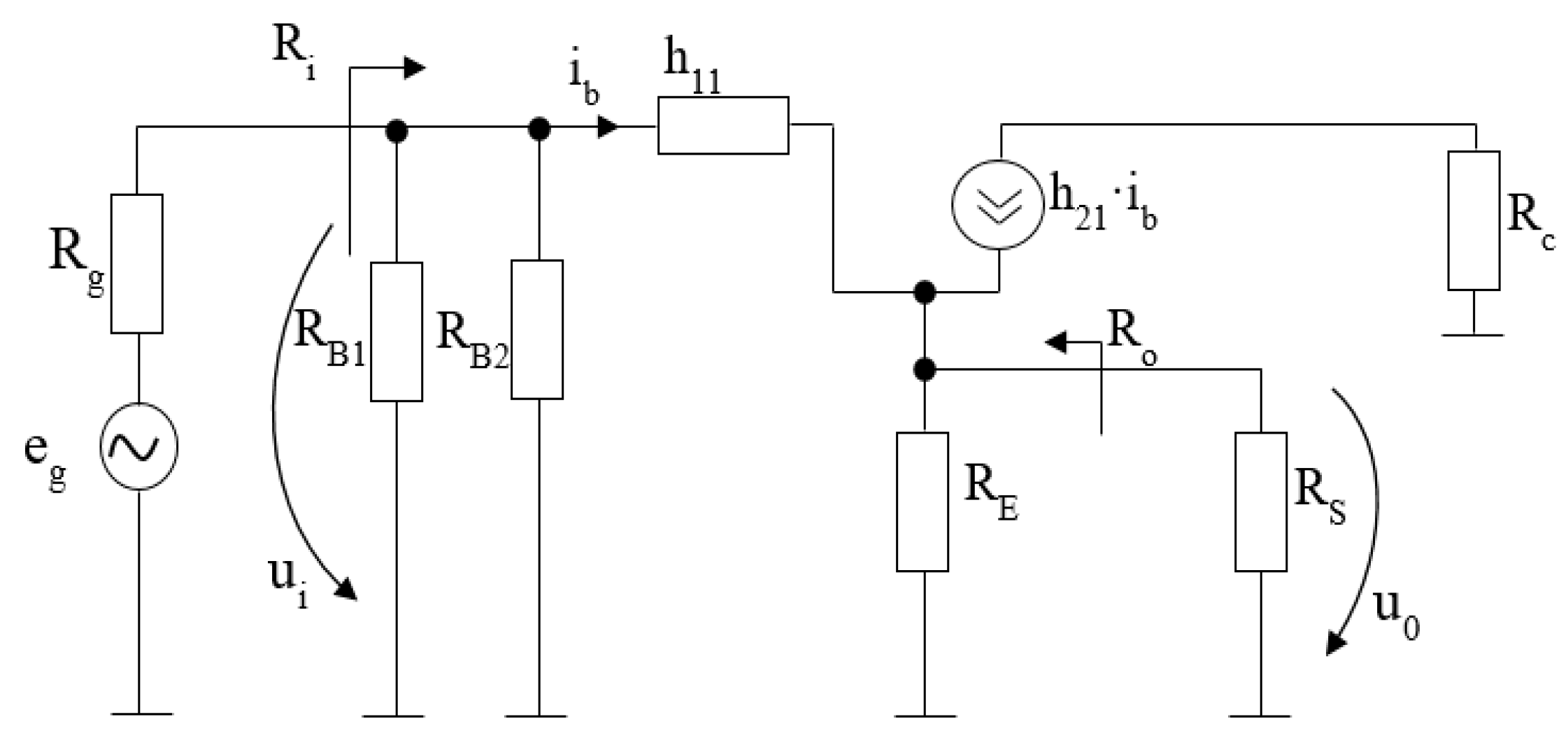

Figure 5.

The equivalent scheme in dynamical regime for common collector connection.

Figure 5.

The equivalent scheme in dynamical regime for common collector connection.

Figure 6.

Electronic scheme for common base connection.

Figure 6.

Electronic scheme for common base connection.

Figure 7.

The equivalent scheme in dynamical regime for common base connection.

Figure 7.

The equivalent scheme in dynamical regime for common base connection.

Figure 8.

Front panel for input/output parameters.

Figure 8.

Front panel for input/output parameters.

Figure 9.

Front panel for common emitter stage parameters.

Figure 9.

Front panel for common emitter stage parameters.

Figure 10.

a) Dynamic regime diagram CE, b) Dynamic parameters CE.

Figure 10.

a) Dynamic regime diagram CE, b) Dynamic parameters CE.

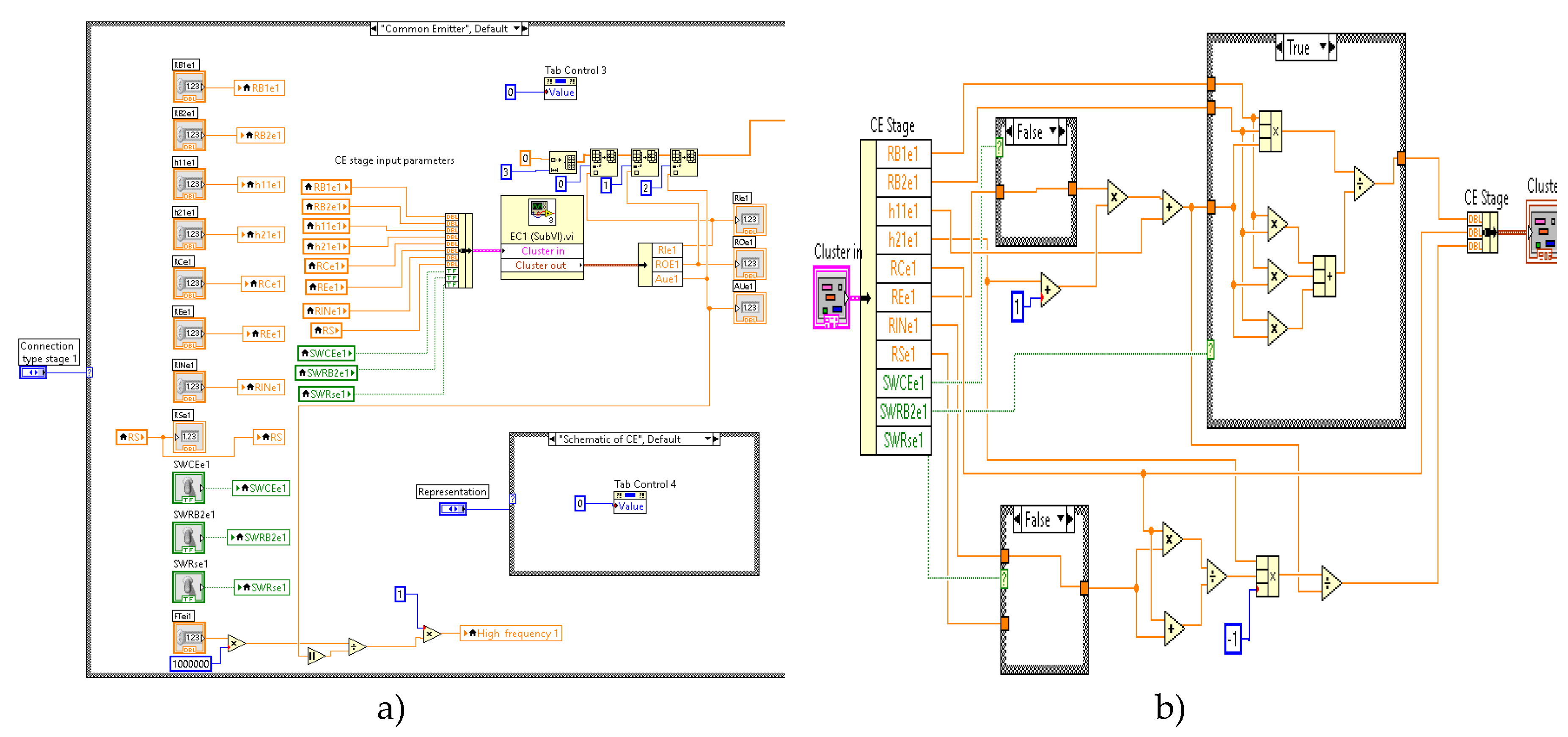

Figure 11.

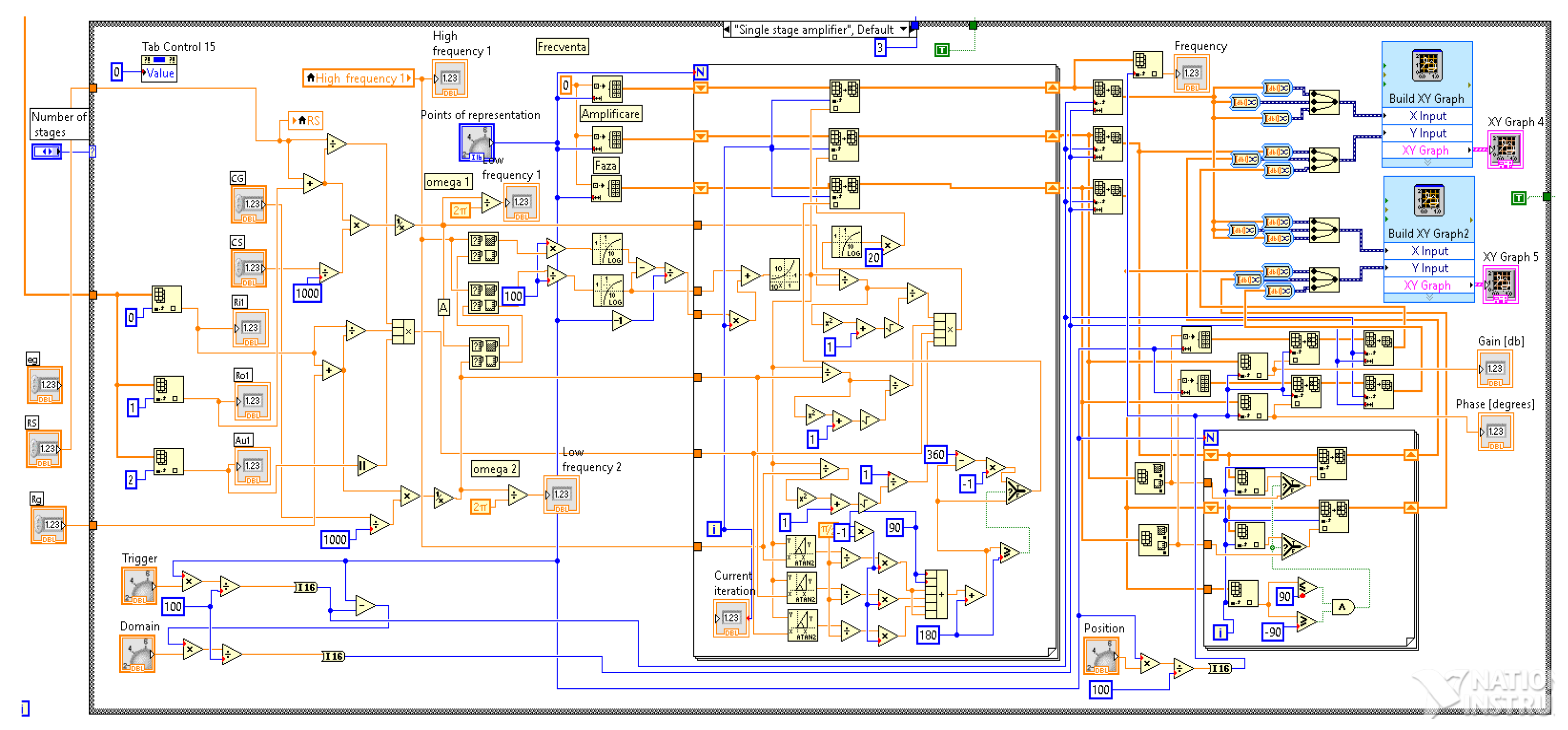

a) Program implementation of computed parameters, b) Subroutine EC1.

Figure 11.

a) Program implementation of computed parameters, b) Subroutine EC1.

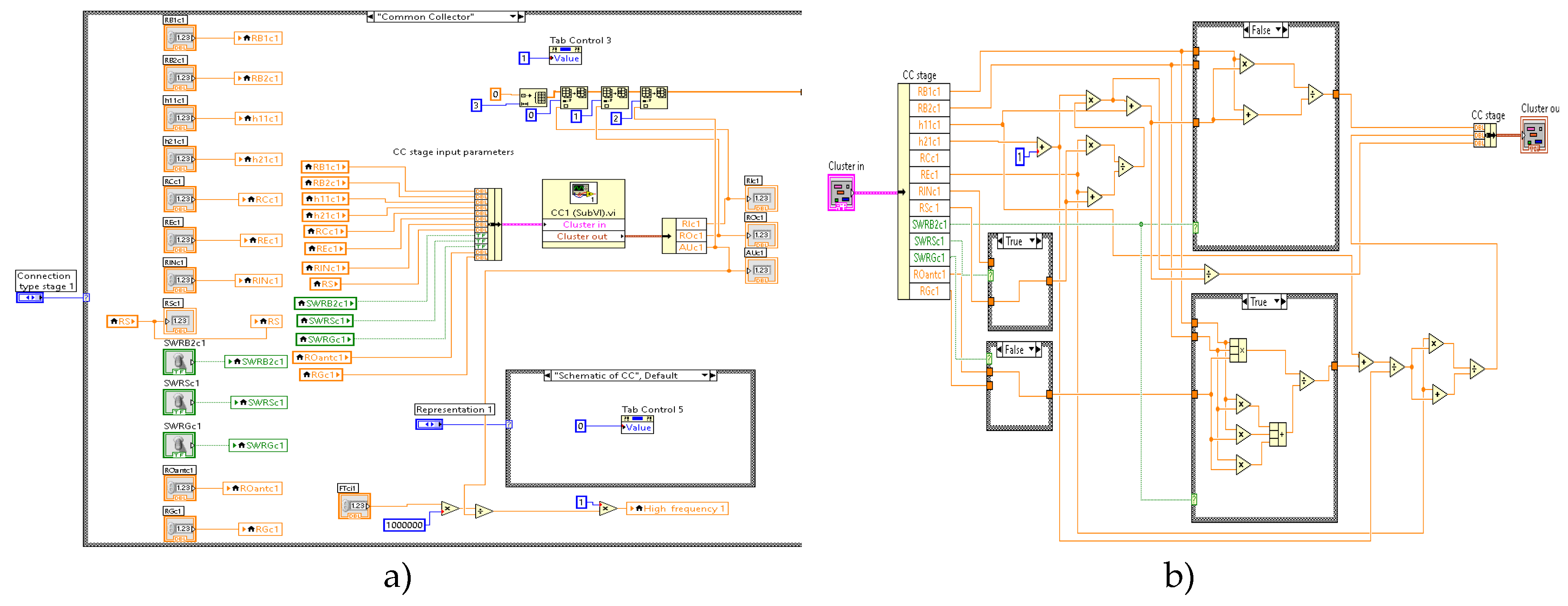

Figure 12.

Front panel for common collector stage parameters.

Figure 12.

Front panel for common collector stage parameters.

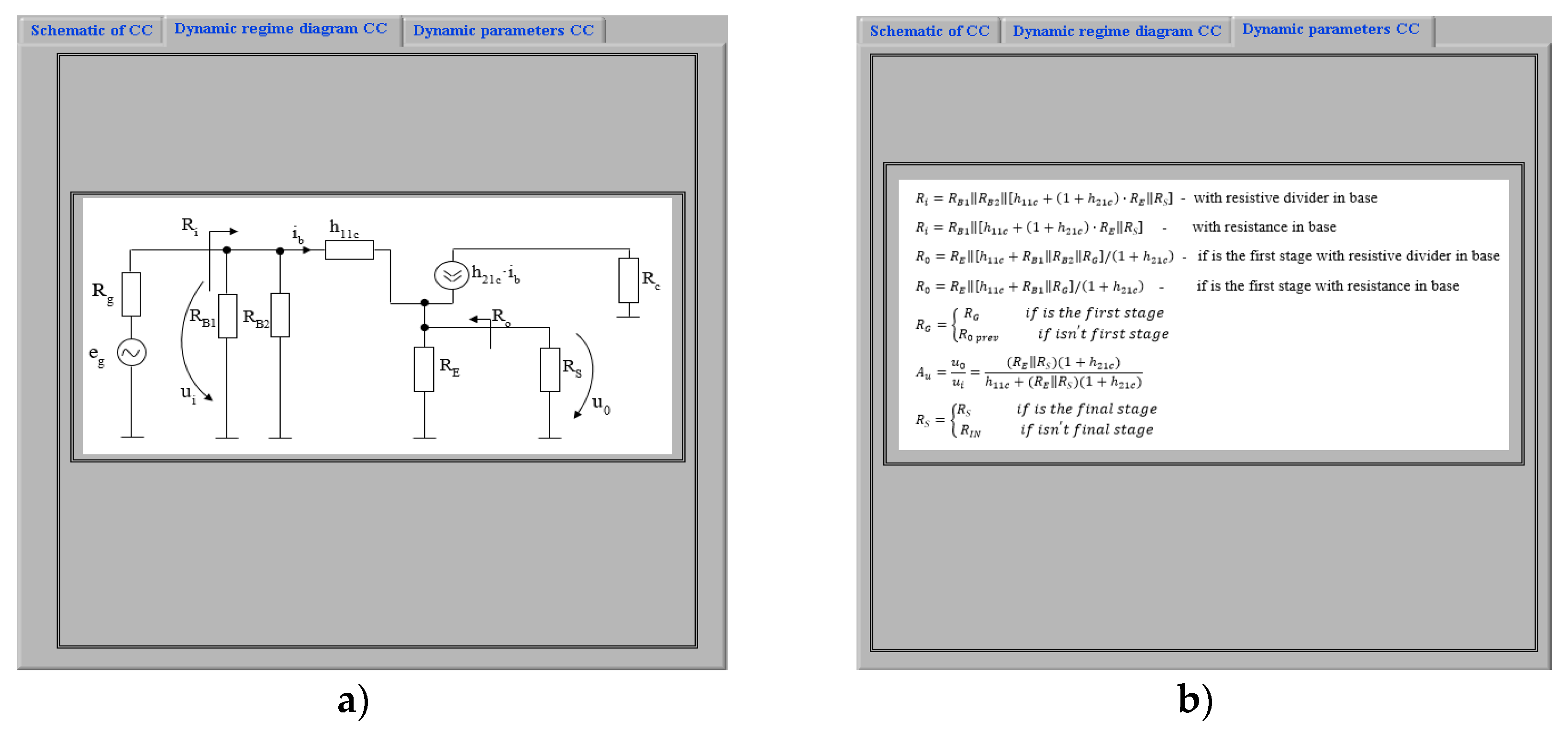

Figure 13.

a) Dynamic regime diagram CC, b) Dynamic parameters CC.

Figure 13.

a) Dynamic regime diagram CC, b) Dynamic parameters CC.

Figure 14.

a) Program implementation of computed parameters, b) Subroutine CC1.

Figure 14.

a) Program implementation of computed parameters, b) Subroutine CC1.

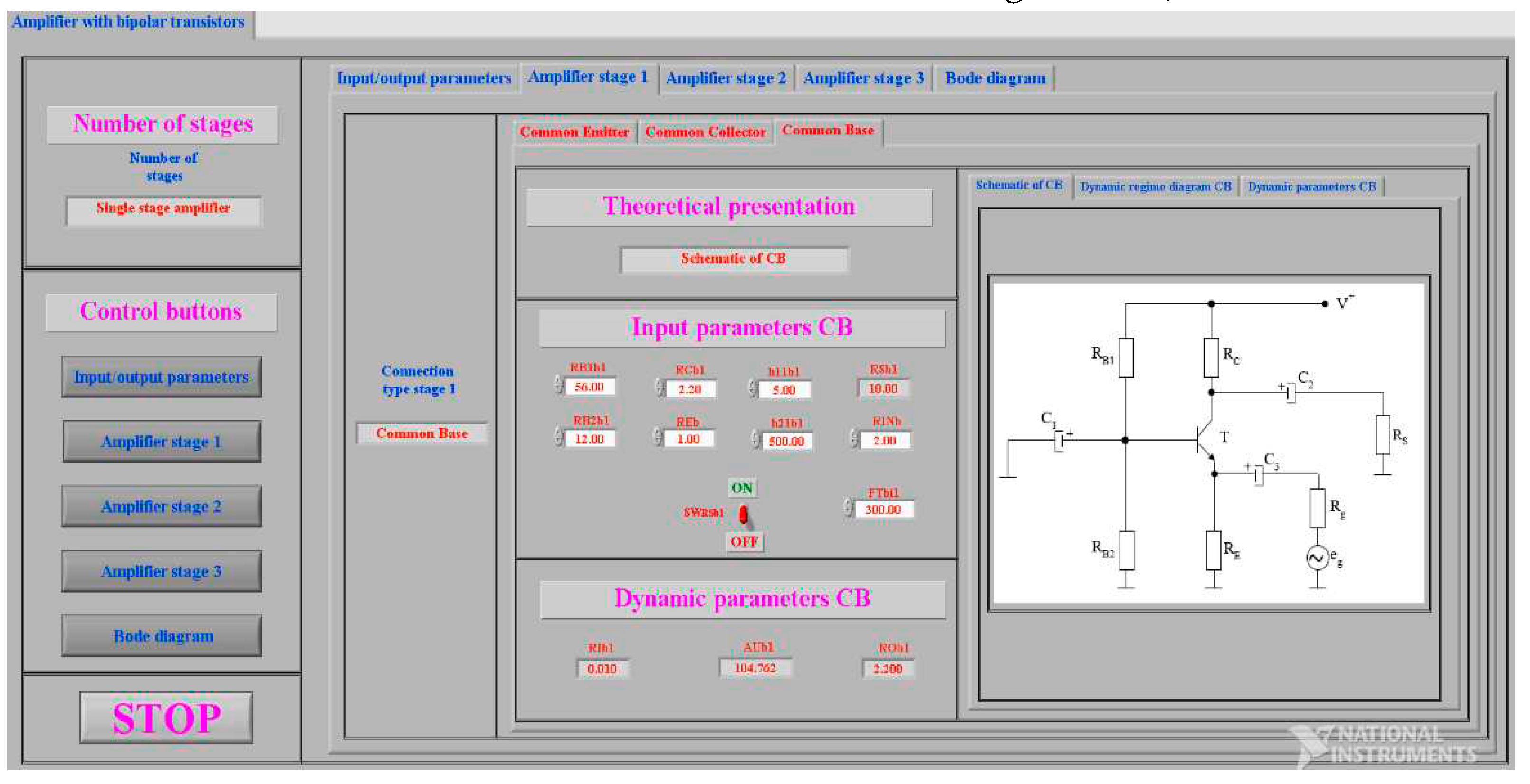

Figure 15.

Front panel for common base stage parameters.

Figure 15.

Front panel for common base stage parameters.

Figure 16.

a) Dynamic regime diagram CB, b) Dynamic parameters CB.

Figure 16.

a) Dynamic regime diagram CB, b) Dynamic parameters CB.

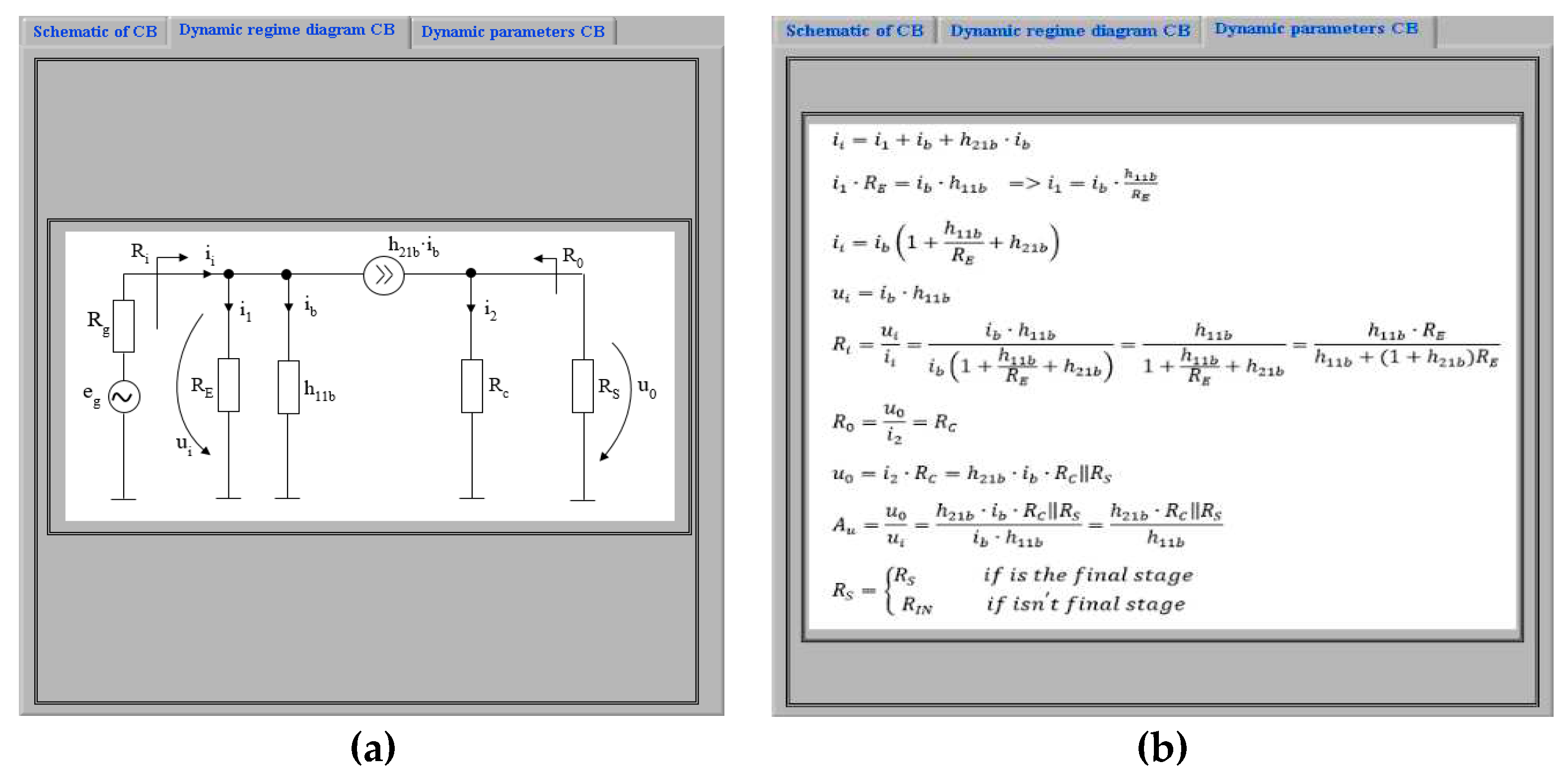

Figure 17.

a) Program implementation of computed parameters, b) Subroutine BC1.

Figure 17.

a) Program implementation of computed parameters, b) Subroutine BC1.

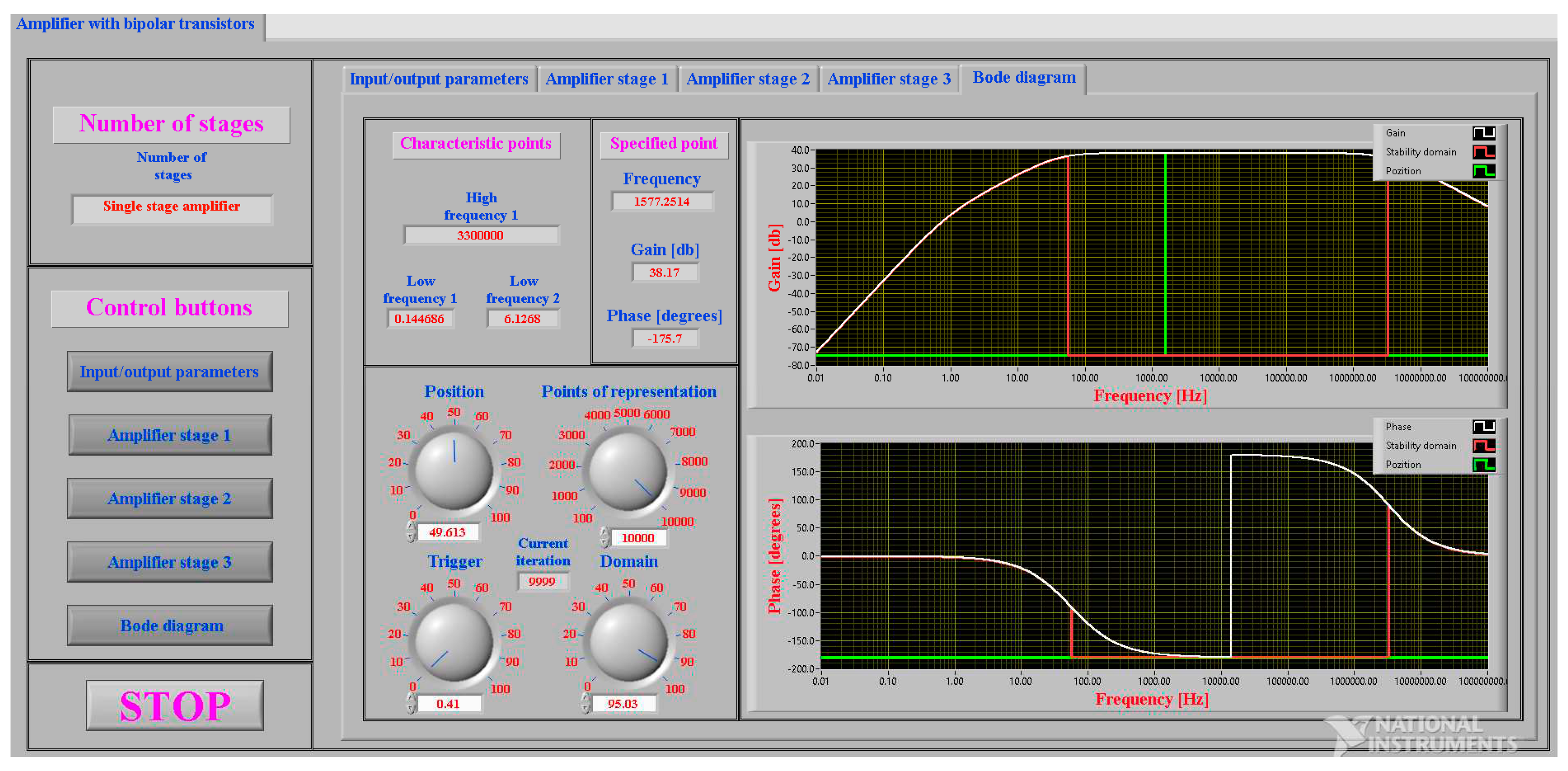

Figure 18.

Bode diagram menu.

Figure 18.

Bode diagram menu.

Figure 19.

Program implementation of Bode diagram menu.

Figure 19.

Program implementation of Bode diagram menu.

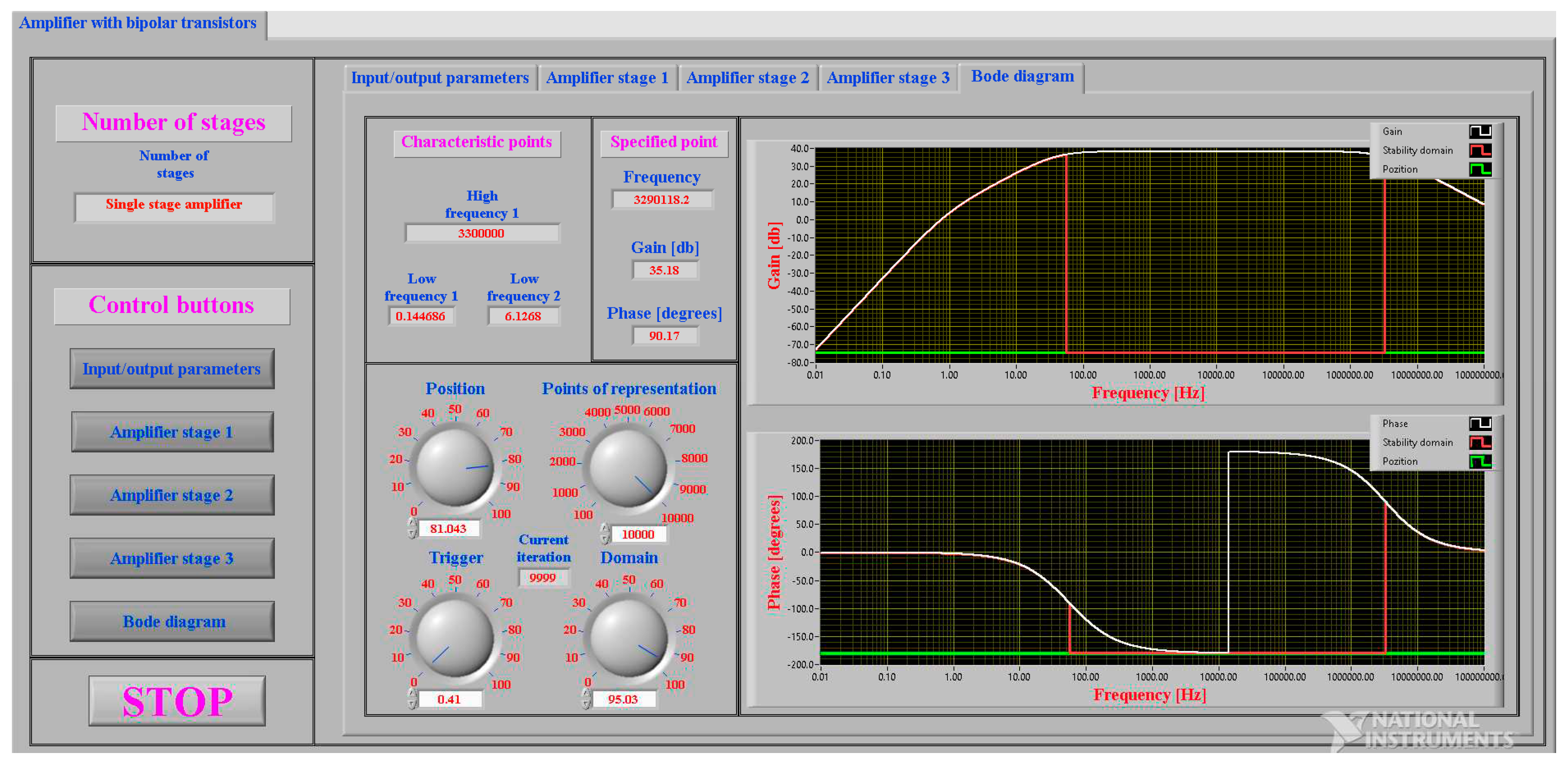

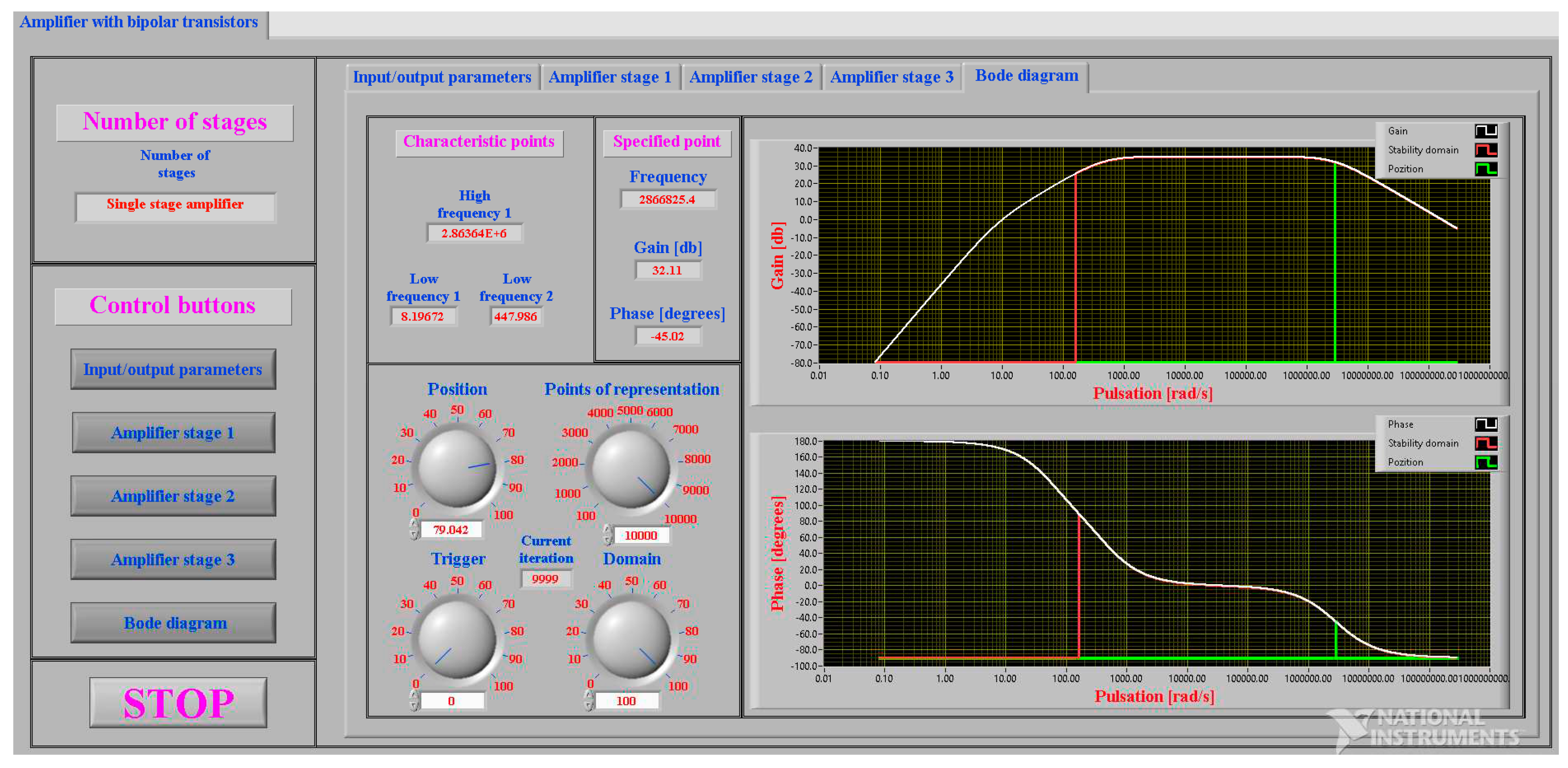

Figure 20.

Bode diagram for line 8 from

Table 1, for SW

CEe1 to ON, for 10 kHz frequency.

Figure 20.

Bode diagram for line 8 from

Table 1, for SW

CEe1 to ON, for 10 kHz frequency.

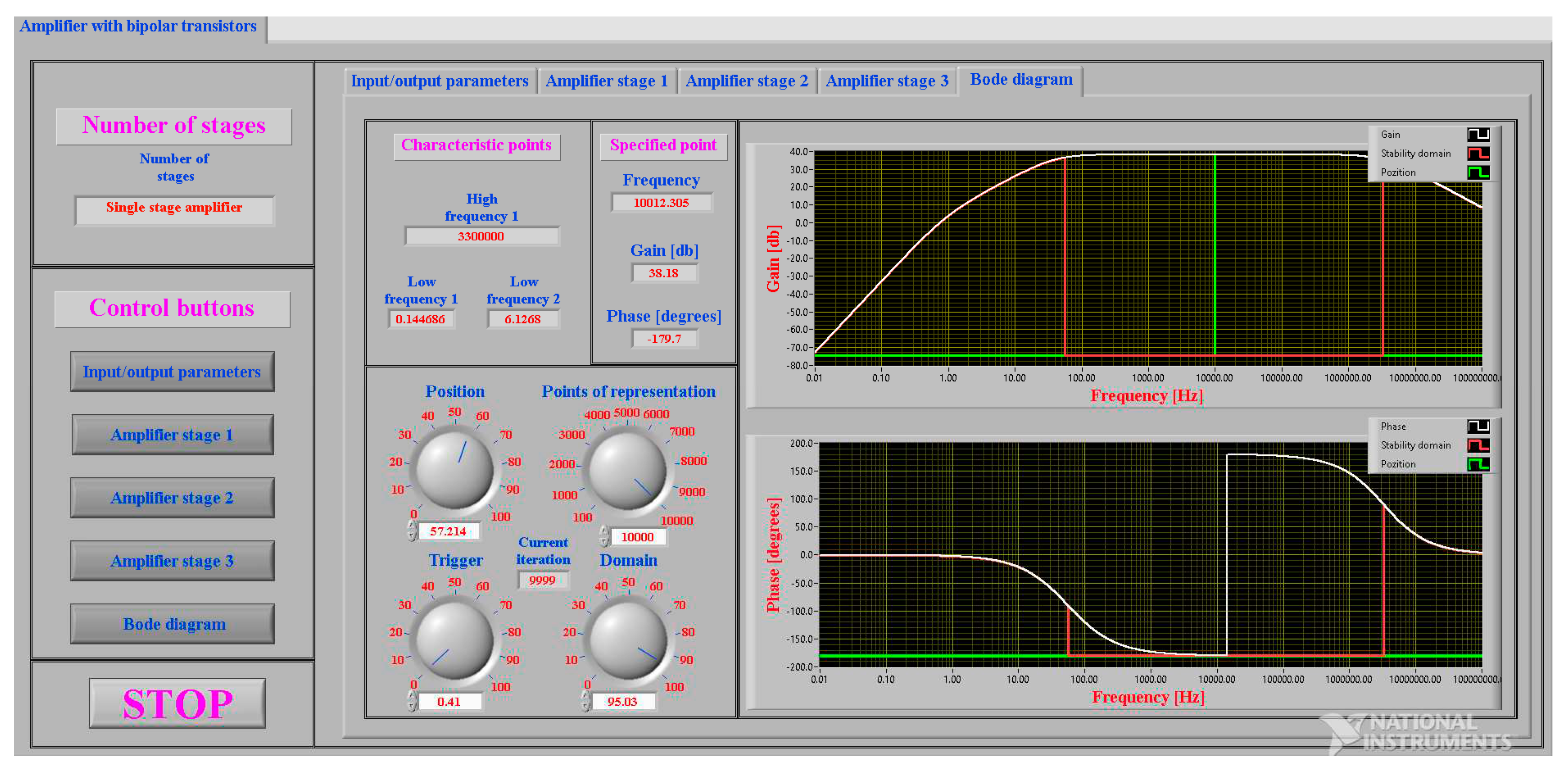

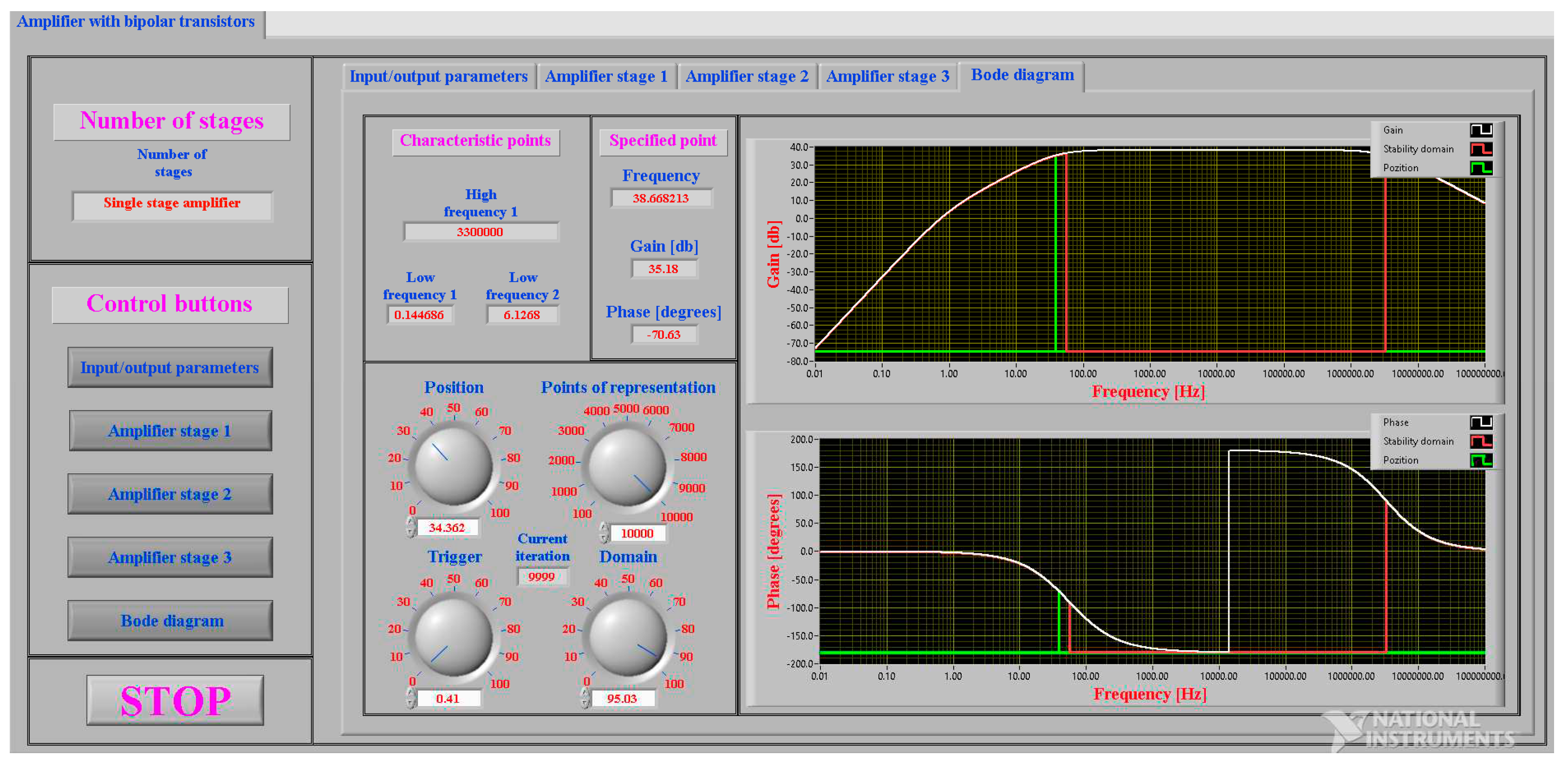

Figure 21.

Bode diagram for line 8 from

Table 1, for SW

CEe1 to ON, for low cut frequency of 38.66 Hz.

Figure 21.

Bode diagram for line 8 from

Table 1, for SW

CEe1 to ON, for low cut frequency of 38.66 Hz.

Figure 22.

Bode diagram for line 8 from

Table 1, for SW

CEe1 to ON, for high cut frequency of 3.29 MHz.

Figure 22.

Bode diagram for line 8 from

Table 1, for SW

CEe1 to ON, for high cut frequency of 3.29 MHz.

Figure 23.

Simulation results for common emitter connection, for SWCEe1 to ON, using Multisim.

Figure 23.

Simulation results for common emitter connection, for SWCEe1 to ON, using Multisim.

Figure 24.

Measurement results for common emitter connection, for SWCEe1 to ON, using Electronic Explorer Board.

Figure 24.

Measurement results for common emitter connection, for SWCEe1 to ON, using Electronic Explorer Board.

Figure 25.

Simulations and experimental results for common emitter connection, for SWCEe1 to ON.

Figure 25.

Simulations and experimental results for common emitter connection, for SWCEe1 to ON.

Figure 29.

Simulations and experimental results for common emitter connection, for SWCEe1 to OFF.

Figure 29.

Simulations and experimental results for common emitter connection, for SWCEe1 to OFF.

Figure 30.

Bode diagram for line 5 from

Table 2, for 10 kHz frequency.

Figure 30.

Bode diagram for line 5 from

Table 2, for 10 kHz frequency.

Figure 31.

Bode diagram for line 5 from

Table 2, for low cut pulsations of 98.85 Hz.

Figure 31.

Bode diagram for line 5 from

Table 2, for low cut pulsations of 98.85 Hz.

Figure 32.

Simulation results for common collector connection, using Multisim.

Figure 32.

Simulation results for common collector connection, using Multisim.

Figure 33.

Measurement results for common collector connection, using Electronic Explorer Board.

Figure 33.

Measurement results for common collector connection, using Electronic Explorer Board.

Figure 34.

Simulations and experimental results for common collector connection.

Figure 34.

Simulations and experimental results for common collector connection.

Figure 35.

Bode diagram for line 1 from

Table 3, for 10 kHz frequency.

Figure 35.

Bode diagram for line 1 from

Table 3, for 10 kHz frequency.

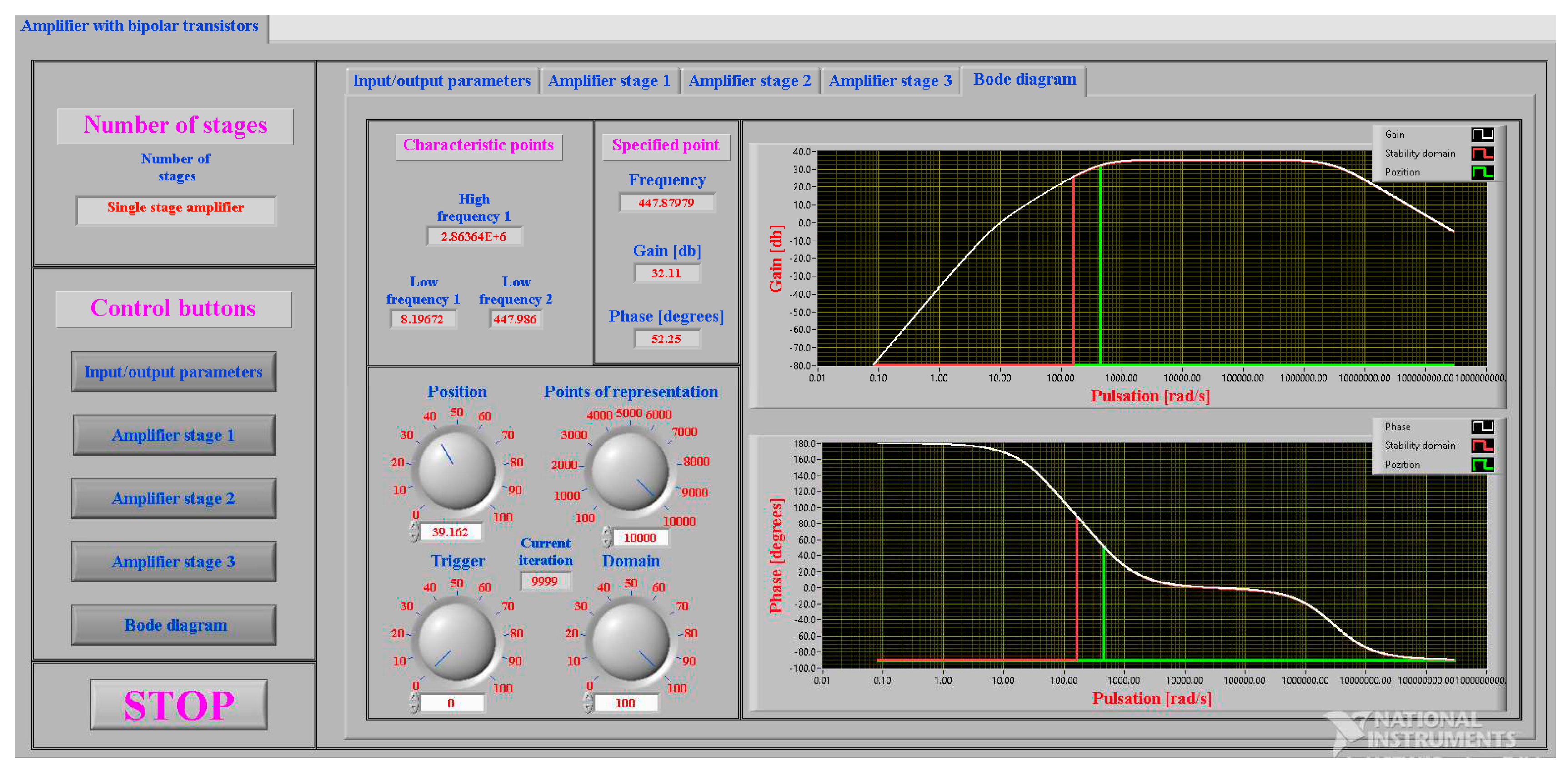

Figure 36.

Bode diagram for line 1 from

Table 3, for low cut pulsations of 447.9 Hz.

Figure 36.

Bode diagram for line 1 from

Table 3, for low cut pulsations of 447.9 Hz.

Figure 37.

Bode diagram for line 1 from

Table 3, for high cut pulsations of 2.86 MHz.

Figure 37.

Bode diagram for line 1 from

Table 3, for high cut pulsations of 2.86 MHz.

Figure 38.

Simulation results for common base connection, using Multisim.

Figure 38.

Simulation results for common base connection, using Multisim.

Figure 39.

Measurement results for common base connection, using Electronic Explorer Board.

Figure 39.

Measurement results for common base connection, using Electronic Explorer Board.

Figure 40.

Simulations and experimental results for common base connection.

Figure 40.

Simulations and experimental results for common base connection.

Table 1.

The values of the output parameters.

Table 1.

The values of the output parameters.

| |

SWRB2e1

|

SWRSe1

|

RIe1 [KΩ] |

AUe1

|

ROe1 [KΩ] |

| OFF |

OFF |

OFF |

20.426 |

-1.167 |

1.000 |

| OFF |

OFF |

ON |

20.426 |

-1.592 |

1.000 |

| OFF |

ON |

OFF |

5.102 |

-1.167 |

1.000 |

| OFF |

ON |

ON |

5.102 |

-1.592 |

1.000 |

| ON |

OFF |

OFF |

4.074 |

-66.667 |

1.000 |

| ON |

OFF |

ON |

4.074 |

-90.909 |

1.000 |

| ON |

ON |

OFF |

2.548 |

-66.667 |

1.000 |

| ON |

ON |

ON |

2.548 |

-90.909 |

1.000 |

Table 2.

The values of the output parameters.

Table 2.

The values of the output parameters.

| SWRGc1

|

SWRB2c1

|

SWRSc1

|

RIc1 [KΩ] |

AUc1

|

ROc1 [KΩ] |

| OFF |

OFF |

OFF |

17.092 |

0.985 |

0.013 |

| OFF |

OFF |

ON |

16.815 |

0.980 |

0.013 |

| OFF |

ON |

OFF |

8.767 |

0.985 |

0.013 |

| OFF |

ON |

ON |

8.694 |

0.980 |

0.013 |

| ON |

OFF |

OFF |

17.092 |

0.985 |

0.013 |

| ON |

OFF |

ON |

16.815 |

0.980 |

0.013 |

| ON |

ON |

OFF |

8.767 |

0.985 |

0.013 |

| ON |

ON |

ON |

8.694 |

0.980 |

0.013 |

Table 3.

The values of the output parameters.

Table 3.

The values of the output parameters.

| SWRSb1

|

RIb1 [KΩ] |

AUb1

|

ROb1 [KΩ] |

| OFF |

0.013 |

104.762 |

2.200 |

| ON |

0.013 |

180.328 |

2.200 |