1. Introduction

In ultra-reliable and low latency communications (URLLC), the high reliability of short block codes becomes the key requirement [

1]. To do this, cyclic redundancy check (CRC-polar codes are particularly effective [

2]. For decoding short CRC-polar codes, the state-of-the-art method is CRC-Aided (CA) - successive cancellation list (SCL) decoding [

3].

Two cutting-edge short code decoding algorithms are ordered statistics decoding (OSD) [

4] and guessing random additive noise decoding (GRAND) [

5]. OSD is a decoder near the maximum likelihood (ML) and ideal for parallel design. However, the decoding complexity of

s-order OSD can be too high to address.

Therefore, many pieces of early research have been done to reduce the complexity of OSD [

6,

7,

8,

9]. Recently, a threshold-based OSD decoder can reduce the number of tested codewords [

10]. CA-OSD [

10] and segmentation-discarding decoding [

11] limit the number of valid codewords to improve performance. Probability-based OSD [

12] calculates the promising probability and success probability to discard the candidate codewords.

Moreover, on the other hand, GRAND provides a new perspective for ML decoding by estimating the noise sequence [

5]. Ordered reliability bits GRAND (ORBGRAND) [

13] is proposed to improve decoding throughput by generating possible error patterns (EPs). Its high-throughput and energy-efficient very large-scale integration (VLSI) circuit architecture is given in [

14].

In this paper, we propose a new scheme called pre-configured error pattern (PEP) OSD that considers OSD from a new perspective. The main innovations and the advantages of this scheme are summarized as follows:

(1) Decoding process: Instead of concentrating on completing queries of the most reliable independent symbols [

4] on Hamming balls as

s-order OSD, we use plenty of pre-configured EPs like ORBGRAND onto the transformed information bits. Before decoding, massive EPs can be pre-configured, so the EPs can be continuously read and tested on the hard-decision bits to see if these EPs can fix the errors in the information bits of the permuted systematic polar codes. After a Euclidean distance competition of

codewords that can pass the CRC check, the most possible result can be obtained. Due to the characteristics of CRC-polar codes, introducing the maximum number of valid codewords

can early stop the decoding to achieve lower complexity.

(2) EP pre-configuring process: The EPs can be either pre-configured once for all kinds of codes (with different lengths or rates) to achieve higher decoding speed or dynamically generated before decoding to save the hardware resource. As optimizing the test order of the pre-configured EPs can further leverage the soft information, queries can be obviously saved. Two orders are introduced: index weight (IW) & Hamming weight (HW) order and priority weight (PW) order. IW&HW relates to the error possibility of a specific EP, and IW similar to the logical weight in ORBGRAND [

13], though only for the transformed information bits in this scheme. Thus the possible calculating complexity is reduced. Moreover, PW, in a quantitative relationship related to IW and HW, is designed to direct an efficient way to use the possible EPs.

The remainder of this work is structured as follows: Preliminaries are provided in

Section 2. The design of a PEPOSD decoder is given in

Section 3. The generating theory and mechanism of PEP and testing order are given in

Section 4. The simulations are evaluated in

Section 5. Finally, conclusions are drawn in

Section 6.

2. Preliminaries

2.1. CRC-Polar Codes

A CRC-polar code is characterized by its code length

n,

k-length information bits, and

m-length CRC, thus denoted by

. For CRC-polar codes, the information bits are assigned to the channels with indices in the information set

, related to the more reliable subchannels, and

. The frozen bits, which have the default values, all zeros, are assigned to the complementary set

. The channel input depends on the encoding function

where

and

are the source and code block, respectively. The source block

consists of information bits

and frozen bits

, and then modulated into BPSK vector

. Suppose that

is transmitted over a noisy channel, and the received vector

is represented as

where

is the additive Gaussian noise. Therefore, there is

where

denotes the hard decision sequence of the received vector, and

denotes the EP where the “1” bits result in the flips of bits between the sequence sent and the hard decision of the received.

Note that the i-th element of a vector is expressed by , for example, the i-th bit of the code is denoted by .

2.2. OSD Algorithm

In OSD, two permutations

,

are performed over

and

before decoding. After these, the received signals

and the hard decision

are all respectively reordered. For example,

is reordered by

Meanwhile, the permutations and Gaussian elimination transform the generator matrix

into its systematic form

[

3]. Therefore, only the

most reliable positions of

are considered.

Then a number of tested codewords are compared to find the most likely estimate. In traditional OSD, codeword estimates are tested in the increasing order of the EP’s Hamming weights. For instance, in s-order OSD, codeword estimates with Hamming weight from 1 to s of the corresponding EP are compared. After performing inverse permutations, the best result of the codeword estimates is chosen as the output.

3. PEPOSD Decoder

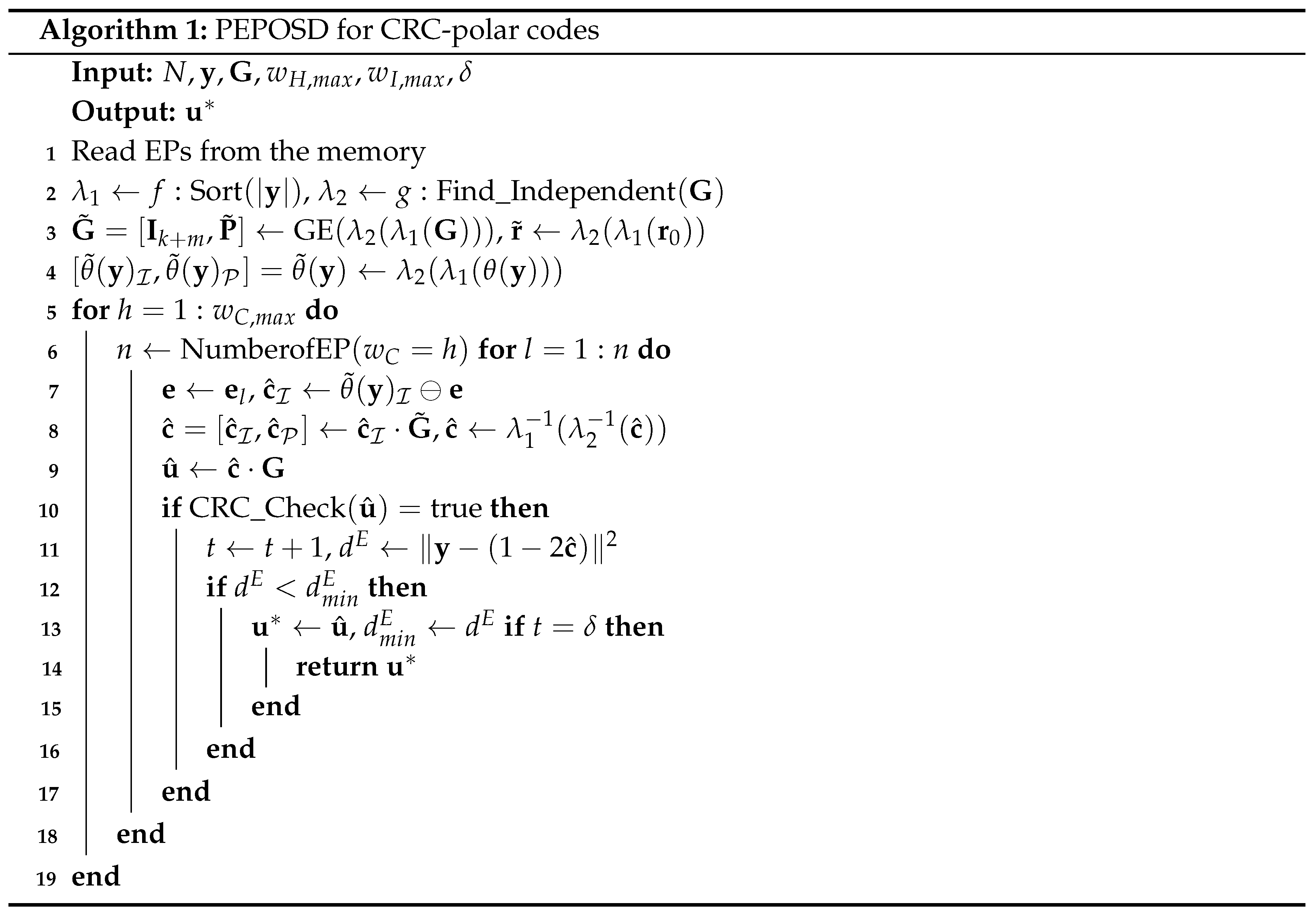

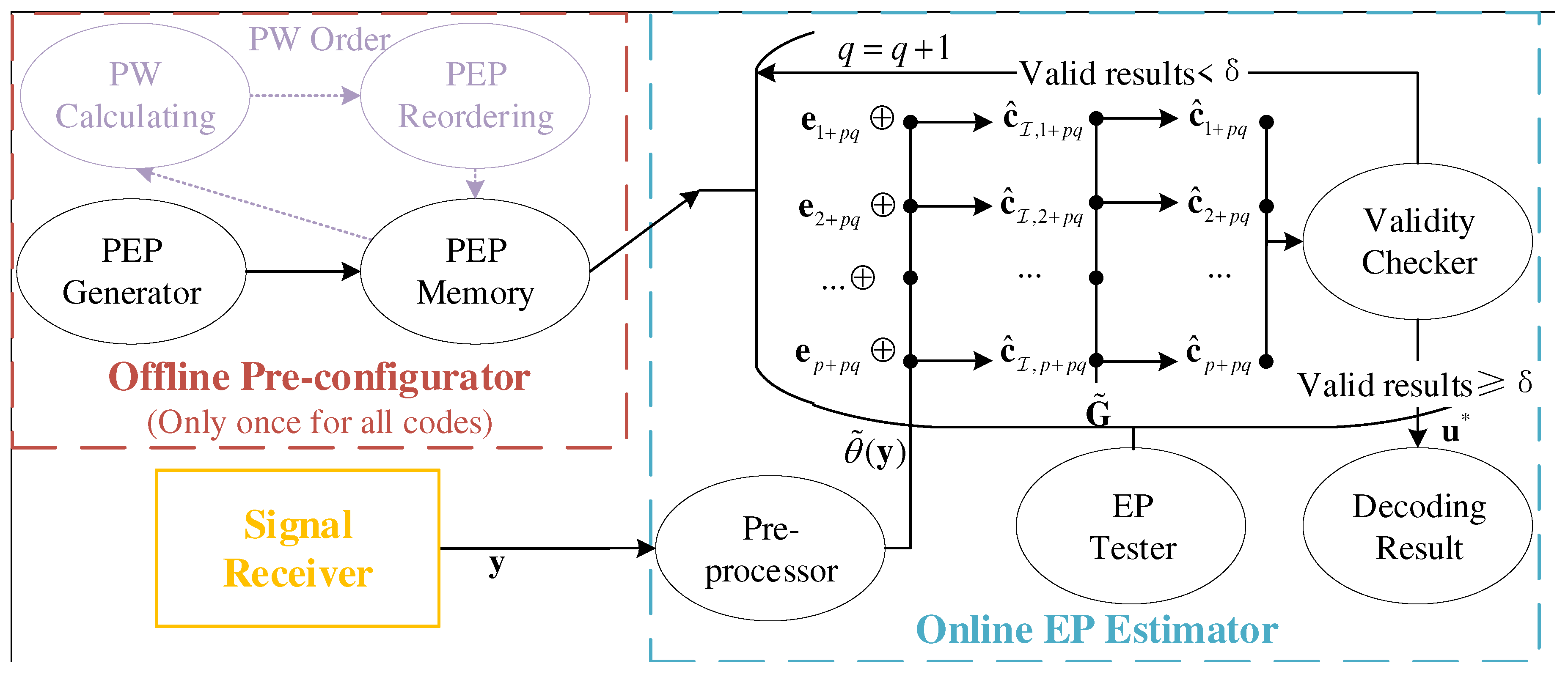

In this section, we introduce the details of PEPOSD. The whole decoder that can generate and test the EPs in parallel and relative processes is shown in

Figure 1. There are two key units in PEPOSD: the offline pre-configurator and the online EP estimator. The pre-configurator can generate and reorder all the EPs and only once for all codes. The related details are described in

Section 6. Meanwhile, the EP estimator consists of 3 modules: pre-processor, EP tester, and validity checker.

We also summarize the decoding process in Algorithm 1. Here we introduce the decoding process in detail.

Before decoding, the signals should be preprocessed by permutations and . Thereby, the hard decision of the signal with systematic bits can be obtained. The EP tester then tests one or several EPs in parallel on the processed sequences and attains the possible result. The validity checker would decide if the result can pass the CRC check. The valid results will be stored in the list until the number reaches its limit . Otherwise, backtrack and another EP will be adopted and tested. Finally, the Euclidean distances of the results will be compared, and the most possible result will be selected as the decoding output.

The pre-processor performs two permutations and the systematic transform. The first permutation sorts by its absolute value , and the second permutation finds linearly independent column vectors in as the first columns. Then it performs Gaussian elimination (GE) to the permuted generator matrix , so the systematic form of generator matrix is obtained. Thus the generator matrix becomes , where is a -dimensional identity matrix and is the parity sub-matrix.

Meanwhile, perform and on the hard decision and initial index , where is set by . Then the reliability index is obtained by , which corresponds to the ascending-order index of reliability in the most reliable bits. The reordered-form , can be obtained. Note that consists of the first bits and the rest , respectively corresponding to and in , i.e., , where and denote the index set of the information and parity bits respectively.

For each EP, the estimate of

, is denoted by a codeword

. The systematic bits

are generated by eliminating the error of hard decision

,

where

denotes the

l-th EP. Then the whole codeword estimate

can be calculated by

Therefore, a possible candidate source block can be attained. After this, the validity checker will test if can pass the CRC check. If the CRC check is passed, is determined as a valid result and sent to the candidate list. Calculate the Euclidean distance and compare it with the current minimum candidate . If the number of candidates reaches , the decoding will be completed and the most likely candidate will be output. This leverages the characteristic of CRC-polar codes to control the complexity.

If the candidate is invalid or the number is not enough, come back to the EP tester and read another EP. Though the generator matrix of CRC can be calculated into the whole generator matrix, a separate check is beneficial to control the number of queries.

4. Pre-Configured Error Patterns

In this section, we first discuss in IW&HW order, the theoretical basis of the PEP generating mechanism. Then two integer splitting algorithms are introduced. Finally, PW order is introduced to better control the testing order of the EPs.

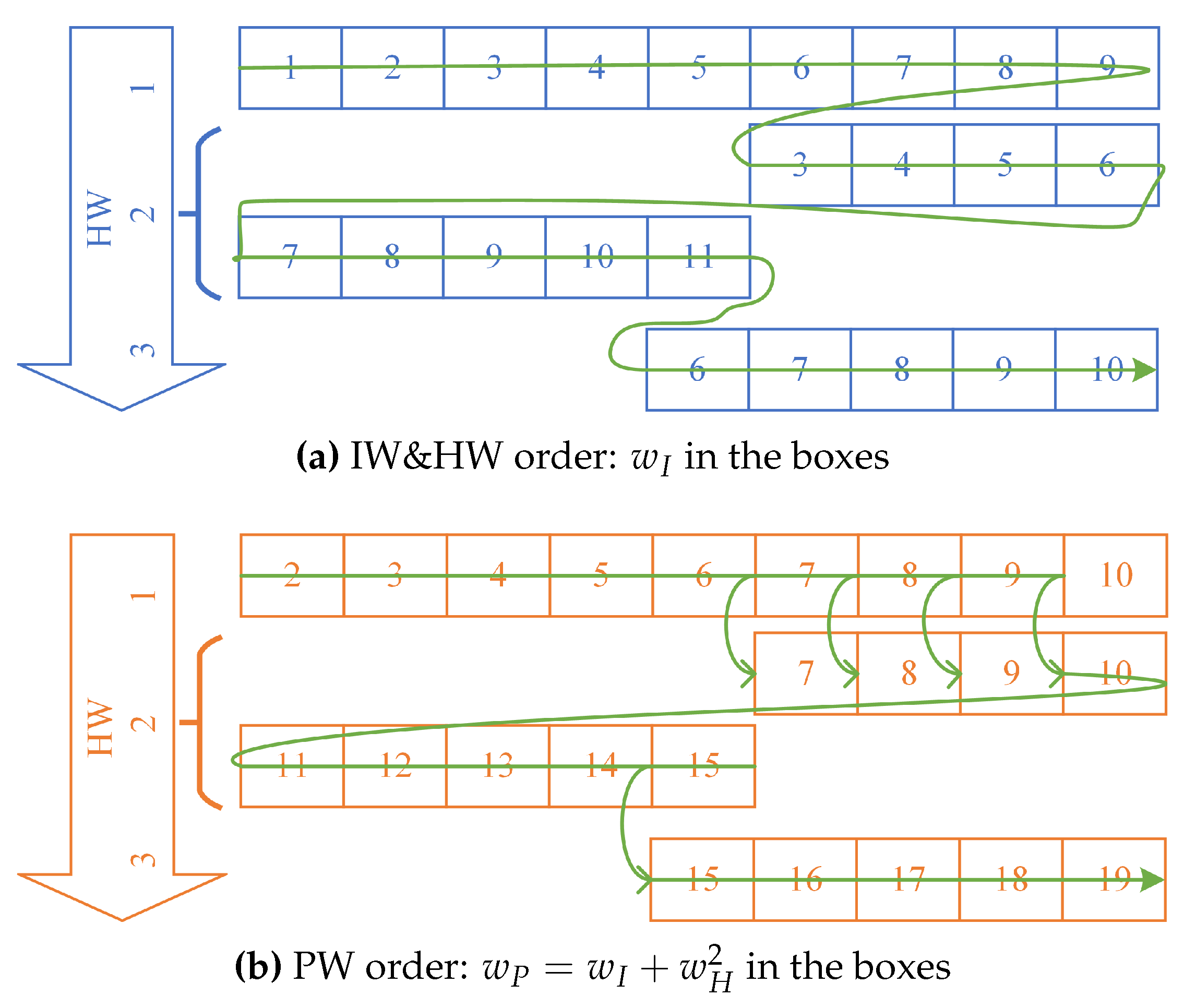

4.1. IW&HW Order

As the reliability index

is obtained by

, this indicates the necessary order to eliminate the errors on these bits. Upon this, referring to ORBGRAND [

13], we can define reliability weight (RW), IW, and HW. The reliability weight is the sum of the approximate reliability of

, which can be calculated by

RW collects the reliability prior information of all permuted systematic bits. However, as RW is difficult to split and control, IW is introduced. For an error pattern

, the corresponding IW is defined as

which means the accumulation of the reliability index of all the error bits

given the specific EP

. The smaller IW generally corresponds to the bigger RW, and also the more possible noise effect of the specific EP. IW gives a quantitative integer indicator to evaluate the order to test EPs. The difference between IW and logical weight [

13] is that IW only consists of the information of the systematic bits, which is determined endogenously by the OSD algorithm, and accordingly leads to different impacts. Furthermore,

indicates the maximum IW in all the EPs.

Similarly, the HW of a given error pattern is defined as

presents the maximum HW of all the EPs. The smaller HW often leads to some more usual errors. Without ambiguity, for all eligible

,

are abbreviated as

.

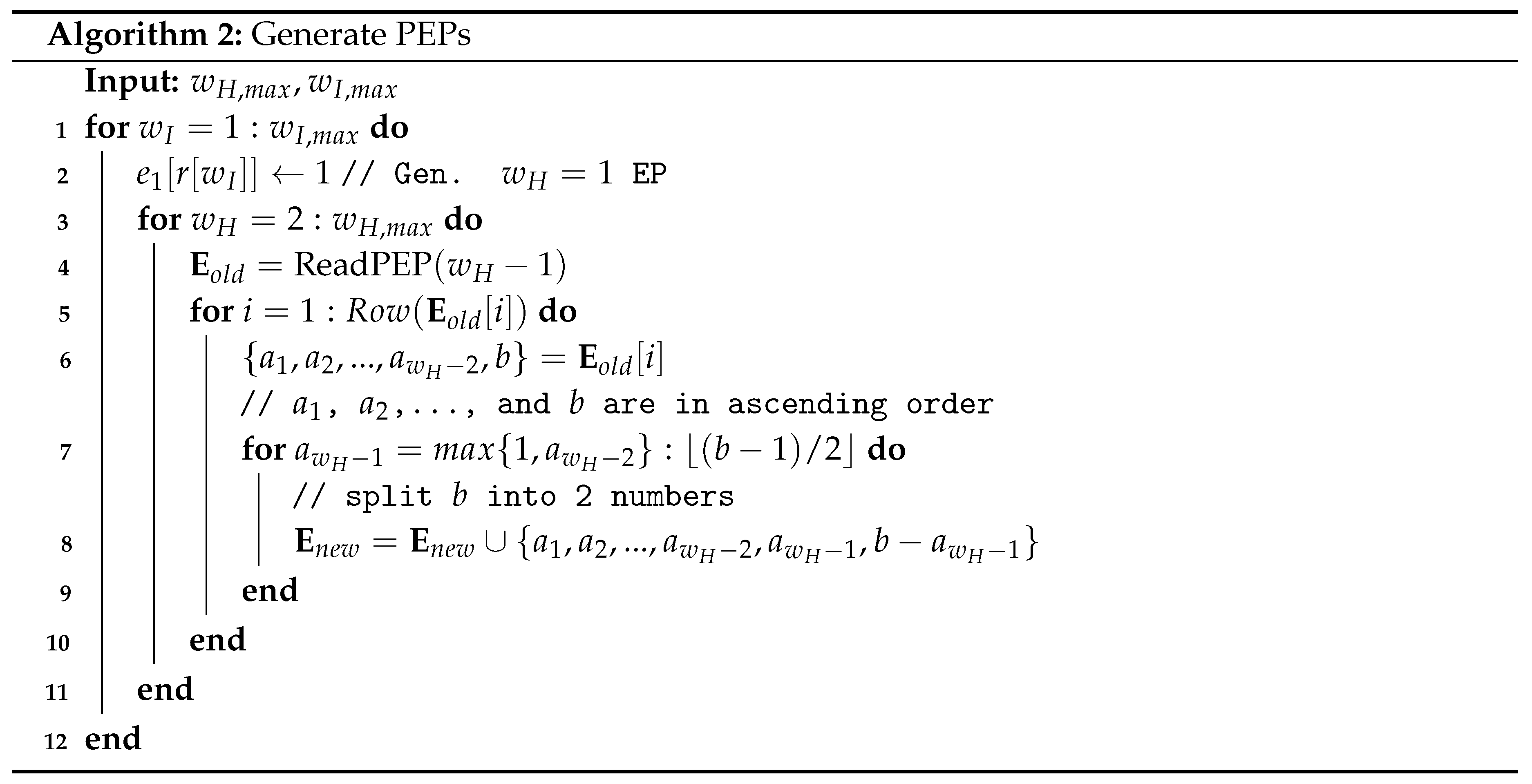

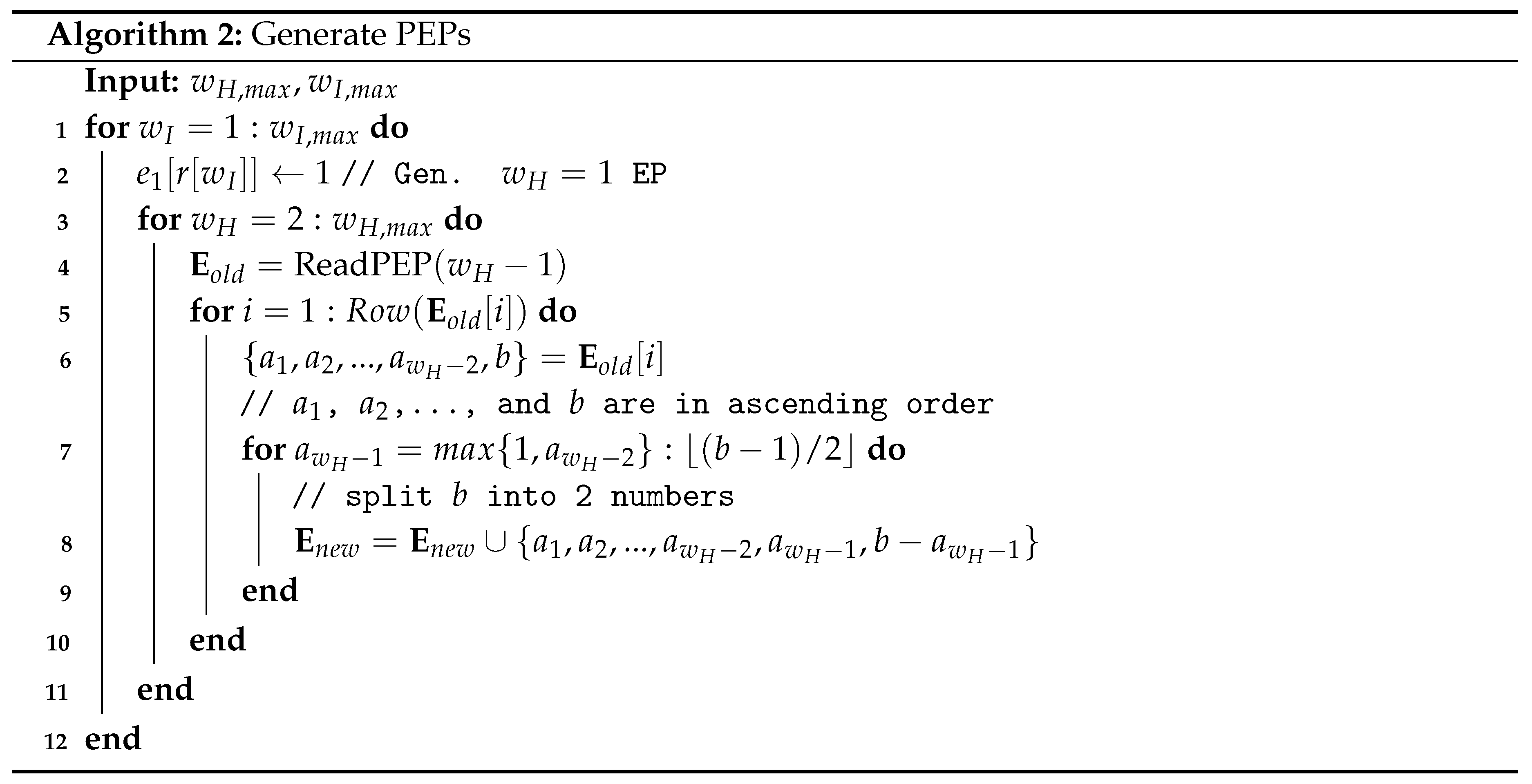

To pre-configure the EPs with all IW and HW we set, the process of PEP generation is designed as follows. We first generate EPs whose

1. While generating “new” EPs whose

is from 2 to

, the generator first reads the “old” EPs whose

, storing into

. By splitting only the biggest integer in old EPs and putting the small integers aside, corresponding new EPs can be generated. The algorithm is summarized in Algorithm 2. While splitting the integer,

b stands for the biggest number and

,

,…, and

b are in ascending order. Thus, all EPs needed can be pre-configured. An integer-splitting algorithm for ORBGRAND [

13] can also be referred to.

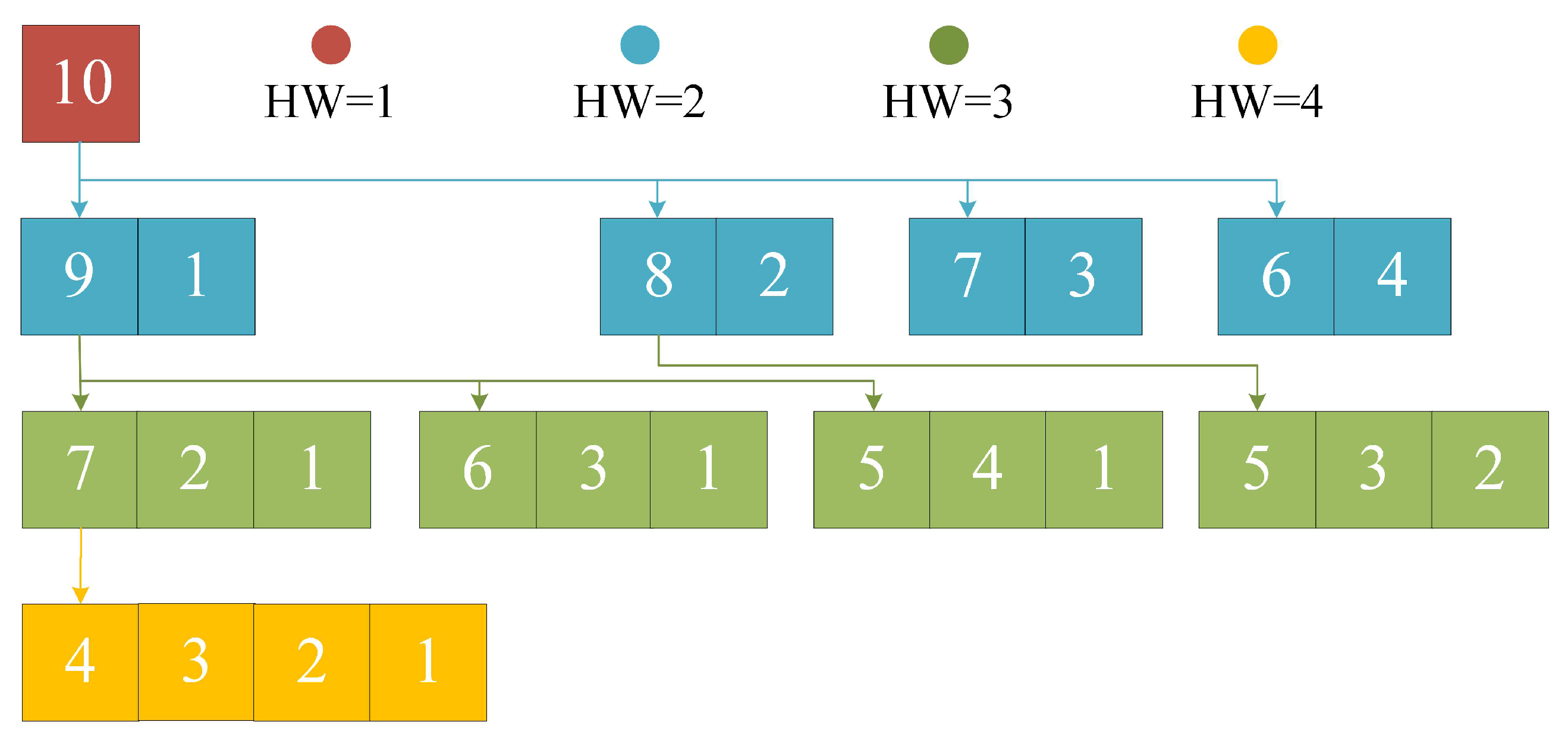

There is an example for

and

shown in

Figure 2. First the EP with

is generated. Then 10 is divided into {9,1},⋯, {6,4}, and 4 EPs with

are obtained. After that, 9 in {9,1} can be divided into {7,2}, {6,3} and {5,4}, while 8 in {8,2} can be divided into {5,3}, thus 4 EPs with

are obtained. Finally, one EP with

is generated by dividing 7 in {7,2,1} into {4,3}.

PEP pre-configurator can produce all EPs stored in the memory before decoding numerous codes, so the decoder can continuously read EPs to significantly reduce the decoding delay, and only once is enough for all kinds of codes and all code blocks. On the other hand, while decoding a small number of codes, each EP can also be dynamically generated just before being tested to ensure better energy efficiency.

4.2. PW Order

As IW and HW are introduced and all the EPs have been pre-configured, PW can be defined by

where

and

are parameters to be set. The order of using the EPs depends on their PW, which indicates a special order to prevent the decoder from trying some EPs with a super low possibility even if its HW is small.

Figure 3 gives a hypothetical example to see the difference of the PEPOSD scheme between IW&HW order and PW order.

Figure 3(a) shows the IW&HW-order PEPOSD. The decoder first tests the

EPs in the order of

. After that, it tests those with

, then 3, and so on. Meanwhile, in our new proposed scheme, the decoder just tests the EPs in the order of PW.

Figure 3(b) shows how the PWs of the EPs correspond to their HW and PW. Therefore for instance, the EPs are tested from

, to

. Obviously, the two EPs with

are tested together, also for

. In this way, the order of using EPs can be optimized and some less probable EPs will be tested far later.

5. Performance Evaluation

In this section, for CRC-polar codes, we respectively compare the performance of PEPOSD with 3-order CA-OSD and CA-SCL ().

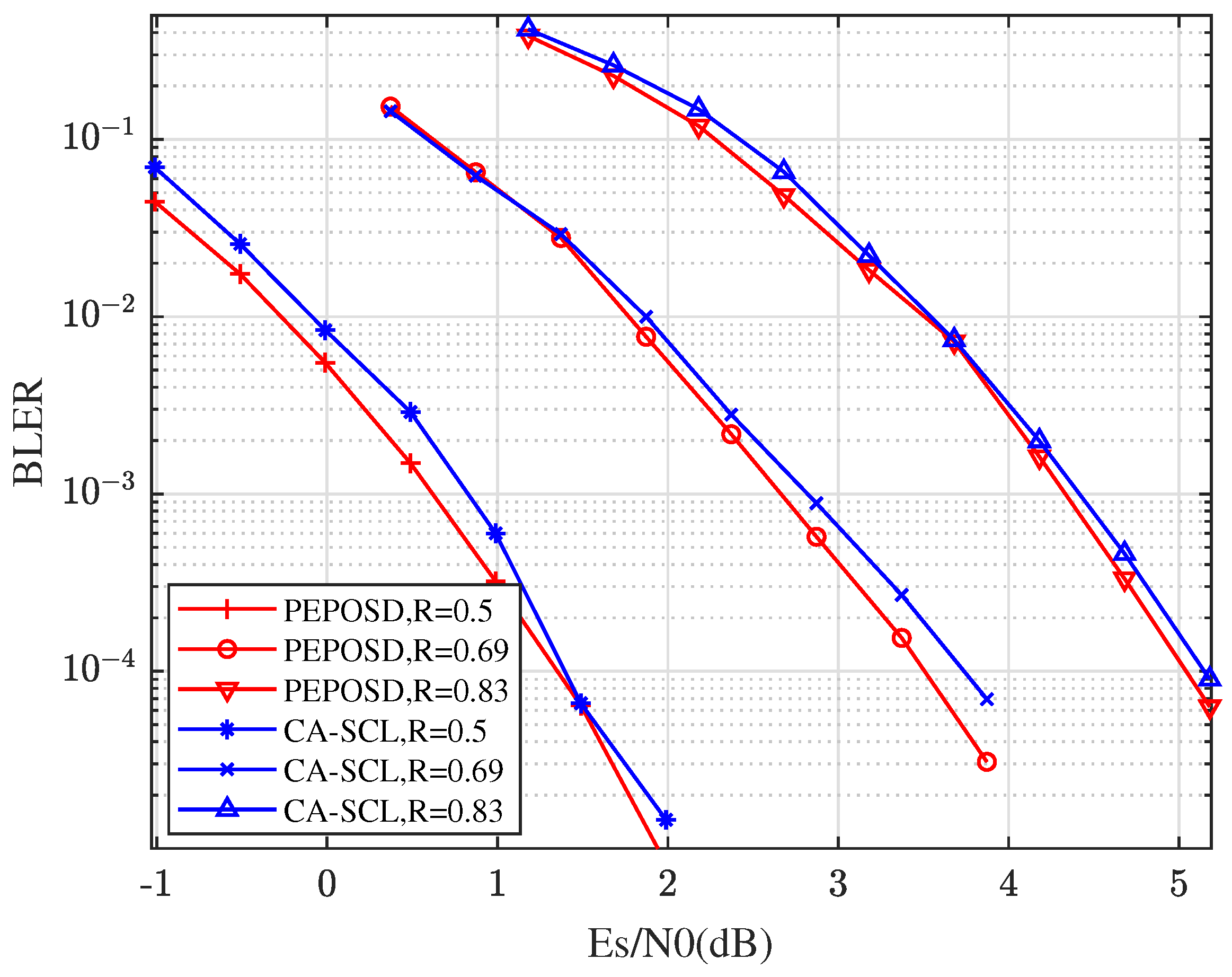

5.1. BLER Analysis

First we compare the BLER performance with low complexity of these algorithms.

Figure 4 shows the BLER comparison between PEPOSD (IW&HW) and CA-SCL with different rates with the code length

and CRC length

. In this figure, there is (IW/HW/

for PEPOSD. This demonstrates that PEPOSD outperforms CA-SCL by about 0.3 dB with the close complexity for the high rates. Increasing the CRC length can improve the performance of PEPOSD while this worsens CA-SCL, so the advantage can be more obvious.

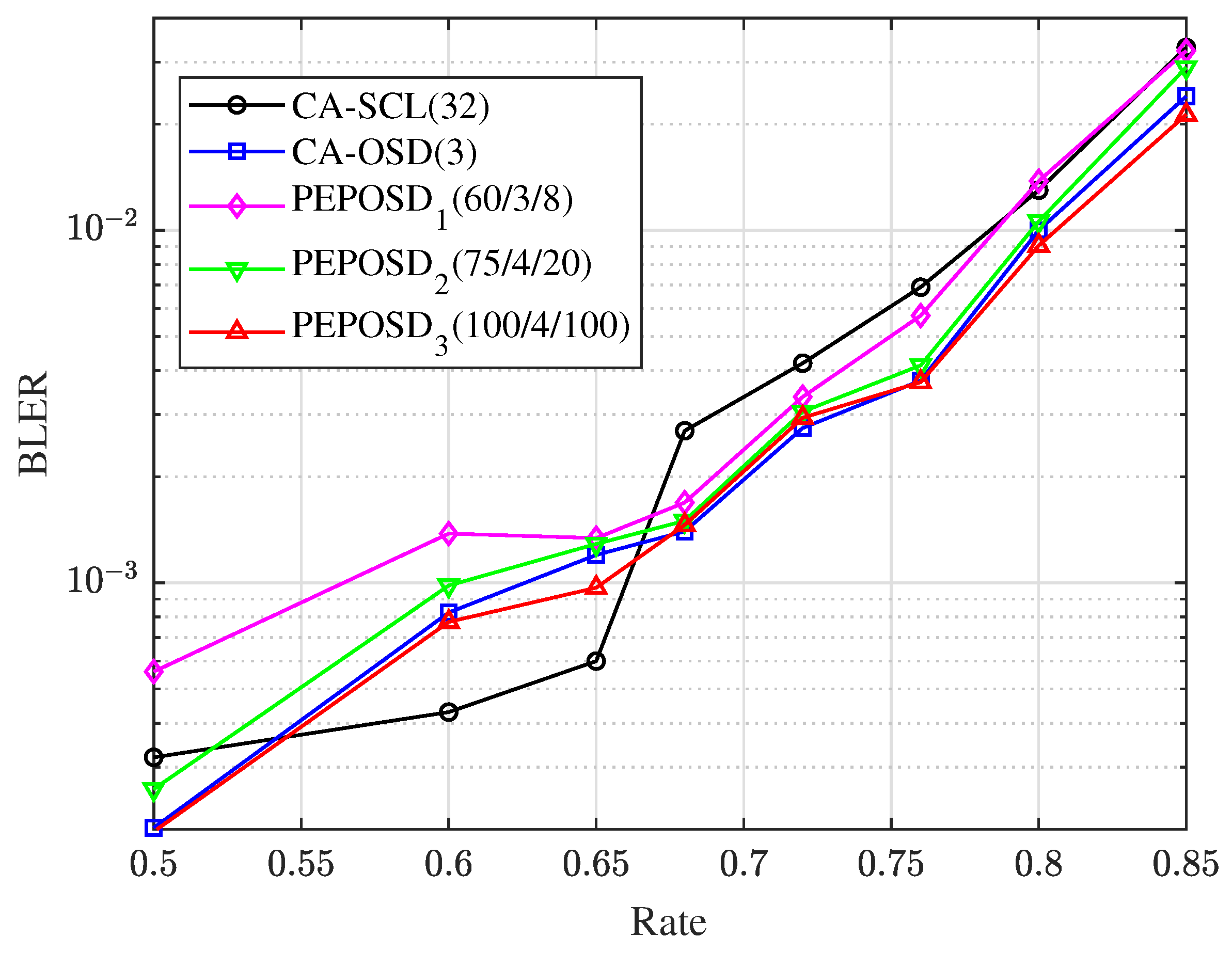

Figure 5 shows when

, the BLER comparison with different code rates from 0.5 to 0.85 among PEPOSD, CA-OSD, and CA-SCL. This shows that PEPOSD

can achieve close accuracy with CA-OSD. Moreover, when

and

or higher, PEPOSD outperforms CA-SCL obviously. More detailed analysis about PEPOSD related to its complexity is given in

Section 5.2.

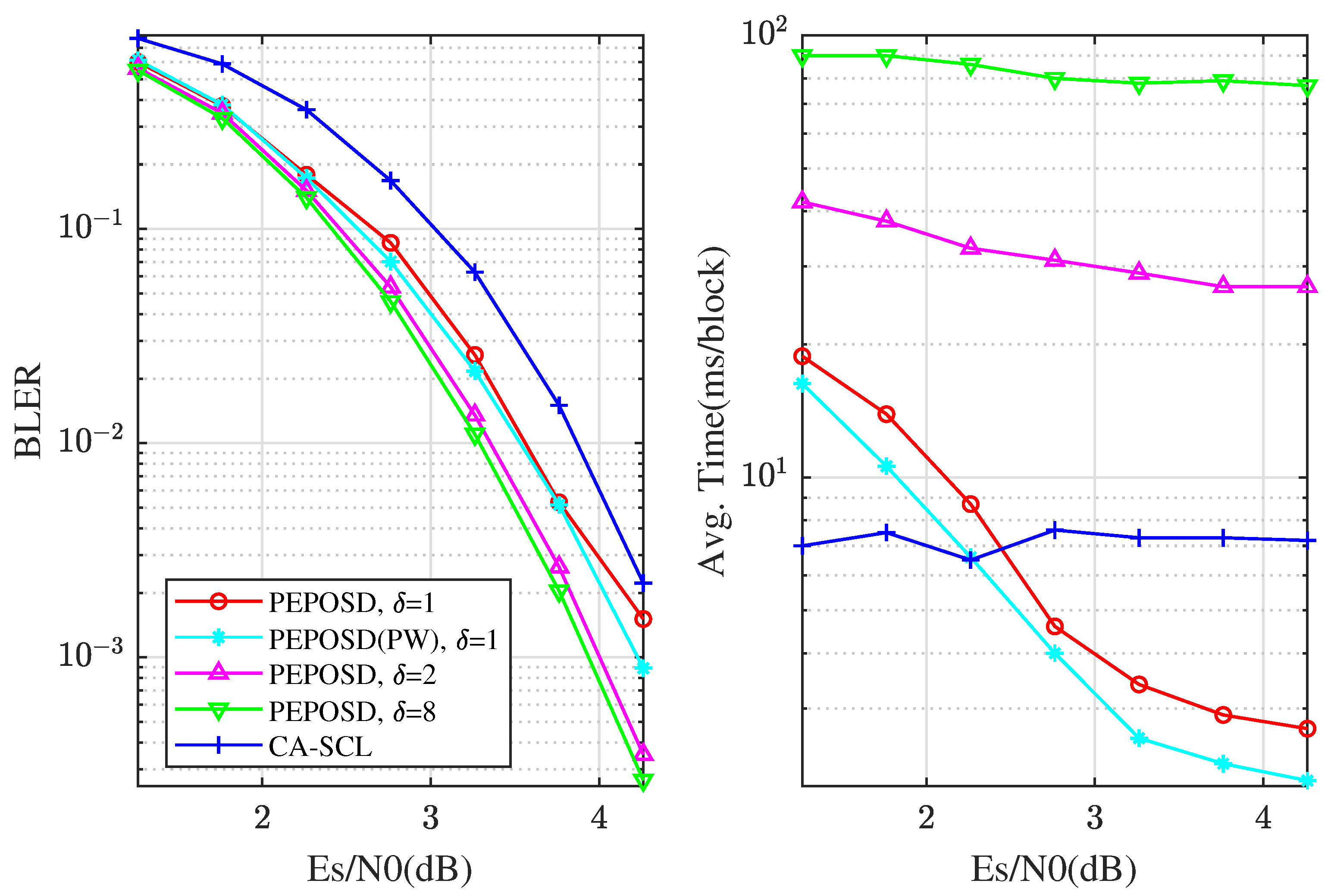

Then we analyze the ultimate performance with higher complexity.

Figure 6 shows the performance comparison for [128,108+11] CRC-polar code. PEPOSD(IW&HW) is here with (IW/HW

and different

. Meanwhile, PEPOSD(PW) with (IW/HW

and CA-SCL(

) are shown. The average decoding time is got from the same CPU. It can be concluded that PEPOSD can achieve better performance at a high rate for 128-bit CRC-polar codes and the decoding complexity can also be smaller than CA-SCL in high SNR areas. Also PW order performs better for this code.

Therefore, the simulation results show that PEPOSD achieves a better trade-off between accuracy and complexity than CA-OSD, and also can perform better for some short codes than CA-SCL. What’s more, the parameters can be configured flexibly and the decoding process can be parallelized to further increase its throughput.

5.2. Complexity Analysis

First, we compare the computational complexity of the proposed scheme with CA-SCL. Specifically, it should be noted that all operations are modulo-two operations (XOR) in this scheme, so the hardware resources and time spent will be obviously less with the same quantity in the engineering practice and hardware implementations. As most of the OSD research does, we focus on the queries needed in the decoding process, also the number of the EPs tested. Therefore, the number of bit flipping in this period can be calculated by

, where

Q denotes the queries. Another key complexity that we consider compared with SCL, GRAND or other algorithms is GE in the pre-processor, of which the complexity can be calculated by

. Moreover, there are some parallel or other efficient implementations can optimize the process like in [

16].

Also, multiplication and addition operations needed in CA-SCL can be expressed as

. Thus,

Table 1 displays the complexity estimation of PEPOSD, CA-OSD, and CA-SCL. The queries of PEPOSD mainly based on

, if IW and HW are relatively high enough. In conclusion, PEPOSD can obviously achieve lower complexity for high-rate codes, and for lower rates, PEPOSD may outperform CA-SCL as it’s with modulo-two operations, which needs more hardware analysis to prove.

Observing together with

Figure 5, it’s obvious that PEPOSD

can achieve close accuracy with CA-OSD while its average number of bit flipping is

to

of 3-order CA-OSD. Also, PEPOSD

can obtain better accuracy than CA-OSD and the queries can be greatly reduced at the same time. For high-rate codes, PEPOSD can outperforms CA-SCL and CA-OSD both in accuracy and complexity.

Finally, as PW is introduced, the queries reduction of the schemes with IW&HW and PW order is compared in

Table 2. For [64,46+6] and [128,108+11] CRC-polar codes, using PEPOSD with (IW/HW/

, the number of queries is reduced by 10%-30%.

6. Conclusion

In this paper, we introduce the PEPOSD algorithm to enhance the performance of short CRC-polar codes. It integrates the generating mechanism of noise queries in ORBGRAND to the generation of error patterns in OSD. Therefore, all the EPs can be pre-generated to allow the pipeline decoding for better speed. Also, early stop by CRC check can significantly reduce the complexity.

To optimize the decoding order of the proposed scheme, two options are introduced. IW&HW order is suitable for the most circumstances while PW shows lower complexity with bigger IW. In this way, the range of error patterns can be more controllable than l-order CA-OSD.

Simulation results show that there are several advantages in the performance and complexity of PEPOSD compared with CA-OSD and CA-SCL for CRC-polar codes, which shows a promising prospect.

Funding

This research was funded by the National Natural Science Foundation of China under Grant 92067202, Grant 62071058.

Abbreviations

The following abbreviations are used in this manuscript:

| PEPOSD |

Pre-configured error pattern ordered statistics decoding |

| CRC |

Cyclic redundancy check |

| GRAND |

Guessing random additive noise decoding |

| ORB |

Ordered reliability bits |

| URLLC |

Ultra-reliable and low latency communications |

| CA |

CRC-Aided |

| SCL |

Successive cancellation list |

| ML |

Maximum likelihood |

| EPs |

Error patterns |

| VLSI |

Very large-scale integration |

| IW |

Index weight |

| HW |

Hamming weight |

| PW |

Priority weight |

References

- Liva, G.; Gaudio, L.; Ninacs, T.; Jerkovits, T. Code Design for Short Blocks: A Survey. arXiv 2016, arXiv:1610.00873. [Google Scholar]

- Niu, K.; Zhang, P.; Dai, J.; Si, Z.; Dong, C. A golden decade of polar codes: From basic principle to 5G applications. China Communications, 2023, 20, 94–121. [Google Scholar] [CrossRef]

- Niu, K.; Chen, K. CRC-aided decoding of polar codes. IEEE Commun. Lett., 2012, 16, 1668–1671. [Google Scholar] [CrossRef]

- Fossorier M. P., C.; Lin, S. Soft-decision decoding of linear block codes based on ordered statistics. IEEE Trans. Inf. Theory, 1995, 41, 1379–1396. [Google Scholar] [CrossRef]

- Duffy K., R.; Li, J.; Médard, M. Guessing noise, not code-words. IEEE Int. Symp. Inf. Theory 2018, 671–675. [Google Scholar]

- Valembois, A.; Fossorier, M. An improved method to compute lists of binary vectors that optimize a given weight function with application to soft-decision decoding. IEEE Commun. Lett., 2001, 5, 456–458. [Google Scholar] [CrossRef]

- Valembois, A.; Fossorier, M. Box and match techniques applied to soft-decision decoding. IEEE Trans. Inf. Theory, 2004, 50, 796–810. [Google Scholar] [CrossRef]

- Jin W.; Fossorier M. Efficient box and match algorithm for reliability-based soft decision decoding of linear block codes. In Proc. Inf. Theory Appl. Workshop, La Jolla, CA, USA, Jan. 2007.

- Wu, Y.; Hadjicostis C., N. Soft-Decision Decoding Using Ordered Recodings on the Most Reliable Basis. IEEE Trans. Inf. Theory, 2007, 53, 829–836. [Google Scholar] [CrossRef]

- Wu, D.; Li, Y.; Guo, X.; Sun, Y. Ordered Statistic Decoding for Short Polar Codes. IEEE Commun. Lett., 2016, 20, 1064–1067. [Google Scholar] [CrossRef]

- Yue C.; Shirvanimoghaddam M.; Li Y.; Vucetic B. Segmentation-discarding ordered-statistic decoding for linear block codes. In Proc. IEEE Global Commun. Conf. (GLOBECOM), Waikoloa, HI, USA, 9-13 Dec. 2019, 1-6.

- Yue, C.; Shirvanimoghaddam, M.; Park, G.; Park, O.; Vucetic, B.; Li, Y. Probability-Based Ordered-Statistics Decoding for Short Block Codes. IEEE Commun. Lett., 2021, 25, 1791–1795. [Google Scholar] [CrossRef]

- Duffy K., R.; An, W.; Médard, M. Ordered Reliability Bits Guessing Random Additive Noise Decoding. IEEE Trans. Signal Process., 2022, 70, 4528–4542. [Google Scholar] [CrossRef]

- Abbas S., M.; Tonnellier, T.; Ercan, F.; Jalaleddine, M. High-Throughput and Energy-Efficient VLSI Architecture for Ordered Reliability Bits GRAND. IEEE Trans. on VLSI Systems, 2022, 30. [Google Scholar] [CrossRef]

- Arıkan, E. Channel polarization: a method for constructing capacity achieving codes for symmetric binary-input memoryless channels. IEEE Trans. Inf. Theory, 2009, 55, 3051–3073. [Google Scholar] [CrossRef]

- Scholl S.; Stumm C.; Wehn N. Hardware implementations of Gaussian elimination over GF(2) for channel decoding algorithms. In 2013 Africon, Pointe aux Piments, Mauritius, Sept. 2013, 1-5.

|

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).