3.1. Configuration

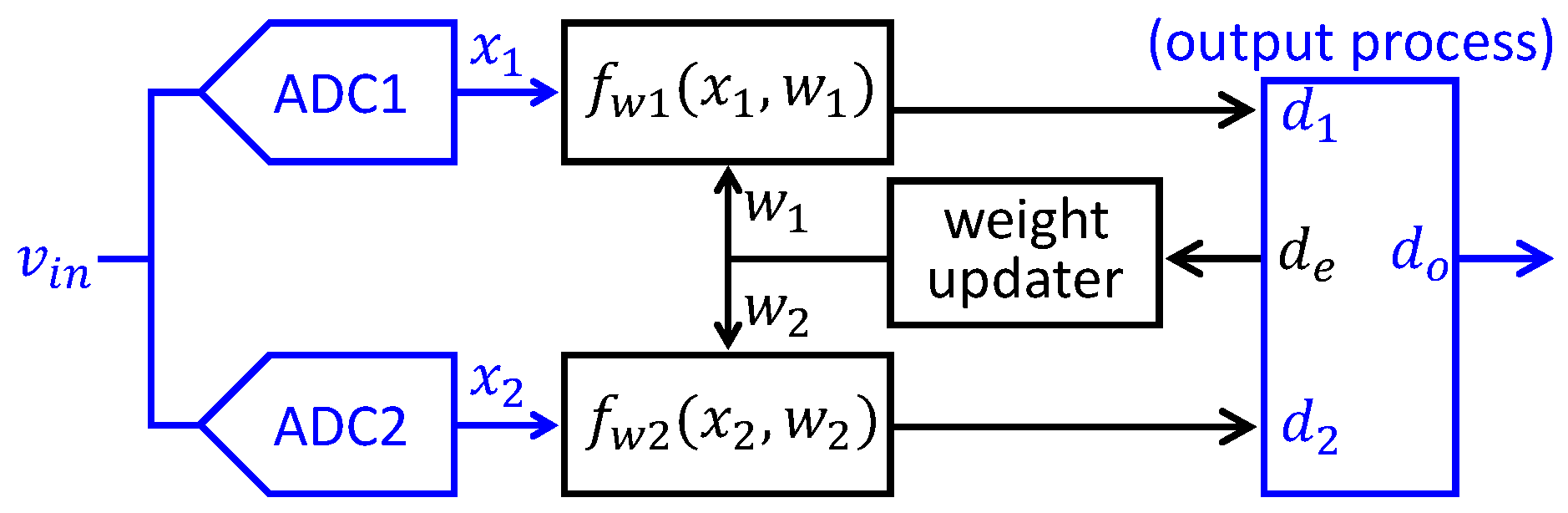

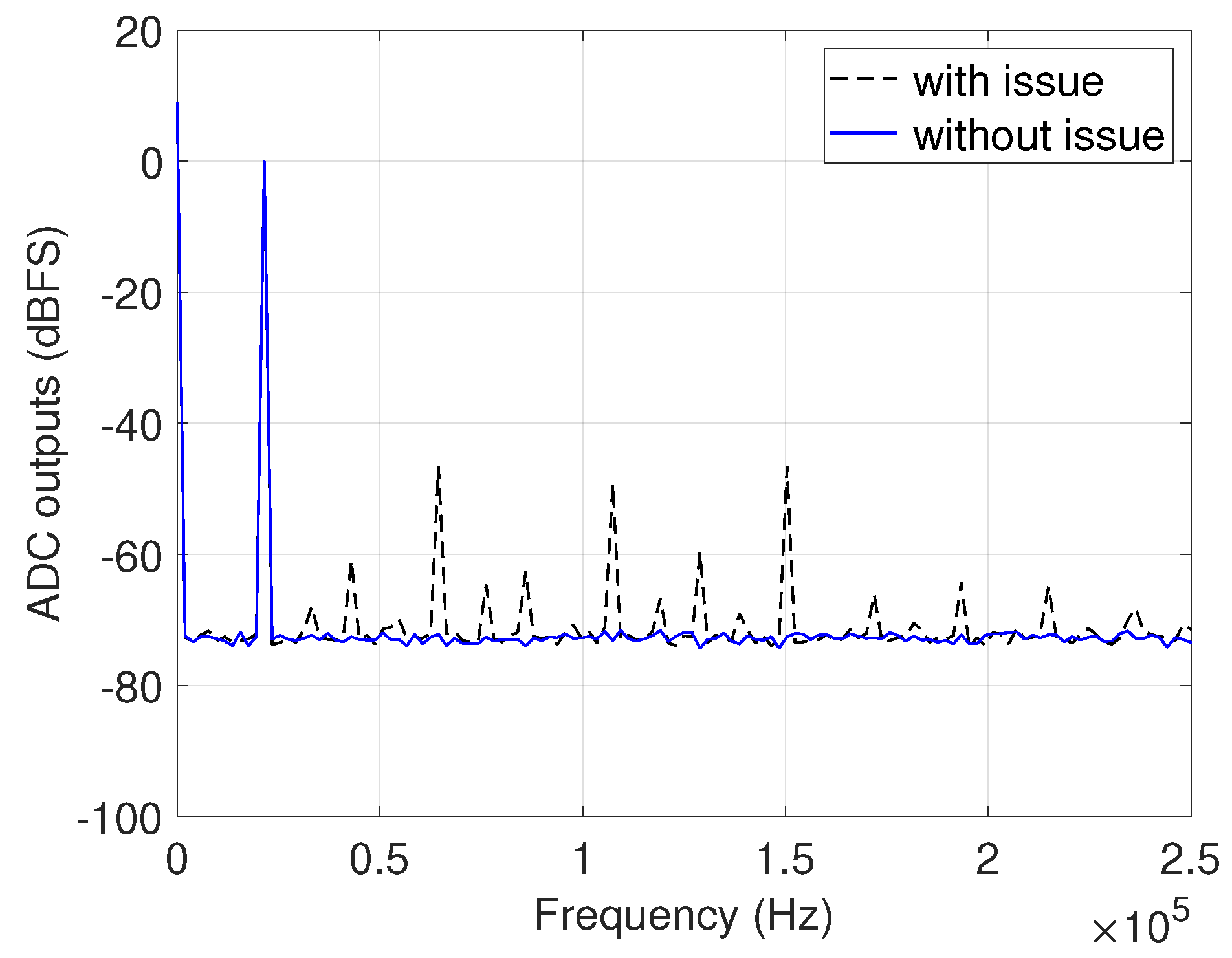

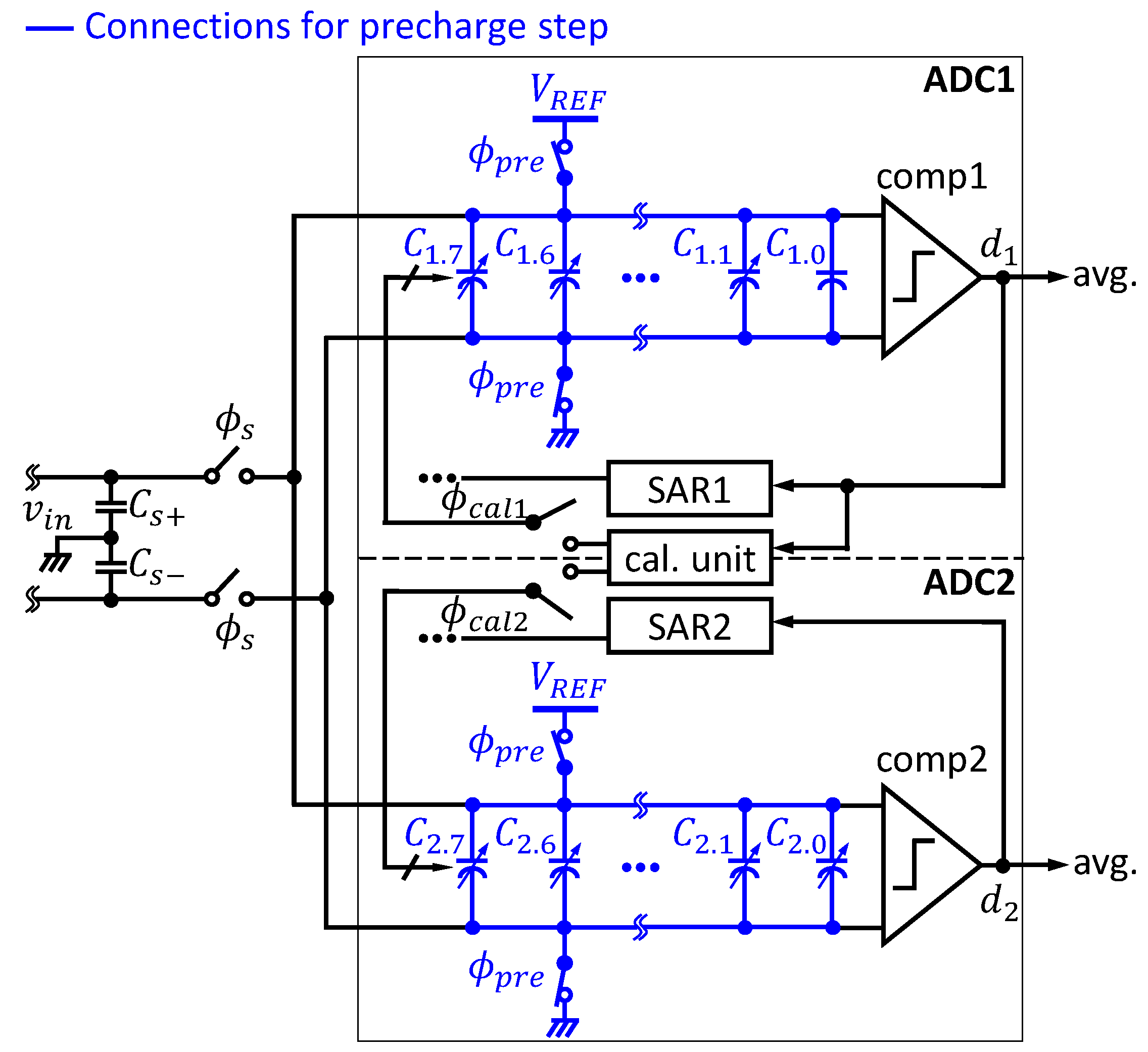

The proposed work can be simply configured by employing the split ADC platform, as shown in

Figure 3a derived from

Figure 1. The two ADC channels (i.e., ADC1 and ADC2) and the output average process highlighted in blue in a conventional split ADC shown in

Figure 1 are employed for this work, because the proposed work does not require an adaptive algorithm using

which is fundamentally required for a conventional split ADC. Thus, the proposed work differently uses the two ADC channels for our calibration purpose. Those two ADC channels provide an efficient platform to allow the proposed calibration unit (i.e.,

cal. unit) to calibrate each capacitor using a few reference capacitors, resulting in much simpler process. Cal unit consists of two processes; the linear search process for the calibration and the voltage generation (by an embedded voltage generator) to apply an input voltage

to the voltage-controlled variable capacitor, as shown in

Figure 3c. An 8-bit ADC is used as an example for better understanding, and the proposed work can be simply applied to higher resolution of the ADC.

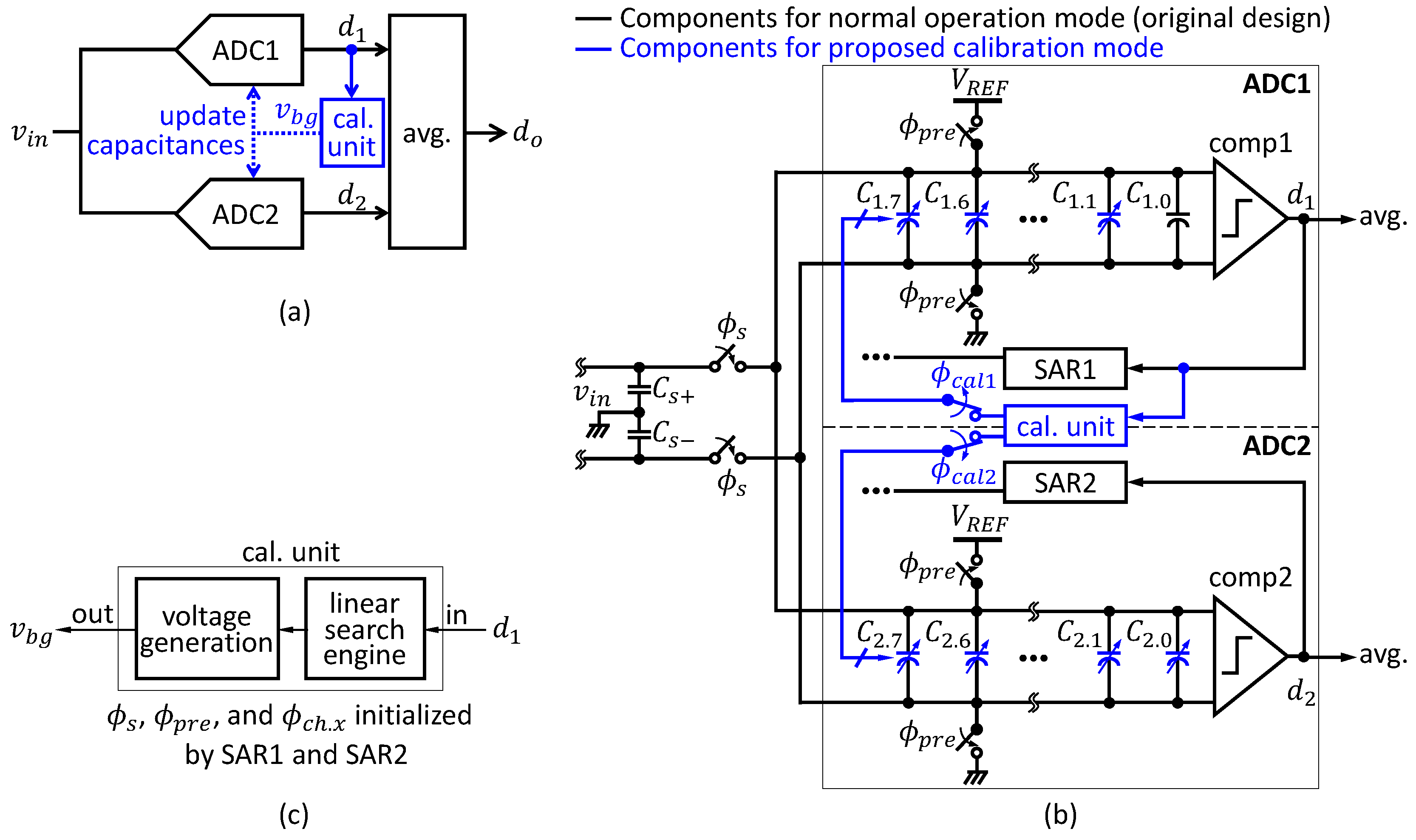

The proposed work in

Figure 3a can be realized as shown in

Figure 3b. A charge-sharing (CS)-SAR ADC [

15] with differential inputs is used for each of ADC1 and ADC2, each of which consists of a track/hold stage (omitted in

Figure 3b for simplicity), a sample stage (

and

), a CDAC (

), and a comparator (

comp1 or

comp2).

The convention

in the CDAC represents either a binary-weighted capacitor or capacitance in contexts, and its subscript

indicates each ADC channel index (i.e., 1 or 2), and another subscript

x represents each capacitor index in the CDAC (e.g.,

for an 8-bit ADC). Thus, ideally

,

, ...,

, where

is a unit capacitor. In addition,

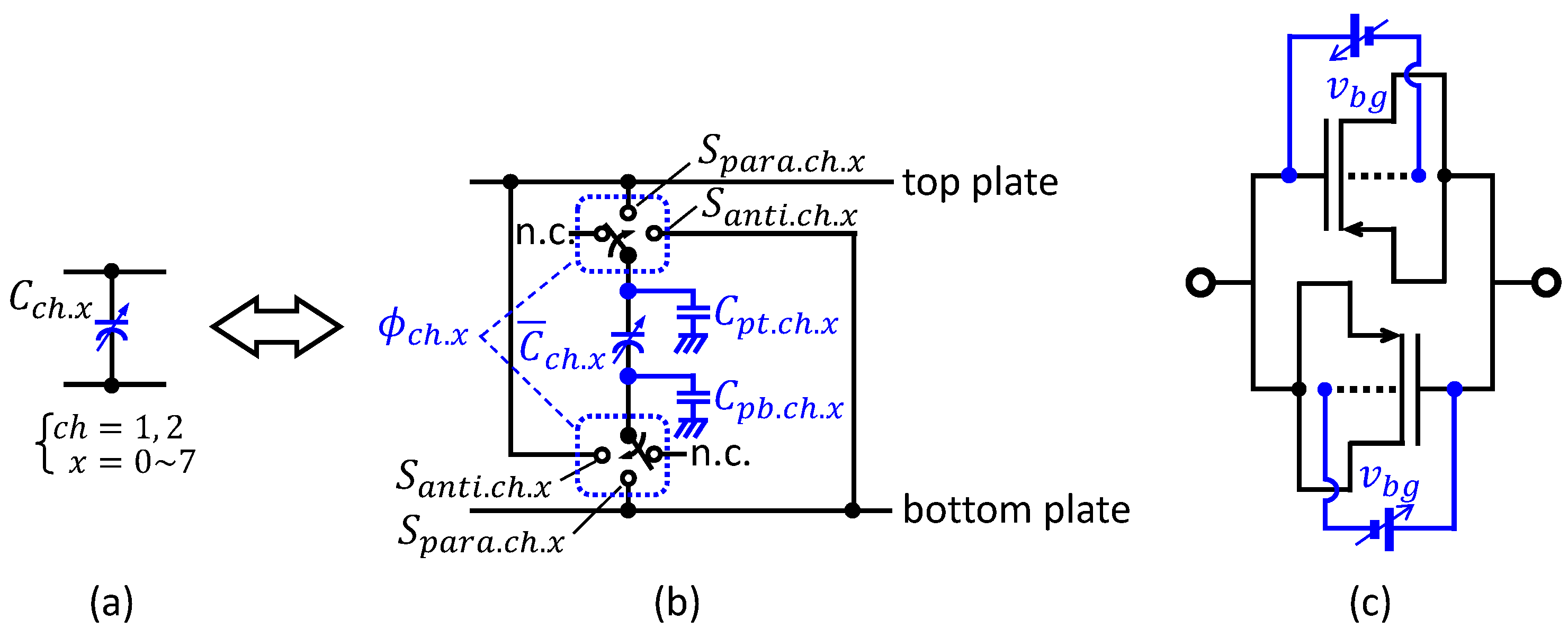

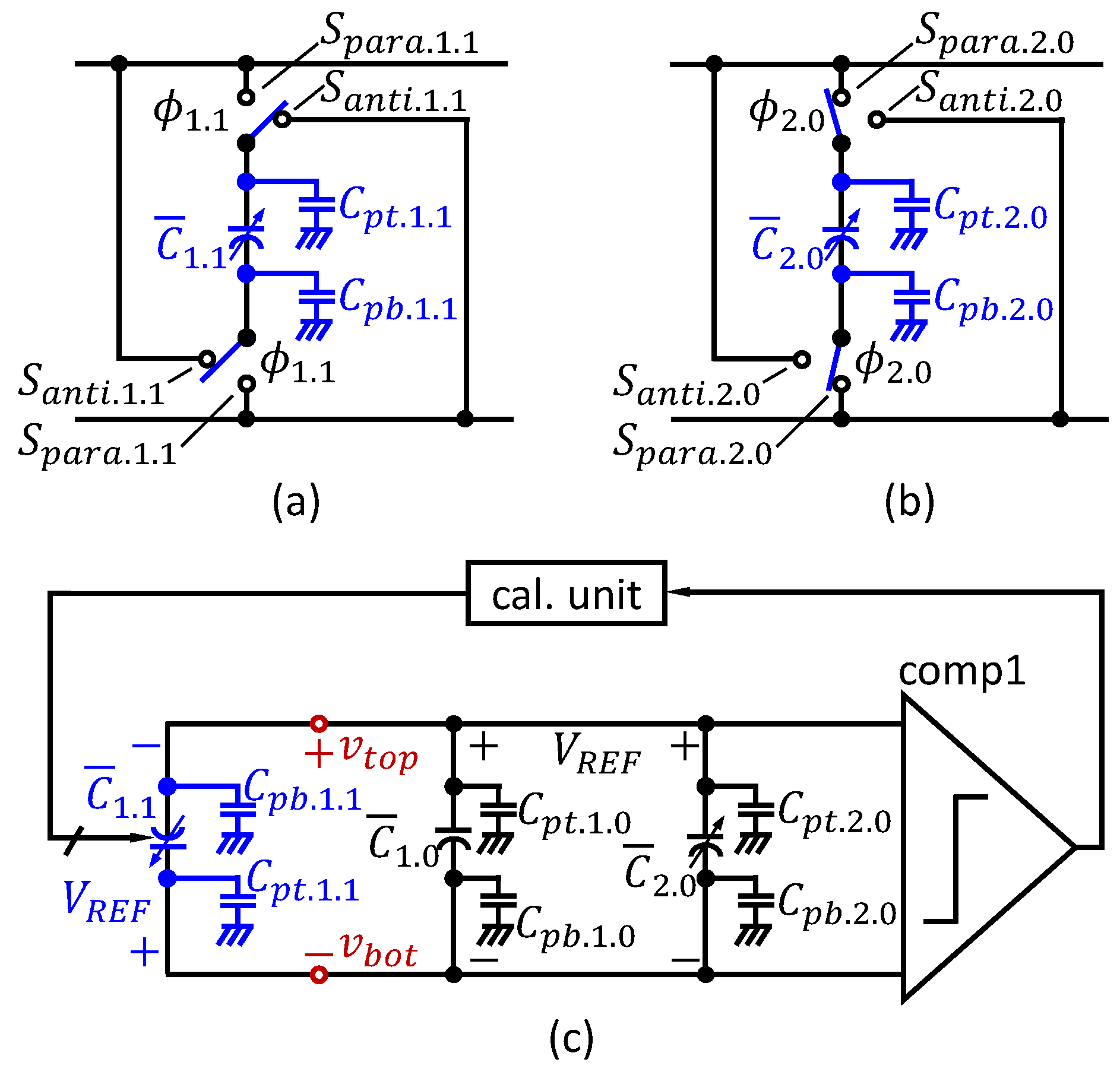

is open to make connections between the top and bottom plates of ADC1 and those of ADC2. For each binary-weighted capacitor in a conventional CS-SAR ADC, there are two internal switches,

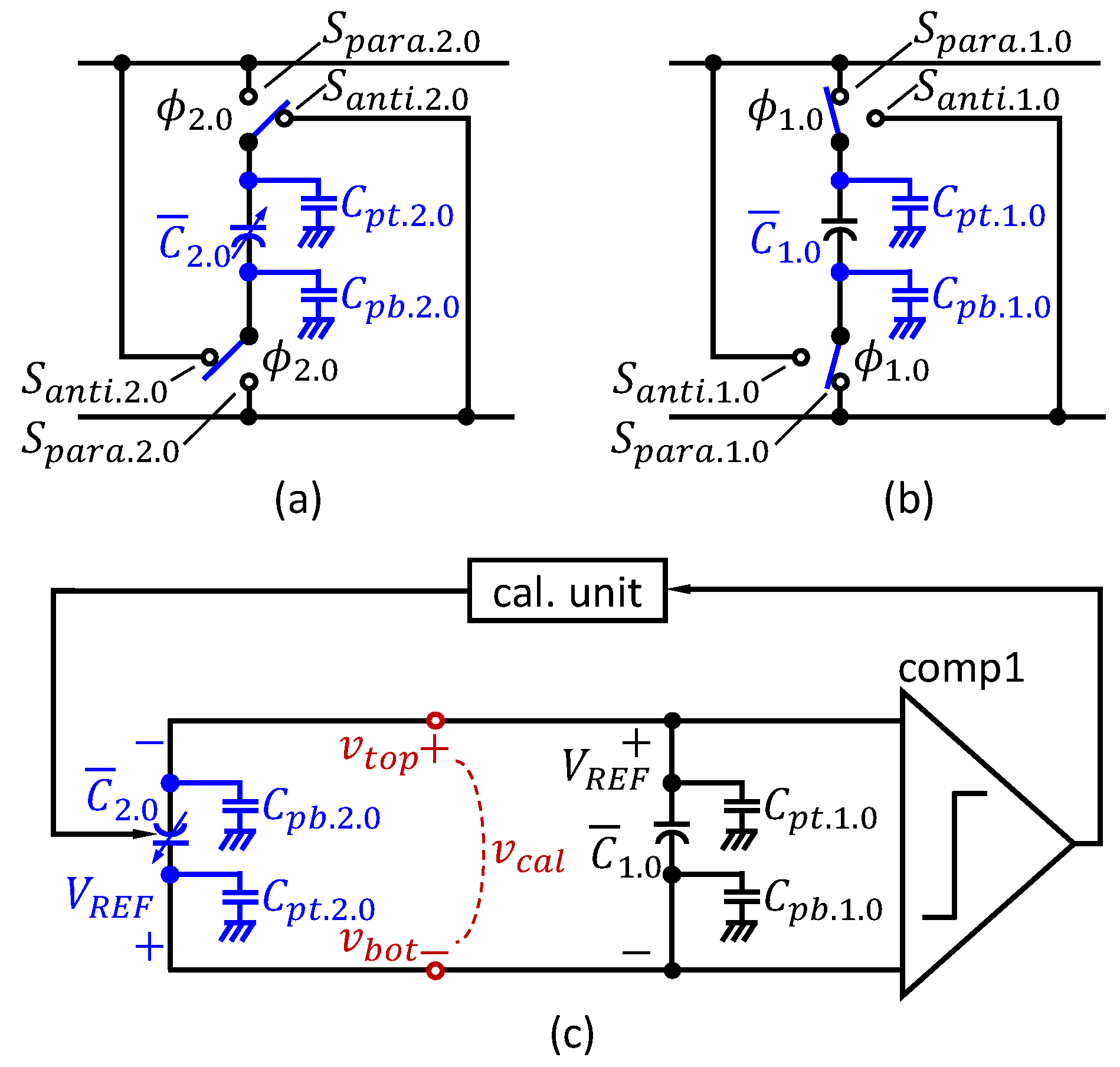

for each

as depicted in

Figure 4(a) and (b) [

15]. As shown in

Figure 4(b), those two switches allow us to make connection between each

and their top or bottom plate, resulting in parallel (

) or antiparallel (

) connection of

. We call those two switches,

para-switches for convenience. In addition, a practical capacitance

can be modeled as a capacitance combined with an ideal capacitance

, and

and

which are the parasitic capacitances occurred on the top and bottom plates, respectively [

16].

Different types of the capacitor to be used for a CDAC can be considered. While metal-oxide-metal (MOM) capacitors have good linearity, those exhibit low capacitance density because of thick oxide layer. In addition, metal-isolation-metal (MIM) and poly-isolation-poly (PIP) capacitors show good linearity and high capacitance density due to thin oxide layer, however those require additional masks and more fabrication steps, thereby increasing manufacturing cost. On the other hand, MOSCAPs have high density of the capacitance, and those need no additional mask process. For the structure of the MOSCAP, the MOSCAP introduces capacitance between a bulk and a gate of the metal–oxide–semiconductor field-effect-transistor (MOSFET) as shown in

Figure 4c, and the gate and the source (connected with the drain) are two terminals of a variable MOSCAP. Then, increasing the input voltage,

between the bulk and the gate almost linearly decreases the capacitance between their two terminals, resulting in a MOSCAP as a variable capacitor. Those capacitors, however, suffer from the nonlinearity; a MOSCAP differently operates in three operation regions divided on the basis for voltage values across the MOSCAP, where its capacitance varies with the voltage value across the MOSCAP in the depletion region, while it is overall constant in the accumulation and inversion regions. As mentioned in

Section 1, in [

14], all the capacitors of the CDAC are replaced with variable MOSCAPs shown in

Figure 4c by carefully using the MOSCAPs in the inversion region, and thus a SAR ADC is calibrated based on the binary-weight relation among capacitors along with a dummy unit-capacitor for their calibration purpose. In the proposed work, the variable MOSCAPs employed from [

14] are fully charged in the precharge step. Then, because the passive CDAC of the CS SAR ADC is not connected with any power source, and also it has no connection with external circuitry, assuming a comparator has high impedance at its input terminal, the same amount of the net charges in the capacitors are retained until the sampling step is completed. Thus, the MOSCAPs stay in the inversion region during the calibration process. The variable MOSCAP shown in

Figure 4c is discussed in detail in [

14,

16]. The aim of this work is to accomplish a highly accurate calibration methodology by overcoming the drawback of a conventional split ADC, using a variable capacitor and its input voltage generator employed from [

14] in cal unit. In addition, the variable capacitors used for the cal unit can be a capacitor-array as well as a voltage-controlled capacitor (e.g., variable MOSCAP, varicap, and more). In fact, proposing a new variable capacitor along with its input voltage generator is not trivial, and thus it is out of scope of this work.

To be summarized, the components for this work are highlighted in blue in

Figure 3b, such as variable capacitors-based arrays of the CDAC, the nodes

, cal unit, and switches

. For efficiency, a set of the track/hold stage and the sample stage, which is designed for each of two ADC channels in a conventional split ADC, are merged into a single set which can be shared by the two ADCs for this work, so that ADC1 and ADC2 can use exactly same input stage, as shown in

Figure 3b.

3.2. Calibration process

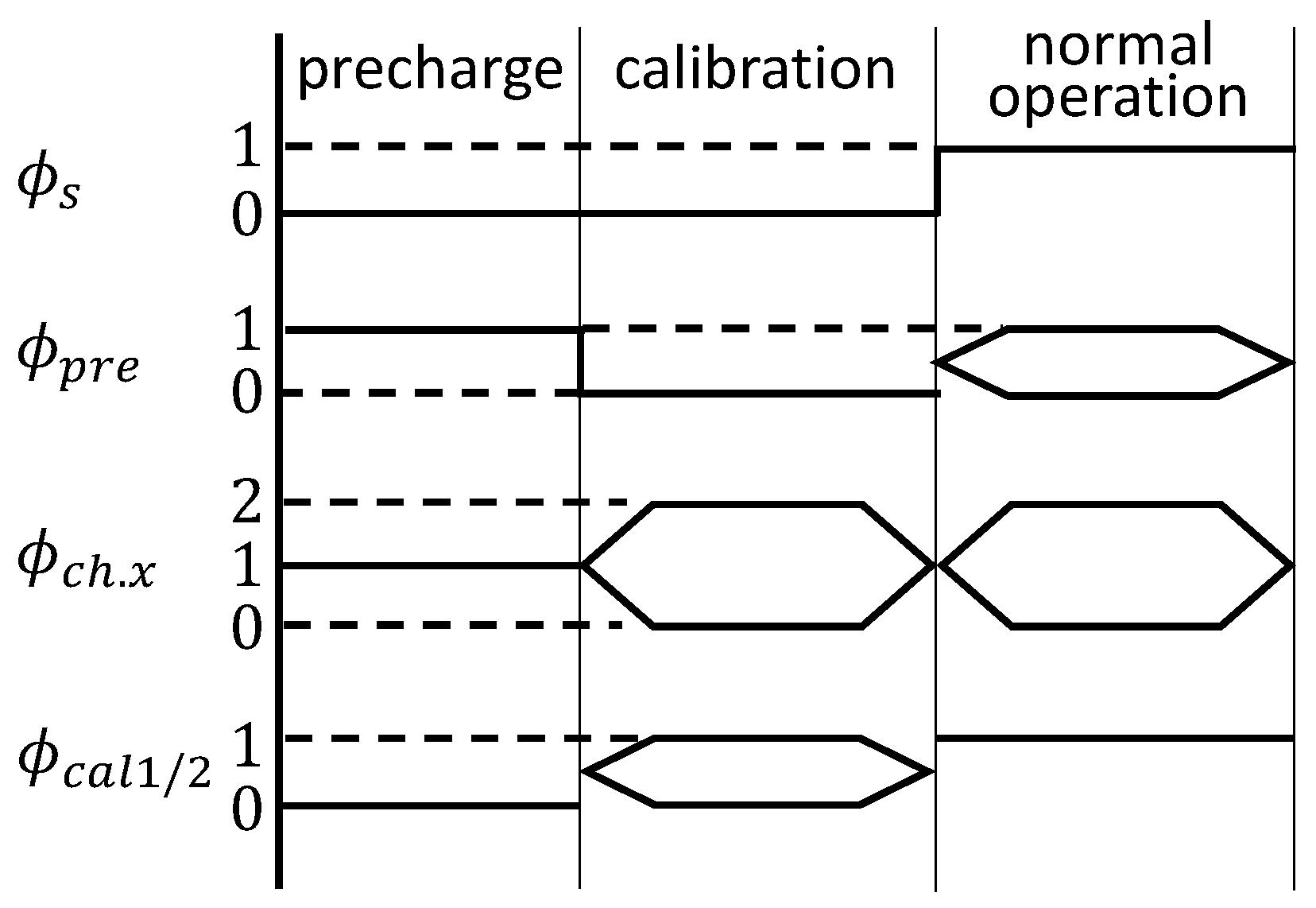

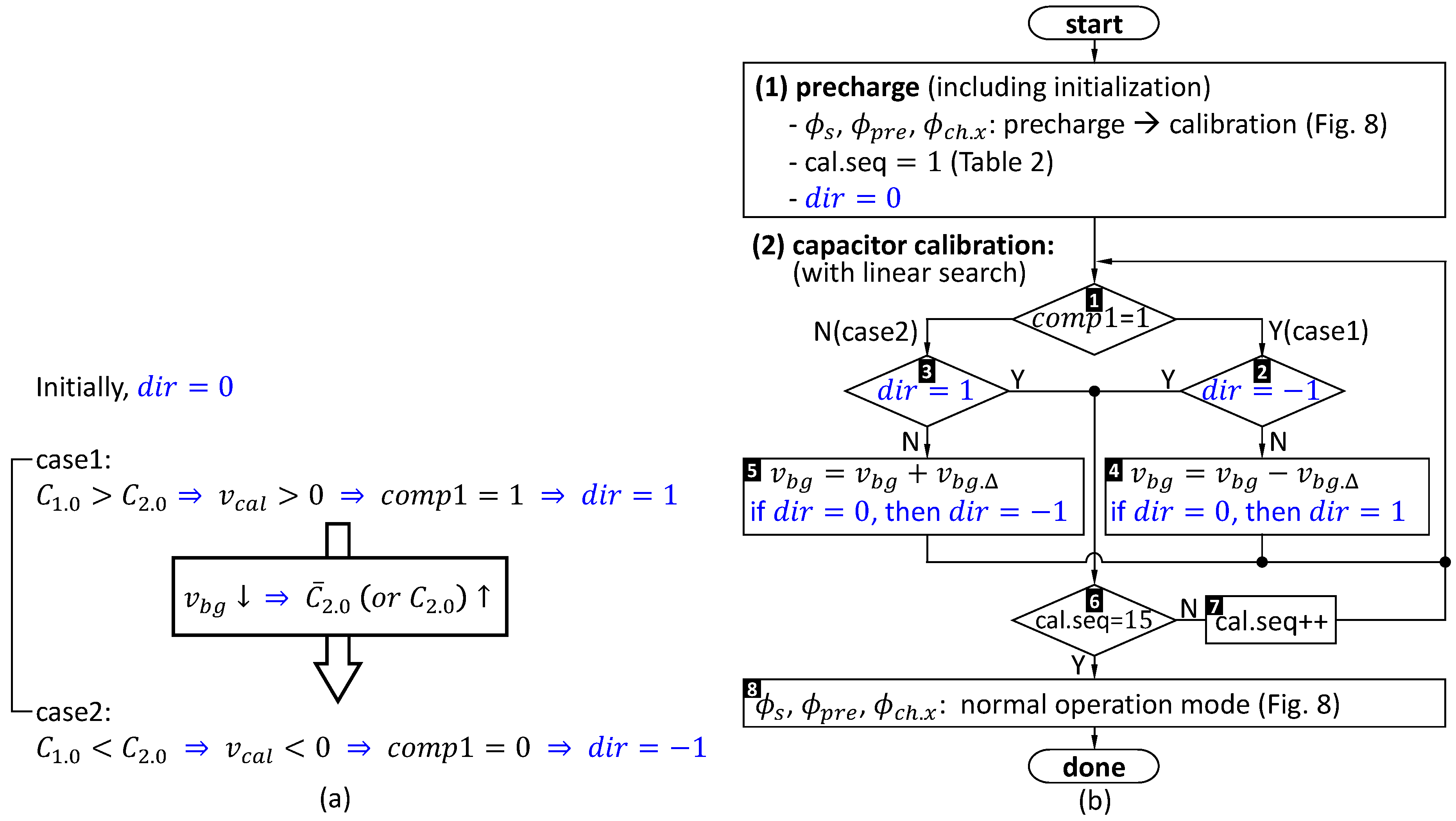

The procedure for the proposed foreground self-calibration is discussed in detail in this section. The proposed scheme is performed in two sequential steps: (1) precharge and (2) capacitance calibration, and the full process is operated by cal unit.

For the precharge step (i.e., the first step), the split CS-SAR ADC shown in

Figure 3(b) is reconfigured into that shown in

Figure 5, by performing the followings:

is open to disconnect the sampling stage (i.e.,

and

) from the CDAC for both the channels.

is closed to provide the charges to all the binary-weighted capacitors. The para-switches of all the capacitors are then connected to their

shown in

Figure 4b, and comp1 and comp2 are disabled. Finally, all the binary-weighted capacitors are fully precharged by

.

For the capacitance calibration (i.e., the second step), all the binary-weighted capacitors are sequentially calibrated in order from the least-significant-bit (LSB) capacitor to the most-significant-bit (MSB) capacitor, as listed in

Table 2, thereby completing all the capacitors in the binary-weighted relation. For better understanding, the first two sequences in

Table 2 are explained using

Figure 5,

Figure 6 and

Figure 7, and

Table 2, in detail as an example, instead of describing the generalized procedure.

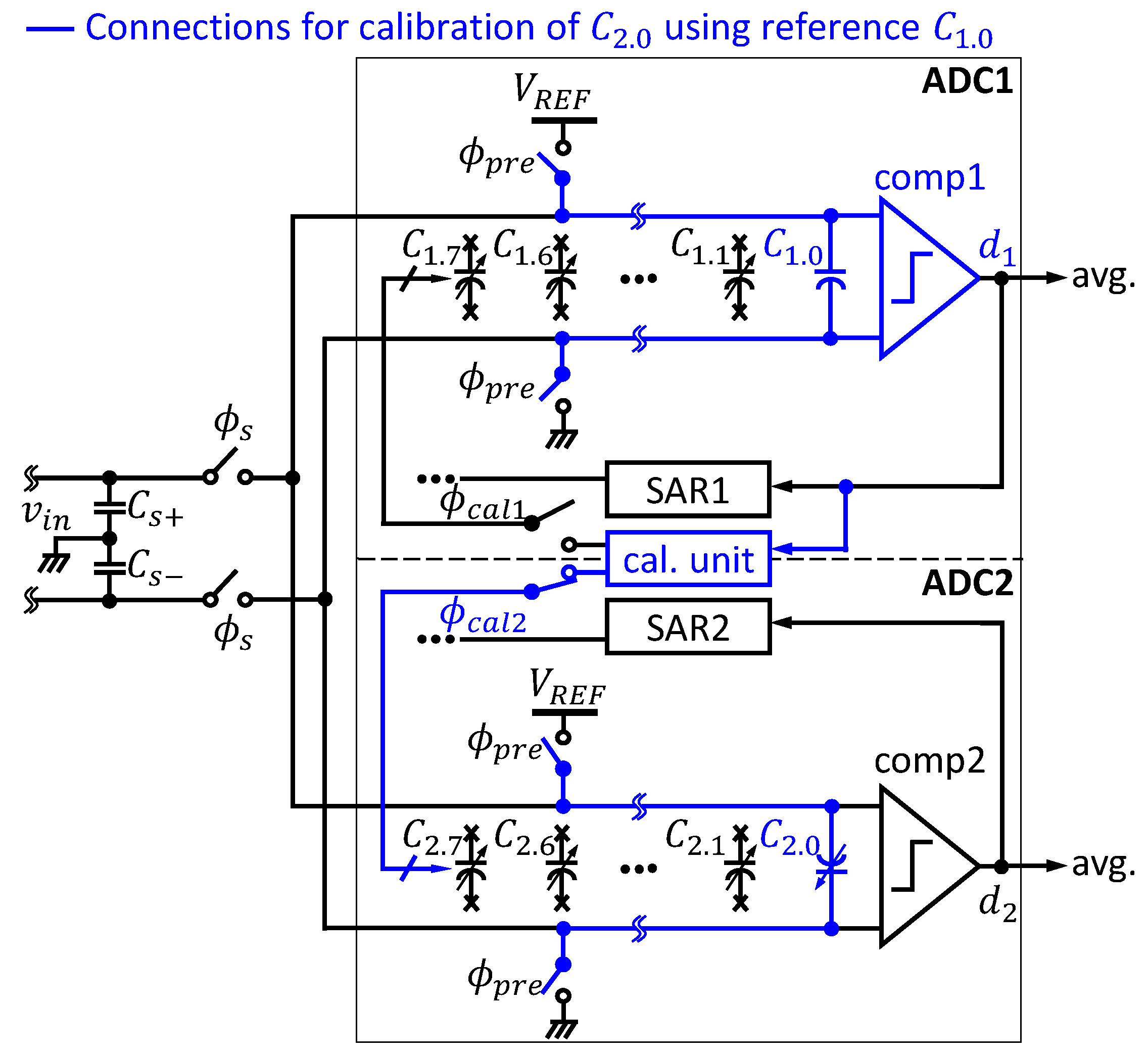

The first calibration sequence of

Table 2 calibrates

using

as a reference capacitor, without any change of

after its fabrication, as shown in

Figure 6. Firstly, the LSB capacitors of each ADC channel (i.e.,

and

) are connected to their top and bottom plates in antiparallel. In order for this,

is set on

as shown in

Figure 7a, while

is set on

as shown in

Figure 7b. On the other hand, all other capacitors are disconnected from the top and bottom plates by setting their para-switches on

n.c. (i.e., no connection). In addition, comp2 is disabled, and comp1 is enabled assuming that its common-mode voltage is ignored for simplicity. Basically,

of ADC2 is connected to

and comp1 by setting

open in both the two ADC channels as highlighted in blue in

Figure 6. The values of the switches for the proposed calibration mode and the normal mode are summarized in

Table 3 and

Figure 8. The only those effective circuits are depicted in

Figure 7c for better understanding.

In

Figure 7c,

, which is a voltage between the top and bottom plates, is derived by the charge conservation from (

3) to (

7). At the moment when

and

are initially (i.e., the time

right after the precharge step) connected in antiparallel,

is still dropped across each capacitor. As discussed in

Figure 4b,

and

are the parasitic capacitances for

, and

and

are the parasitic capacitances for

, as shown in

Figure 7a–c, as modeled in [

16]. Then, the overall initial charge

on the top plate in

Figure 7c can be identified as

where

and

are the initial charges on the top plate of

and the bottom plate of

, respectively, which are made in the precharge step. Thus,

is the sum of them in antiparallel circuit. Similarly, the overall initial charge

on the bottom plate of the CDAC can be found as

where

and

are the initial charges on the bottom plate of

and the top plate of

, for each. Similarly,

is the sum of them in antiparallel circuit as well.

On the other hand, if

, then the overall final charge

and

on the top and bottom plates can be found as

where

and

are the voltages at the top and bottom plates of the CDAC, and also it is defined as

, which is the input voltage of comp1.

Then, the two relations,

and

are obtained by the charge conservation, and those can be described using (

3), (

4), and (

5) as follows.

is finally obtained by solving the simultaneous equations of (

6) as

where

and

. The comparison technique using antiparallel connection among multiple capacitors has been used in a conventional CS-SAR ADC [

14,

15].

As shown in (

7),

is a function of

as a variable capacitance. Based on the correlation in (

7), the proposed calibration algorithm is simply overviewed in

Figure 9a. If

, then

, and accordingly comp1 output becomes 1, where this condition is defined as

case1 using a case indicator

. Since then,

is decreased to increase

, resulting in comp1

at the moment when

or

which is defined as

case2 represented using

. The linear search for the calibration of

finishes at this transition from the case1 to the case2, which can be considered as the moment when

or

. In addition, even in the opposite transition from the case2 to the case1, the linear search works similarly. Overall, the calibration process for each capacitor under calibration is finished at the transition between the case1 (

) and the case2 (

), where

initially.

Based on (

7) and

Figure 9a, the flow chart for this work is described as shown in

Figure 9b. The process in the flow chart is performed to calibrate capacitances, i.e., the second step of the proposed work. All those procedures are controlled by the linear search engine in cal unit shown in

Figure 3c. Initially,

right after the precharge step is done. We put numbers from #1 to #8 for each flow of

Figure 9(b). In #1,

in (

7) is measured by comp1, and then if comp1 output

or case1 (i.e.,

and

), then it is also asked if the current

in #2 to see if we were in the case2 previously, or to see if we are in the transition between the cases 1 and 2. Because

initially, we go to #4, and

becomes 1 to represent the case1. In addition,

is decreased by a step size

of a MOSCAP, thereby updating

. Then, we go back to #1 to check if comp1 output

after

is measured again, because

has a correlation with the updated

, as shown in (

7). If comp1 output

in this time, then we go to #3 which is the case2. Because we were previously in the case1 and thus currently

, this moment is the transition from the case1 to the case2 which can be considered as the moment when

or

, and thus the linear search finishes for the calibration of

, as discussed earlier.

may be correlated with its parasitic capacitances,

and

as shown in (

7), and thus

, which exhibits the correlation in (

7), is identified to meet

for the calibration of

. Next, we go to #6 to check if cal.seq

(i.e., the last calibration sequence of

Table 2). If no, then the second calibration sequence is set in #7 (i.e., cal. seq.

), which is discussed further below.

There can be a trade-off between

and the process time of the linear search, as in general linear search method; the higher

is, the sooner the linear search can be done, and the less accurate the searched value is (or vice versa). In addition, the following relation can be concluded from (

7) to meet

:

The second calibration sequence of

Table 2 calibrates

using a sum of

and

which has been previously calibrated, and thus can be reused as a reference capacitor, as shown in

Figure 10. Similarly,

is open.

and

of ADC1 and

of ADC2 are connected in antiparallel to the top and bottom plates, by setting

on

, and by setting

and

on

and

, respectively, as shown in

Figure 10a,b.

is connected to

(omitted for simplicity), as in

Figure 7b. All other capacitors are disconnected from the top and bottom plates, and also comp2 is disabled, while comp1 is enabled. As a result,

is connected to

and

in antiparallel, as depicted in

Figure 10c.

in

Figure 10c is obtained based on the charge conservation as follows. When

,

, and

are initially connected in antiparallel,

is still dropped across each capacitor immediately after the precharge step. As shown in

Figure 10(a–c),

and

are similarly modeled as the parasitic capacitances on the top and bottom plates of

and

, respectively. Then, the overall initial charge

and

on the top and bottom plates in antiparallel circuit in

Figure 10c can be identified as

where

,

, and

. In addition,

,

, and

.

and

are the initial charges on the top and bottom plates of

, respectively, which are made in the precharge step.

On the other hand, if

, then the overall final charge

and

on the top and bottom plates can be found as

Then, the two relations,

and

are obtained by the charge conservation, and those can be described using (

9) and (

10) as follows.

where

,

,

, and

. Finally,

is obtained by solving the simultaneous equations of (

11) as

As in the previous example, the linear search engine in cal unit finds

that satisfies

in (

12). The flow chart of

Figure 9b works for this example as well.

may be correlated with its parasitic capacitances as shown in (

12), and thus

is identified to meet

for the calibration of

as well. In addition, the following relation can be concluded from (

12) to meet

.

All other calibration sequences in

Table 2 can be also similarly processed. It can be observed in

Table 2 that one (or two) reference capacitor is used in the odd(or even)-numbered calibration sequence. In summary, the proposed calibration scheme updates all the capacitances to be in the binary-weighted relation using only one or two reference capacitors, based on an actually fabricated LSB capacitor

, instead of forcedly updating each capacitance into a specific value predefined by the design specifications.

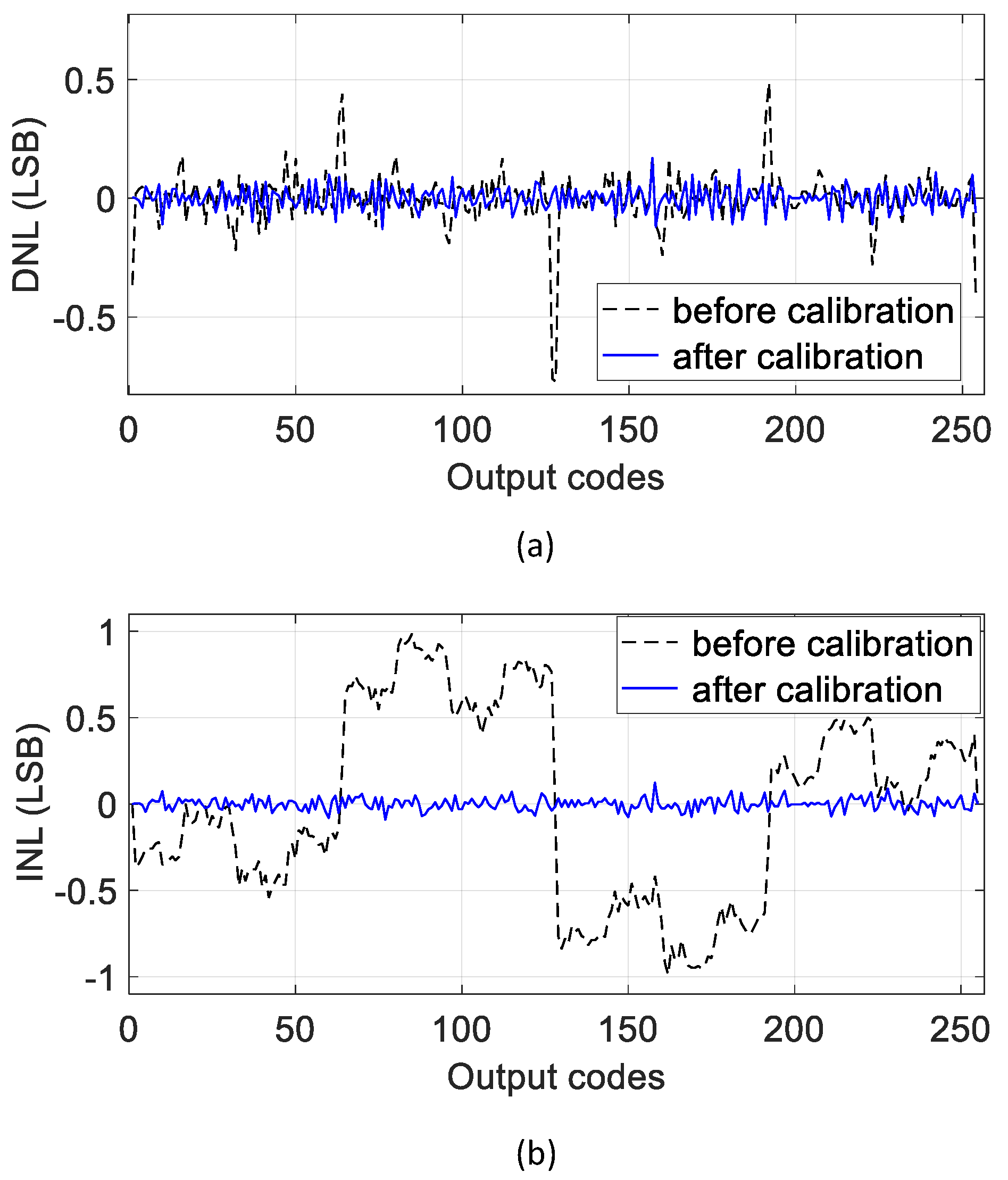

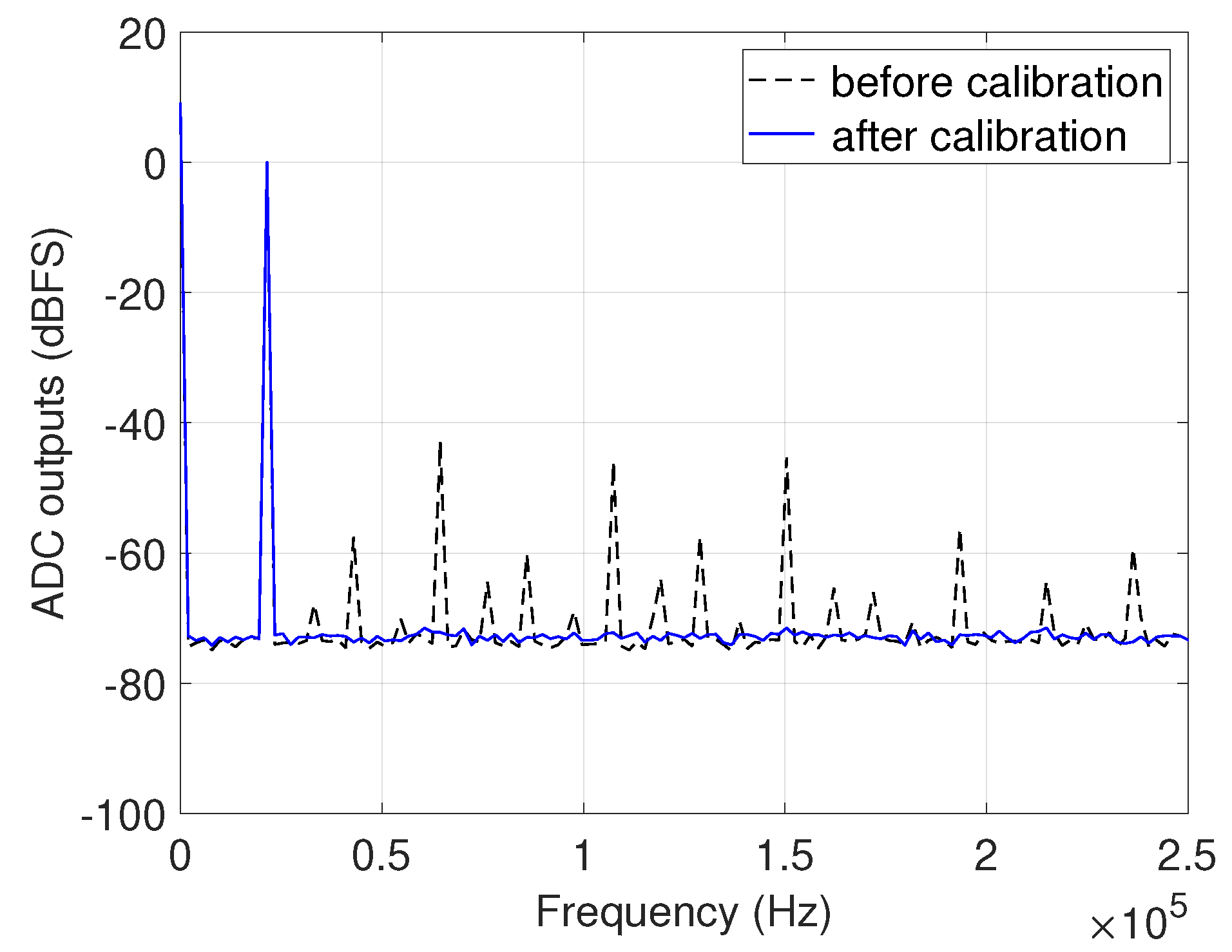

Several benefits of this work are summarized as follows:

The proposed work does not require an adaptive algorithm e.g., LMS as in [

10], and thus the heavy calculation process is not needed, and a digital hardware logic for calculation, i.e., a calibration unit, can be much simpler.

This work does not require a dummy unit capacitor, e.g.,

by employing two-ADC channel configuration. In [

14],

is required to make the number of capacitors a power of 2, so that

under calibration can be compared with

by a comparator for the capacitor mismatch calibration. For the proposed work, two unit capacitors are available from the two original ADC channels, and thus those capacitors facilitate the capacitance calculation based on a power of 2 without a dummy unit capacitor, as shown in

Table 2.

Using a small number (i.e., at most two) of the reference capacitors allows this work to make simple connection of capacitors as well as simple calculation in cal unit. For example of [

14] with a 16-bit ADC,

is calibrated using one reference comparator,

.

is calibrated using 2 reference capacitors,

, and finally calibrating

requires a sum of 16 reference capacitors,

. Thus, total 136 reference capacitors are required to calibrate all the 16 capacitors of the CDAC. Basically, an

N-bit ADC is calibrated using exponentially increased

reference capacitors. On the other hand, the proposed work with a 16-bit ADC uses only 46 reference capacitors to calibrate all the capacitors of the two ADC channels. Thus, an

N-bit ADC is calibrated using linearly increased

reference capacitors for this work. As a result, this work uses only

, and

of the reference capacitors required for [

14] (i.e.,

), for

, and 18-bit ADCs, respectively. Therefore, as an ADC has higher resolution, i.e., more capacitors, the proposed calibration scheme significantly reduces the complexity both in the connection of the capacitors and the calculation process in cal unit.