2.1. Traditional Structure

The Single Slope ADC traditionally comprises a comparator, ramp generator, and counter. The ramp generator initiates a gradually decreasing voltage signal, with the counter tallying from the onset of this ramp. The pixel output is then compared to this slope voltage, yielding the SS ADC’s quantization result after decoding.

At higher quantization bits, the quantization speed of SS ADC will be affected due to the increase of slope length. While ensuring high quality and high integrity of image information, image sensors need to have a higher frame rate and faster response speed. Two-step SS ADC based on TDC can meet the needs of high-speed CMOS image sensors, and is increasingly used in the field of CMOS image sensors.

The working mode of the two-step SS ADC based on TDC is that the pixel signal will be compared with the ramp signal. When the pixel signal voltage is higher than the ramp voltage, the comparator will flip, and the output of the comparator will be coarse quantized by the post-feed counter, while the TDC will fine quantize the comparator flip signal. That is, the coarse quantization counts the number of clock cycles from the highest point of the ramp voltage to the comparator flip point, while the fine quantization quantifies the time from the comparator flip point to the end of its clock cycle. The two-step quantization method can effectively alleviate the energy consumption and load driving problems caused by too high clock frequency.

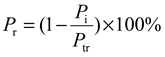

The comparator in SS ADC based on TDC usually adopts the fully differential comparator structure as shown in

Figure 1. The working process is as follows: Switch S2 is closed, the two-stage comparator is reset, switch S1 is closed, and the voltage of

Vin+ and

Vin- is connected to the left plate of corresponding capacitor

C1, respectively. When the voltage of

Vin+ and

Vin- is stabilized, S1 and S2 are disconnected. In order to inhibit the channel charge injection of the S2 switch, the turn-off time of S1 is 4 ns later than that of S2. The input signal is then quantized, and the second level comparator converts the double-ended output into a single-ended output.

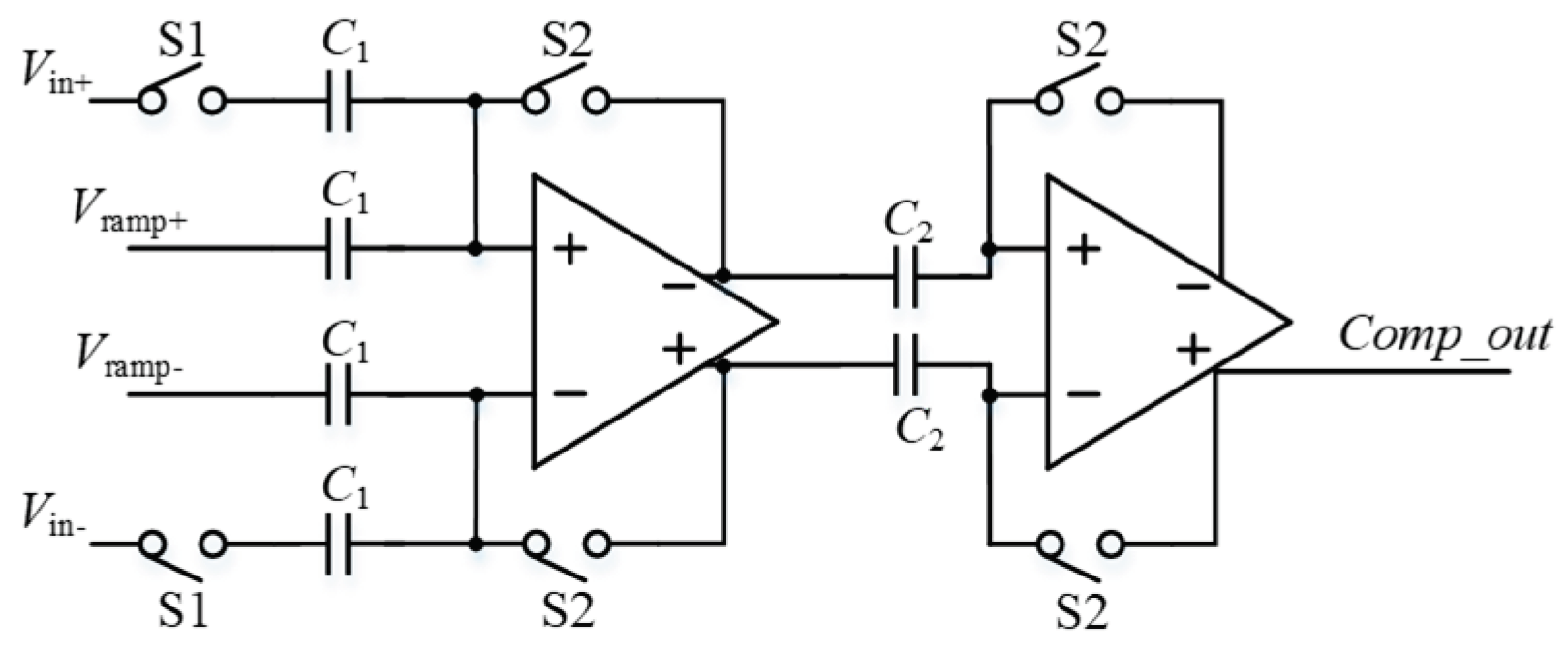

The structure of the single-stage comparator in a fully differential two-stage comparator is shown in

Figure 2. Considering the input common model envelope of the comparator input signal, the differential input pair tube adopts a PMOS transistor. Assuming that

Vin+ and

Vin- are common-mode signals when the comparator starts to work, if

Vin+ increases and

Vin- decreases, the overdrive voltage of the M3 transistor will decrease, the leakage current will decrease, and the leakage current of the M4 transistor will increase. Because the gate leakage of M5 and M8 transistors are connected, they are always in the saturation region, and the change of current will reduce the gate voltage of M5 transistor. That is, when

Vin- decreases, the gate voltage of M8 transistors increases, that is,

Vin+ increases. At the same time, the gate voltage of M6 and M7 transistors is controlled by

Vin+ and

Vin- respectively. Therefore, the increase of

Vin+ will increase the leakage current of M6 transistors, thus making M6 distribute more current, which makes the leakage current of M5 transistors smaller, and its gate voltage further decreases, forming a positive feedback. Similarly, the gate voltage of the M8 transistor will further increase, and finally, M6 will enter the deep linear region, M7 will enter the cut-off region, the comparator will complete the comparison,

Vin+ output high level, and

Vin- output low level.

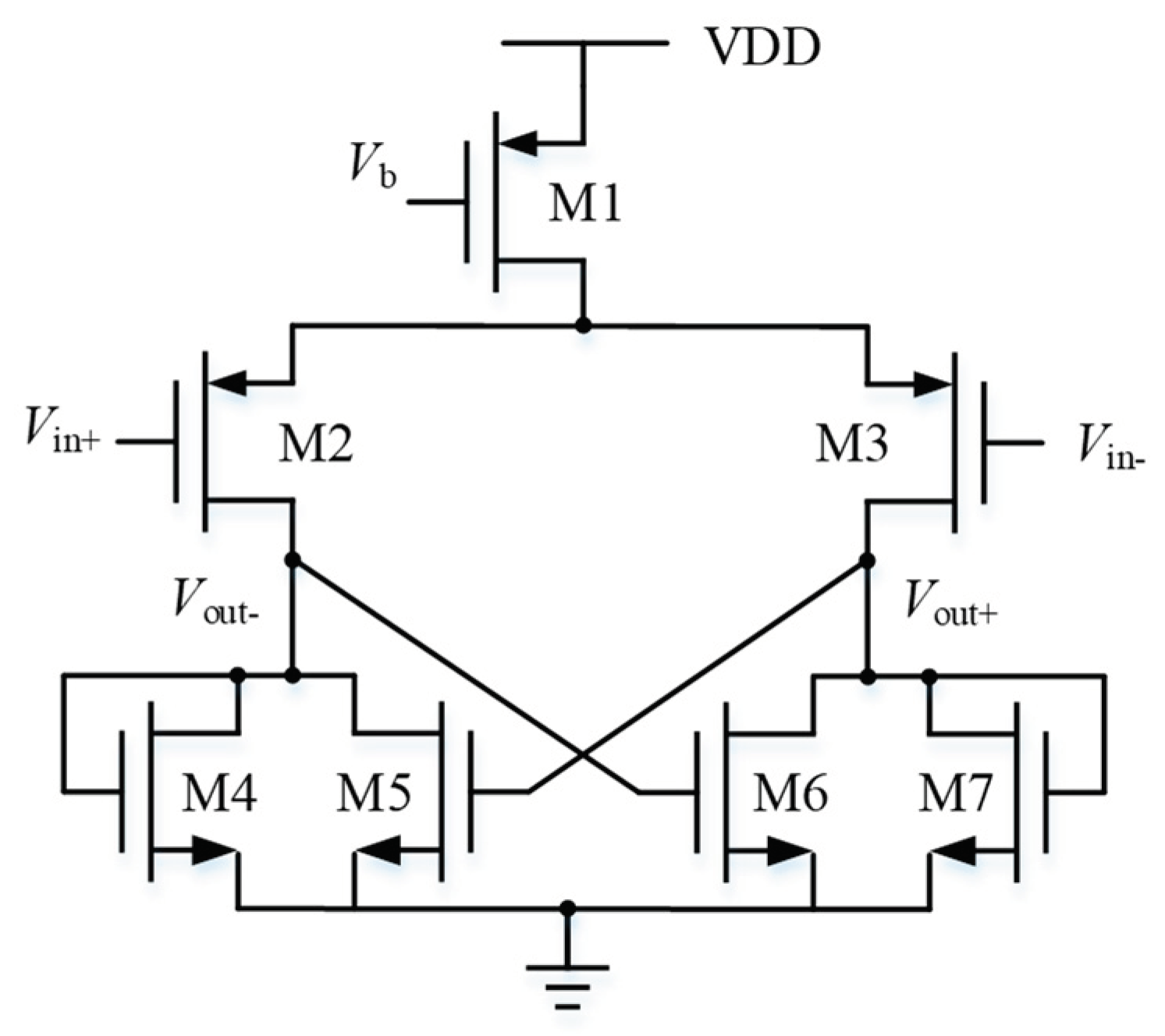

The traditional TDC structure for CMOS image sensors is shown in

Figure 3, which is mainly composed of a delayed phase-locked loop, delay chain and D-flip-flop. The pixel output is transmitted to the column level for comparison with the reference ramp, and the point in time at which the comparator flips is transmitted to the delay-locked loop (DLL) delay chain. 2

n delay units are required to complete

n-bit quantization. The rising edge of the comparator flip is delayed by each delay unit with the same time accuracy, and the output of each delay unit is connected to the signal input of the D flip-flop. The rising edge of the next clock cycle will be sent to the clock input of the D flip-flop as a

stop signal. The clock signal will sample the signal input of the D flip-flop and read the output of the delay unit into the D flip-flop. Then the D flip-flop is used as a shift register, the data in the D flip-flop is passed to the decoder, and the final N-bit quantization result is obtained.

The main power consumption of TDC comes from the power consumption of the delay unit and the D flip-flop, where the delay unit ensures the accuracy of the delay time, and its current size is determined by the

Vctrl provided by the DLL. The power consumption of CMOS circuit is

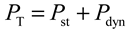

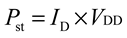

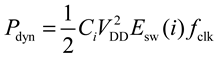

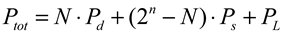

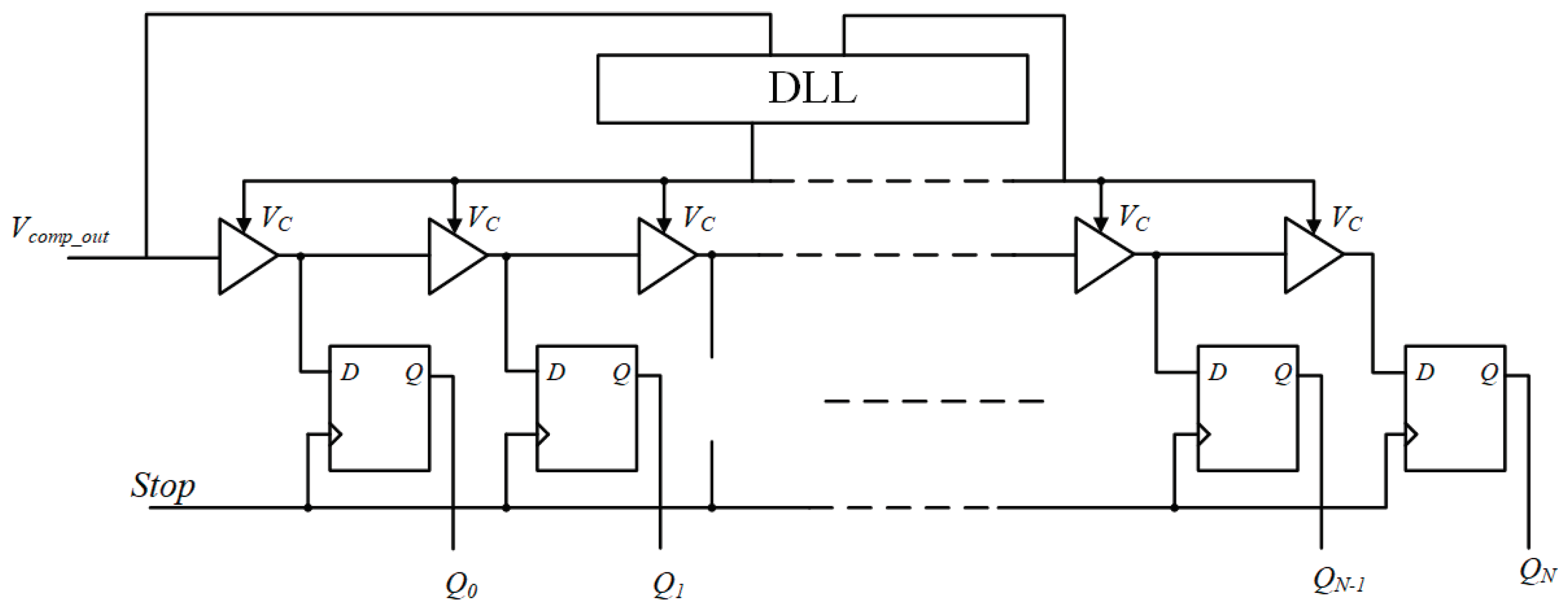

where

PT is the total power consumption,

Pst is the static power consumption, and

Pdyn is the dynamic power consumption. Static power consumption is mainly caused by drain current, and static power consumption is

where,

ID is drain current and

VDD is power supply voltage. Dynamic power consumption is mainly caused by the charge and discharge of the circuit to the node capacitor. Each charge (or discharge) of a node capacitor

C will lead to the dynamic power consumption of 1/2

CVDD2. Therefore, the average static power consumption of a node i in the circuit during the whole working time can be expressed as [

13]

where,

fclk is the clock frequency and

Esw is the switching activity, which represents the average number of jumps of the node i signal in each clock cycle. Therefore, the more the number of signal jumps of the D flip-flop, the higher its dynamic power consumption, resulting in a higher total power consumption.

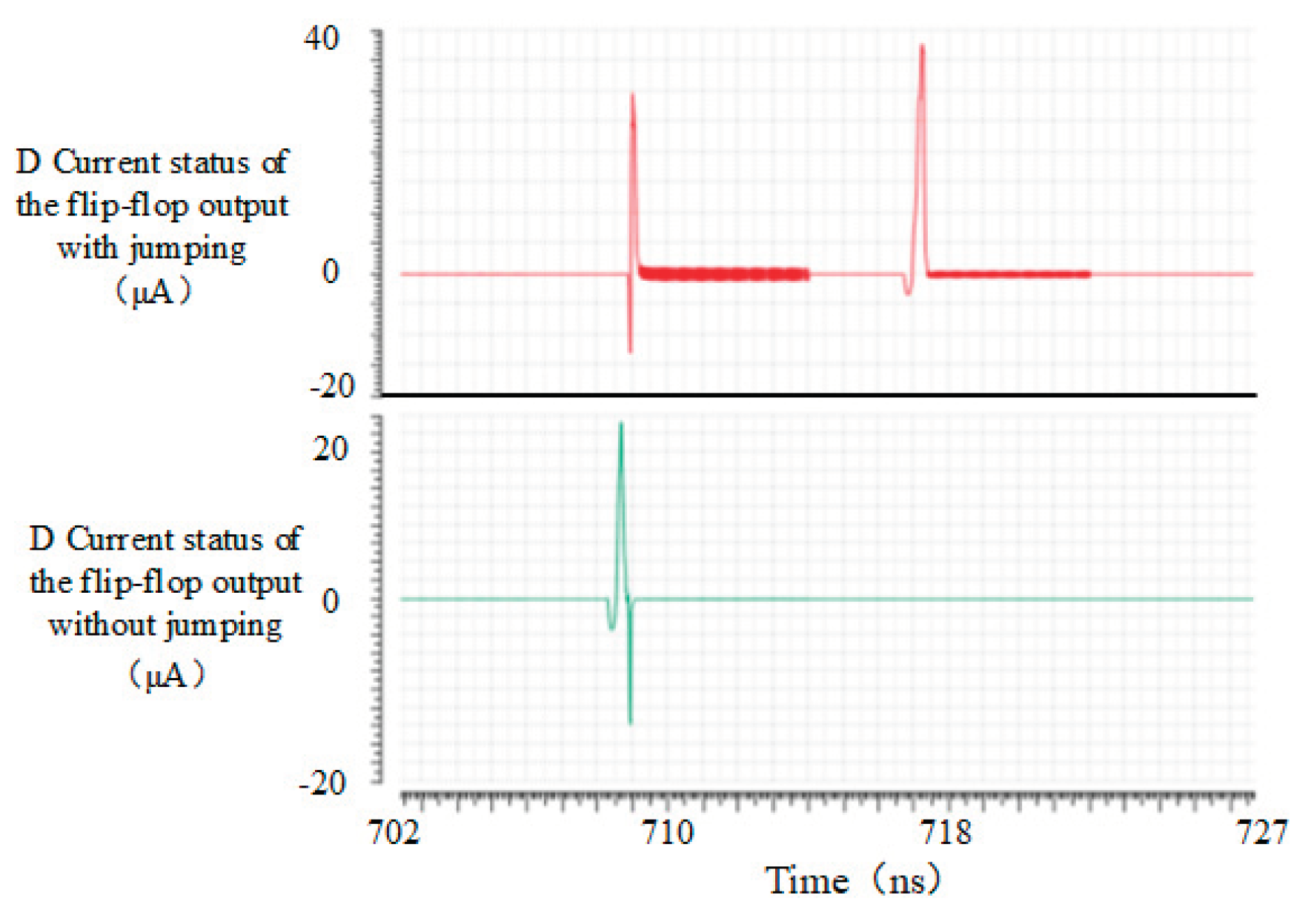

In the simulation process, it can be found that when the signal input of the D flip-flop is kept at a low level, its power consumption level is far less than that when the signal input has a high level. Simulation of the D flip-flop we used is carried out, as shown in

Figure 4, respectively, the current condition of the output of the D flip-flop becomes high level and the current condition of the input and output of the D flip-flop is kept low level. It was calculated through a calculator that the average current when the output remained low was 32.88 nA, while the average current when the output changed was 217.2 nA. It could be seen that the average current of D flip-flop would be significantly increased by flipping. The power consumption of D flip-flop was mainly the power consumption of its flipping. Therefore, if a new counting method is adopted to reduce the flipping times of the D flip-flop in TDC, low power consumption can be achieved.

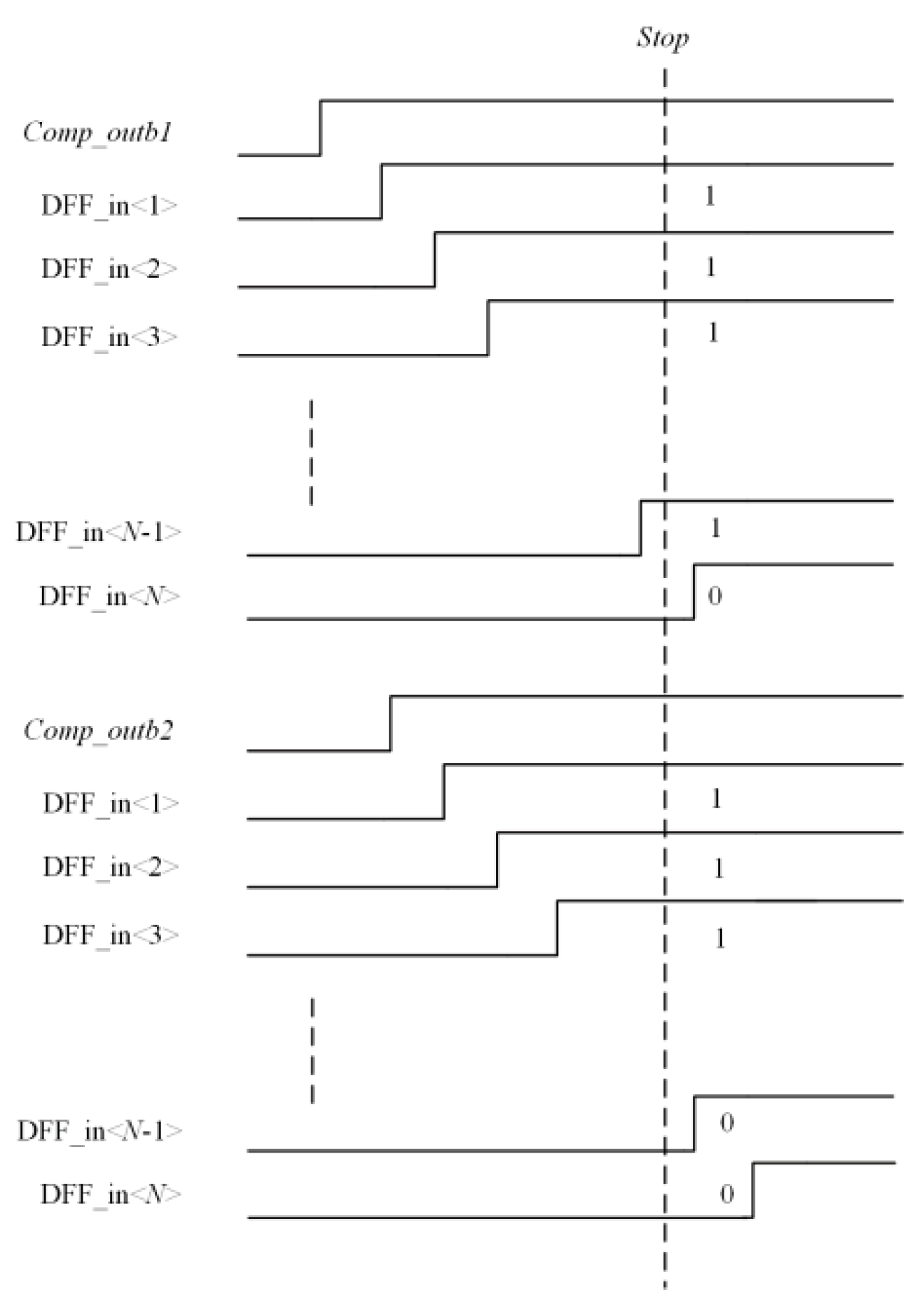

The output of the delay chain in the quantization process is shown in

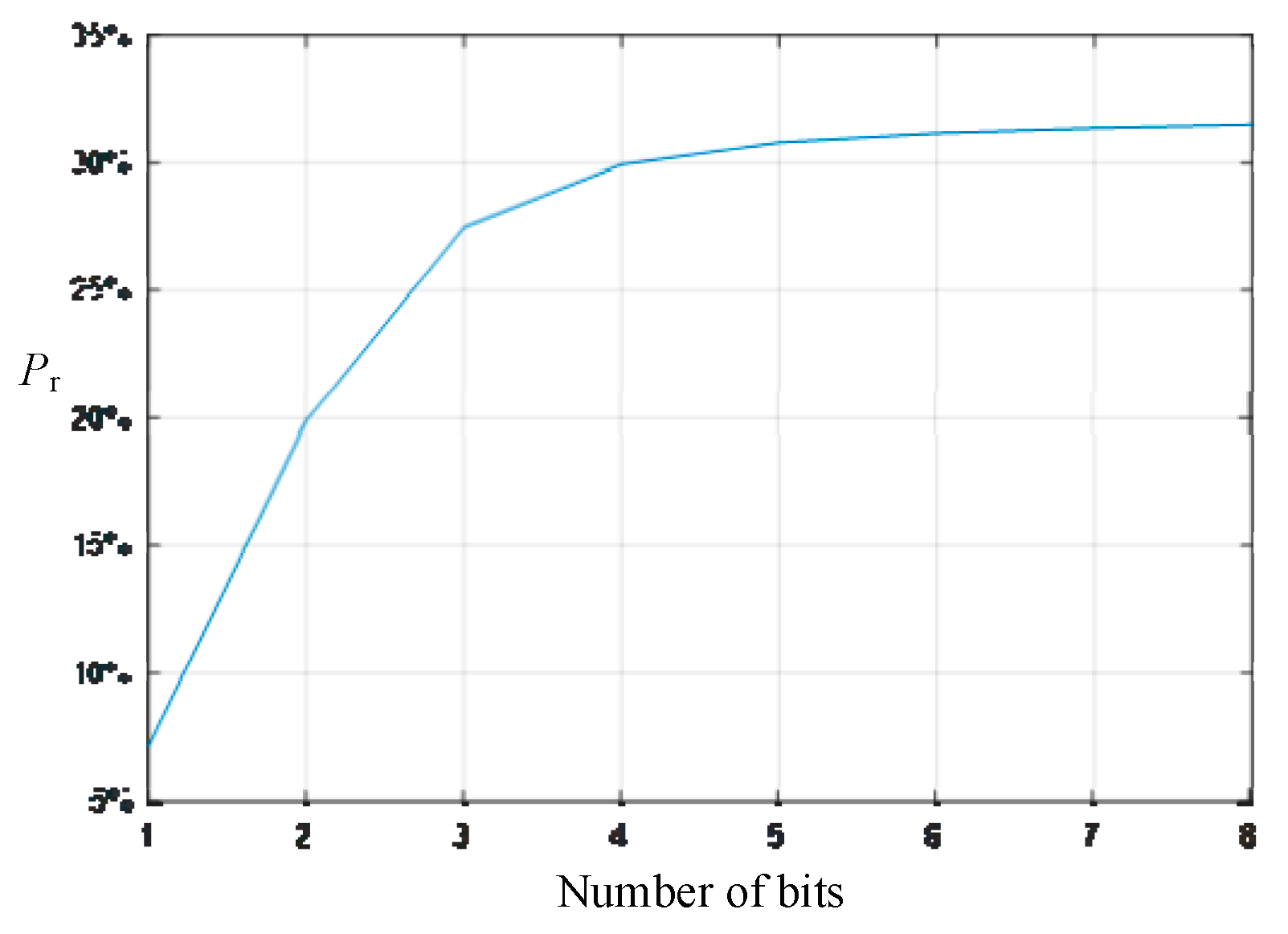

Figure 5. Where Comp_outb1 and Comp_outb2 represent the inversion signal of the comparator in the first and second rows respectively, and DFF_in<

N> represents the input of the NTH D flip-flop, which is the output of the NTH delay unit. When the

stop signal arrives, each D flip-flop will sample the output of the delay unit and generate a thermometer code with 1 and 0 separated as 111…00. Due to the continuity of the analog signal, the light intensity information between the two adjacent rows of pixels is generally very close, so its quantization code value will also be very close. If a more simplified quantization method that quantizes the difference between two rows of pixel signals rather than the full signal can be adopted to eliminate the quantization of the same part between the two rows of signals, the quantification of redundant information will be removed. The number of output signals of 1 can be reduced, that is, the number of flips of the D flip-flop can be reduced, thus reducing the counting power consumption.

The main source of ADC differential nonlinearity is the random variation of the delay time of the delay unit buffer caused by the inconsistency and mismatch of the device manufacturing. The greater the number of delay buffers, the greater the differential nonlinearity, which will cause a certain error. In addition, the D flip-flop must ensure that it has a narrow metastable width, which must be shorter than the delay period of the delay unit, so as to reduce the TDC time measurement error.

2.2. Proposed TDC

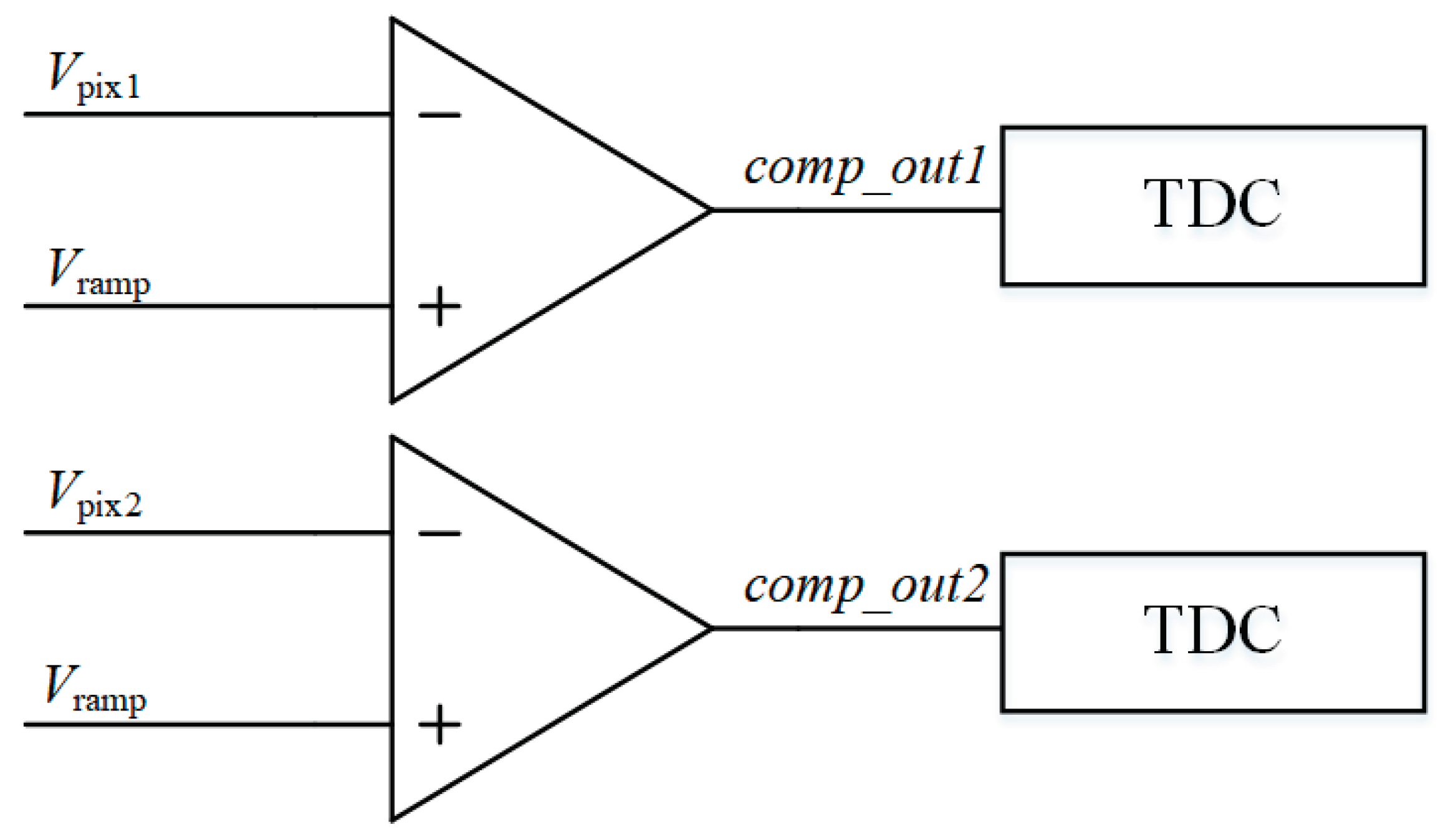

The improved column-level readout architecture is shown in

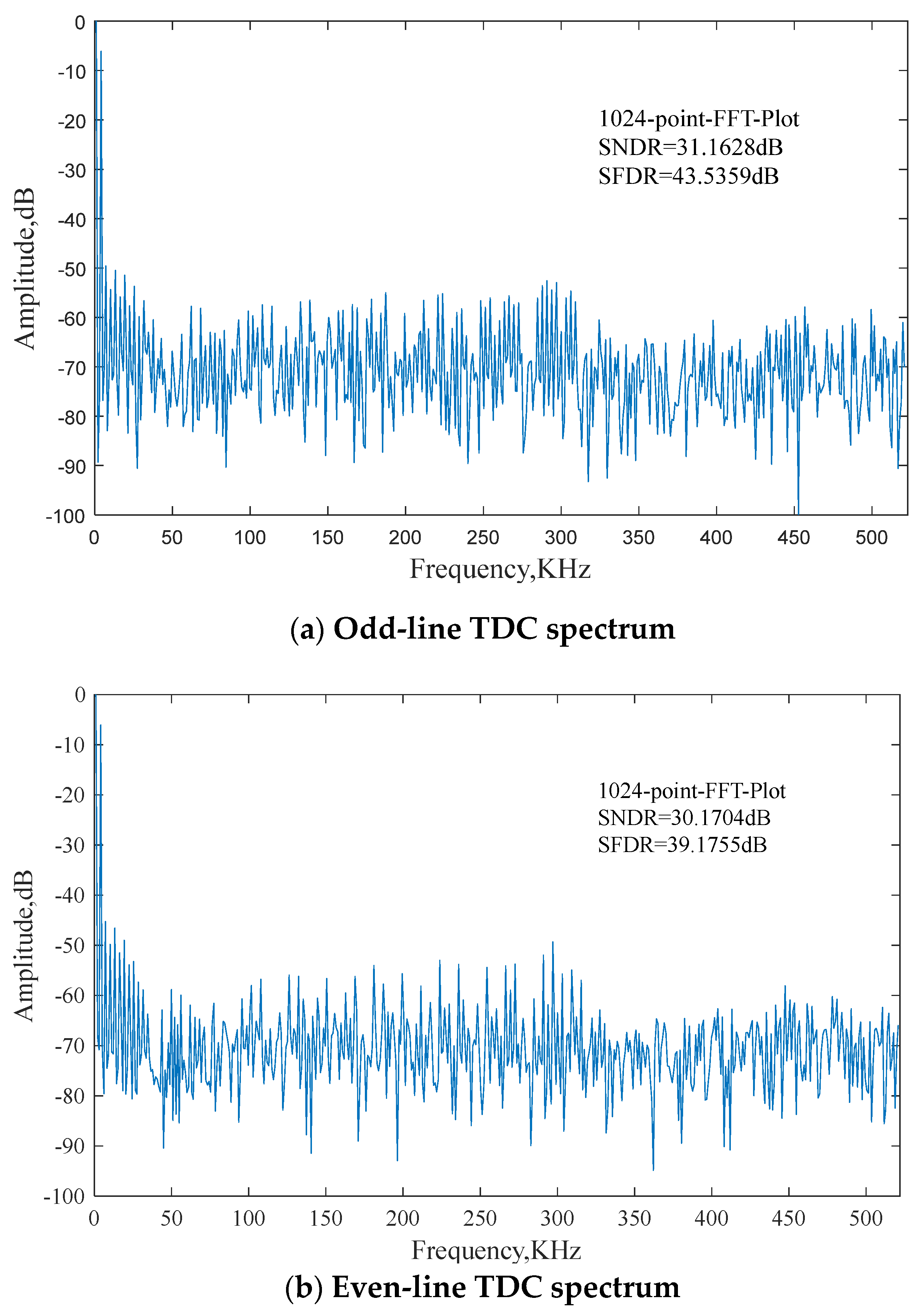

Figure 6. Since the output of two rows of pixels needs to be compared to quantify their difference, two column parallel buses need to be used for simultaneous readout, and the output of pixels is sent to the column-level comparator for comparison with the reference slope voltage respectively. When the output signals of the two rows of pixels are different, the flip time of the comparator will also be different. By sending the outputs of the two comparators into two sets of TDC for quantization at the same time, the flip time point of the comparator, that is, the output signal of the pixel, can be encoded.

In high-speed image sensors, considering the RC delay of the row driver signal transmission line and column bus, the row driver signal is difficult to be completed from the timing control driver circuit on both sides of the pixel array to the most middle column pixel in the row selection time, and the most middle row pixel signal is output to the column level through the column bus.

Under the premise of not reducing the pixel array and frame rate, to achieve complete signal transmission within the row time, the mode of simultaneous readout of two column buses proposed in this work can be adopted. Each column pixel shares two column buses, and the pixel output of odd and even rows is transmitted to the column level respectively. In this way, the timing control driver circuit can select two adjacent rows of pixels each time. The signal is selected and read at the same time, each column bus only needs to complete the selecting and reading of half of the pixel output in one frame time, and the row selection time can be doubled, which greatly alleviates the pressure of signal establishment in the row selection time. Therefore, the proposed TDC is very suitable for high-speed CMOS image sensors.

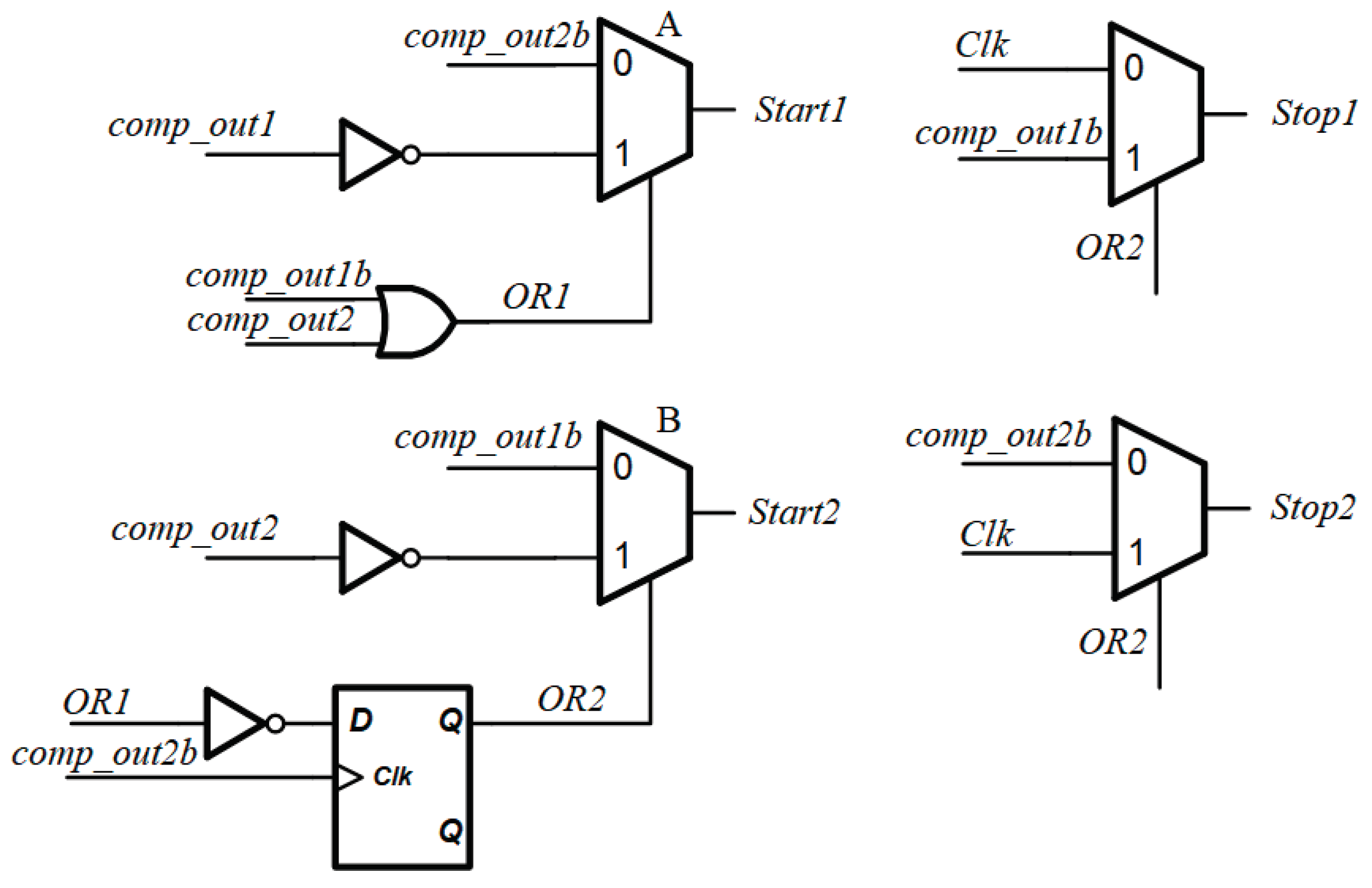

For TDC to quantify the difference between the output of two rows of pixels, it is necessary to quantify the time difference between the flip time points of the two rows of comparators. This work designs a series of logic circuits before TDC. The following purposes can be achieved by using the logic circuit as shown in

Figure 7.

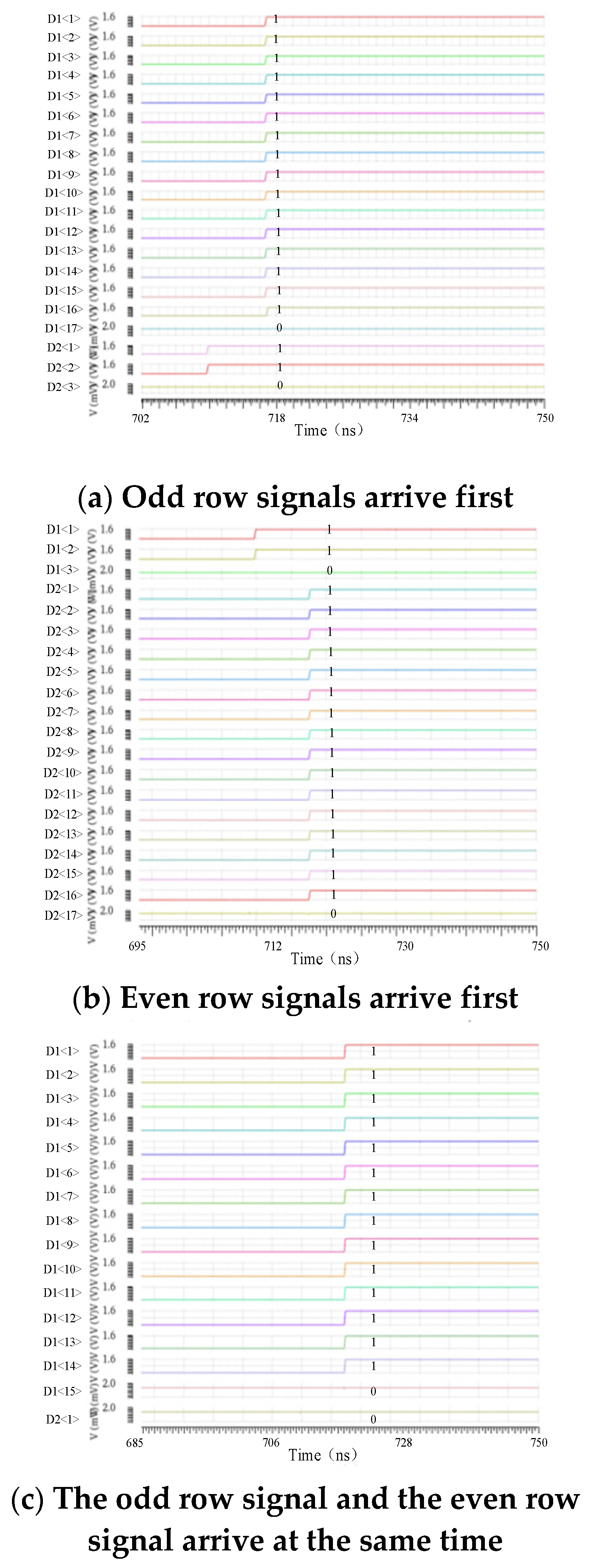

In the initial state disjunction gate output OR1 is high, when comp_out1, that is, the first-row comparator flip time point arrives earlier than comp_out2, disjunction gate output remains high, the output of multiplexer A is the delay of the first-row comparator flip invert signal, and the signal which will be delayed by the delayed chain is sent to the start signal input of the first row TDC. At this time, the clock input of D flip-flop has not yet arrived, and its output is the default value after reset, that is, the low level. The output of multiplexer B is also the delay of the first row of the comparator flipping invert signal, and the start signal of the two rows of TDC is the delay of the first row of the comparator flipping invert signal. After that, even if the second row of the comparator flipping time arrives, the value of OR1 remains unchanged. The output of the D flip-flop will also remain low; Since the output of the D flip-flop remains low, the stop signal of the first row TDC is the rising edge of the next clock cycle, and the stop signal of the second row TDC is the delay of the second row comparator flip invert signal.

When comp_out2 arrives before comp_out1, the output OR1 of the disjunction gate will become low, the output of multiplexer A will be the delay of the second row comparator flip invert signal, the output of the D flip-flop will also jump to a high level, and multiplexer B will select the delay of the second row comparator flip invert signal. At this time, the stop signal of the second row of TDC is the rising edge of the next clock cycle, and the stop signal of the first row of TDC is the delay of the first row of the comparator flip invert signal.

It can be seen that the first arrived comparator flip signal will be fully quantized the time from the flip time point to the rising edge of the next clock cycle, and the other row of TDC completes the quantization of the time difference between the flip points of the two rows of comparators. Due to the spatial continuity of the analog signal, the difference is usually relatively small. Therefore, this quantization method can reduce the number of flips of the D flip-flop, thereby reducing the power consumption of the count. In addition, in traditional TDC-based SS ADCs, an edge detection circuit is usually needed to generate a

stop signal, that is, the comparator flip signal is delayed, and the D flip-flop is used to sample the end of the clock cycle where TDC quantization is located, that is, the rising edge of the next clock cycle. In the improved TDC, the

stop signal of the faster row of the comparator flipping signal is the end of the whole quantization time, and the

stop signal of the slower row of the comparator flipping signal is the

stop signal of the other row of TDC. Therefore, the improved TDC does not need the edge detection circuit to provide the

stop signal, which can further save power consumption. The TDC-based SS ADC used in Ref. [

6], the edge detection circuit is usually needed to generate the

stop signal, that is, the comparator flip signal is delayed, and the D flip-flop is used to sample the end of the clock cycle where the TDC quantization is located, that is, the rising edge of the next clock cycle. In the improved TDC, the

stop signal of the faster row of the comparator flipping signal is the end of the whole quantization time, and the

stop signal of the slower row of the comparator flipping signal is the

stop signal of the other row of TDC. Therefore, the improved TDC does not need the edge detection circuit to provide the

stop signal, which can further save power consumption.