1. Introduction

Gallium nitride (GaN) based material has shown an outstanding potential as a candidate for future power devices overcoming silicon (Si) and silicon carbide (SiC) limitations such as physical properties or cost of fabrication. Indeed, high GaN epi-layer quality can be grown on silicon substrate, enabling to benefit from a high electron mobility, a high electric field and a large band gap at silicon cost. However, reliability issues still plague well established lateral GaN high electron mobility transistors (HEMTs) for high voltage (HV) applications (beyond 600 V voltage operation)[

1,

2]. Vertical GaN technology grown on low-cost foreign substrates is a promising solution for medium and high voltage applications[

3,

4,

5,

6,

7,

8].

GaN P-N junction based vertical structures offer robust performance including avalanche breakdown capability and high current spreading while maintaining small device dimensions[

3,

9,

10]. Most of the reported vertical GaN on silicon devices have a pseudo vertical structure, where the backside layer is reached from the front side by dry etching. This structure is widely used since the process is relatively straightforward as no backside processing is required to fabricate the discrete devices. On the other hand, unlike fully vertical structures, pseudo-vertical devices suffer from the so-called current crowding effect directly affecting the on-state behavior due to thermal dissipation issues[

11]. It can be pointed out that this undesired effect scales with the device dimensions, which makes the fully vertical structure mandatory. The development of a fully vertical structure based on GaN grown on silicon substrate is achieved by means of a local substrate and buffer layer removal[

12,

13]. In this case, one of the key challenges is the development of the backside ohmic contact due the inherent N-face polarity of the n+ doped GaN layer[

14]. This problem is also faced with the vertical GaN-on-GaN structure in the field of power electronics and optoelectronics [

14,

15,

16,

17,

18,

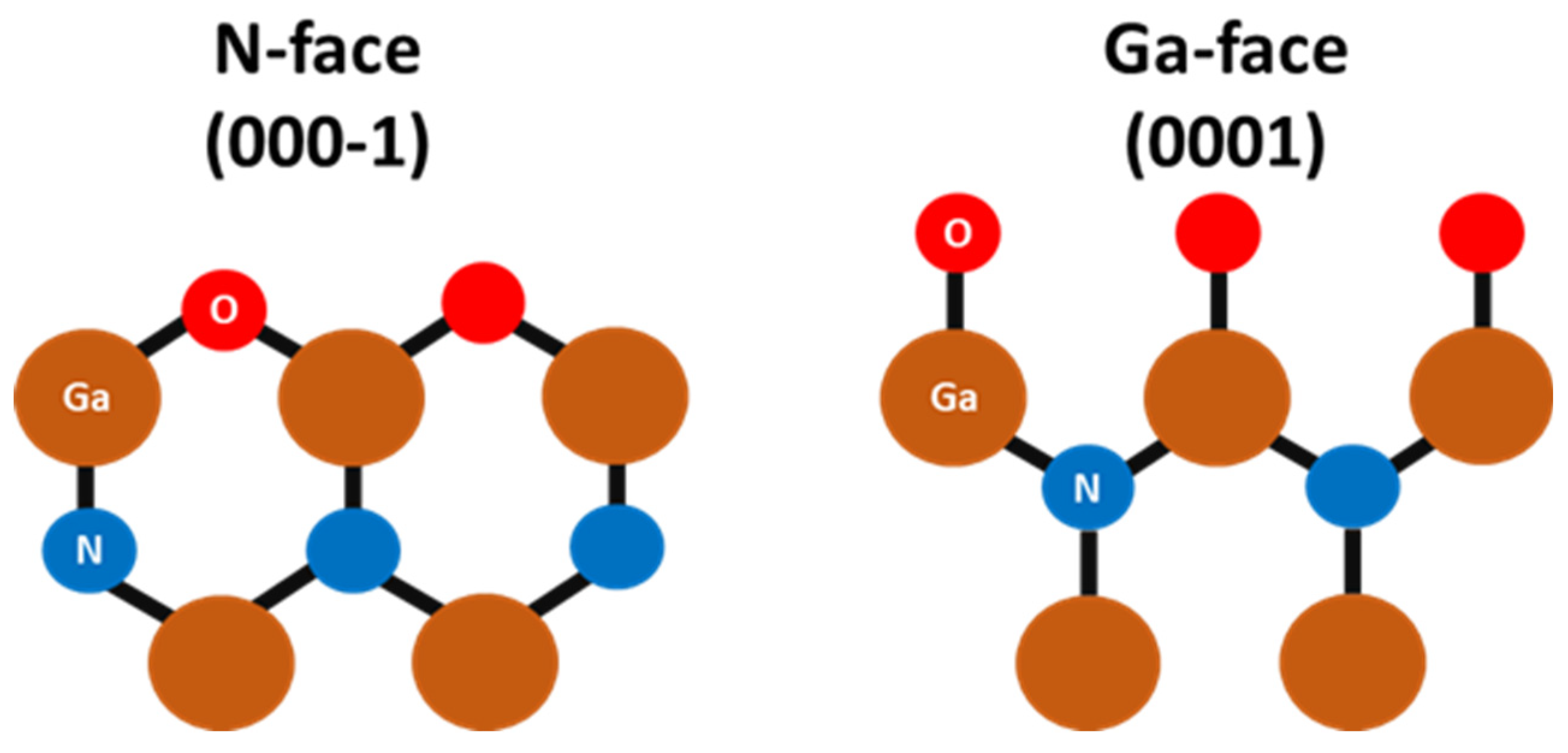

19]. Unlike Ga-face, the formation of low resistive ohmic contacts on the nitrogen face of n+ layer is more complex due to the inversed polarity from the backside, the atom position in Wurtzite crystal of GaN is prone to high oxidation (Figure 1a)[

20]. In this work, we propose a simple approach to overcome this issue. A high temperature HCl based wet treatment of the GaN surface was developed which significantly enhanced the ohmic contact quality under specific treatment conditions. TLM lift-off inside GaN on Silicon membranes using laser direct lithography has been developed allowing proper characterization of the contact resistances on top of the N-face n+ doped GaN backside layer. The electrical results are supported by X-ray photoelectron spectroscopy (XPS) and scanning electron microscopy (SEM) analysis to reveal the impact of the wet treatment.

Figure 1.

Side view diagram of the N-face (a) and Ga-face (b) GaN in the presence of oxygen atoms.

Figure 1.

Side view diagram of the N-face (a) and Ga-face (b) GaN in the presence of oxygen atoms.

2. Materials and Methods

A GaN-based PIN diode heterostructure was grown on a 6-inch silicon substrate using metal-organic chemical vapor deposition (MOCVD). The GaN epitaxy started with the growth of a thick buffer layer, followed by an 800 nm n+ doped GaN layer with a Si-doping concentration of 5×1018 cm-3. Subsequently, a 3.5 µm n- doped GaN drift layer was grown with a Si-doping concentration of 3×1016 cm-3 corresponding to a net doping of 9×1015 cm-3 considering the residual carbon concentration. The growth was completed with a p-type GaN layer on top, doped with 2×1019 cm-3 of Magnesium (Mg), resulting in a hole concentration of 3×1017 cm-3 as assessed by Hall effect measurements.

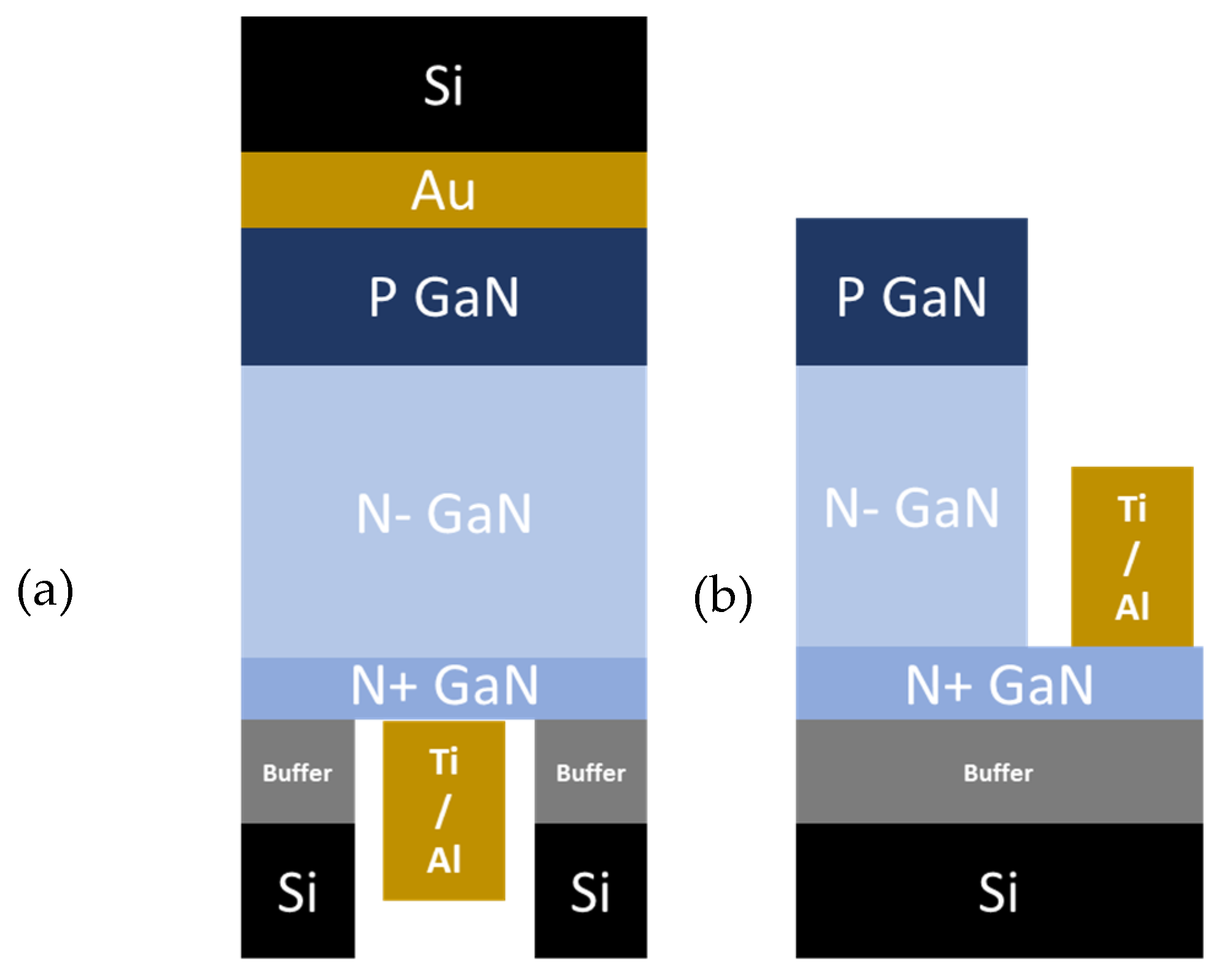

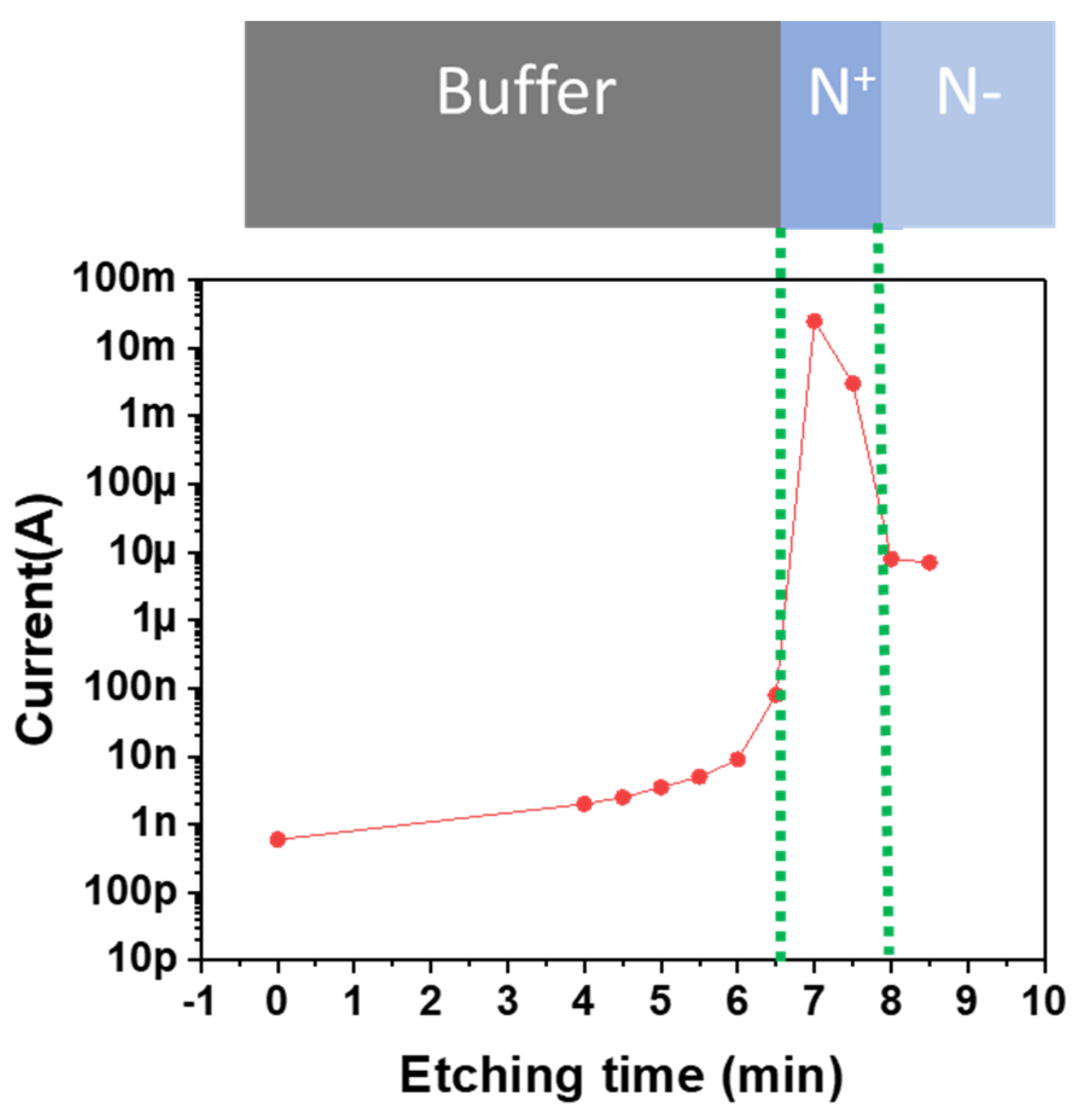

To avoid robustness issues of the membranes, the vertical GaN fabrication process started with the bonding of the front side on a silicon substrate by thermal compression of gold at 300°C (Figure 2a). The metal used for bonding was Ti (100 nm)/Au (200 nm), deposited by evaporation on both the silicon substrate and the PIN diode frontside. The backside process began with thinning the Si substrate from 1 mm down to 150 µm, followed by the deposition and patterning of a thick resist layer using standard lithography. This resist layer served as a mask during the local removal of Si using deep reactive-ion etching. The buffer layer was subsequently removed using a Cl2 ICP (inductively coupled plasma)-based recipe. Due to the membrane's critical etching depth, etching control is not trivial. Therefore, etching time was calibrated by monitoring the electrical conductivity. Direct I(V) measurements on the surface (without metals) at 30V resulted in the following current level for each layer: nA range for the buffer layers, mA range for the n+ layer, and µA range for the n- layer (Figure 3).

Figure 1.

Schematic overview of the studied samples to characterized the ohmic contacts on N-face GaN layer, samples B-D (a) and Ga-face GaN layer, sample A.

Figure 1.

Schematic overview of the studied samples to characterized the ohmic contacts on N-face GaN layer, samples B-D (a) and Ga-face GaN layer, sample A.

Figure 3.

current versus etching time curves to control the etch depth.

Figure 3.

current versus etching time curves to control the etch depth.

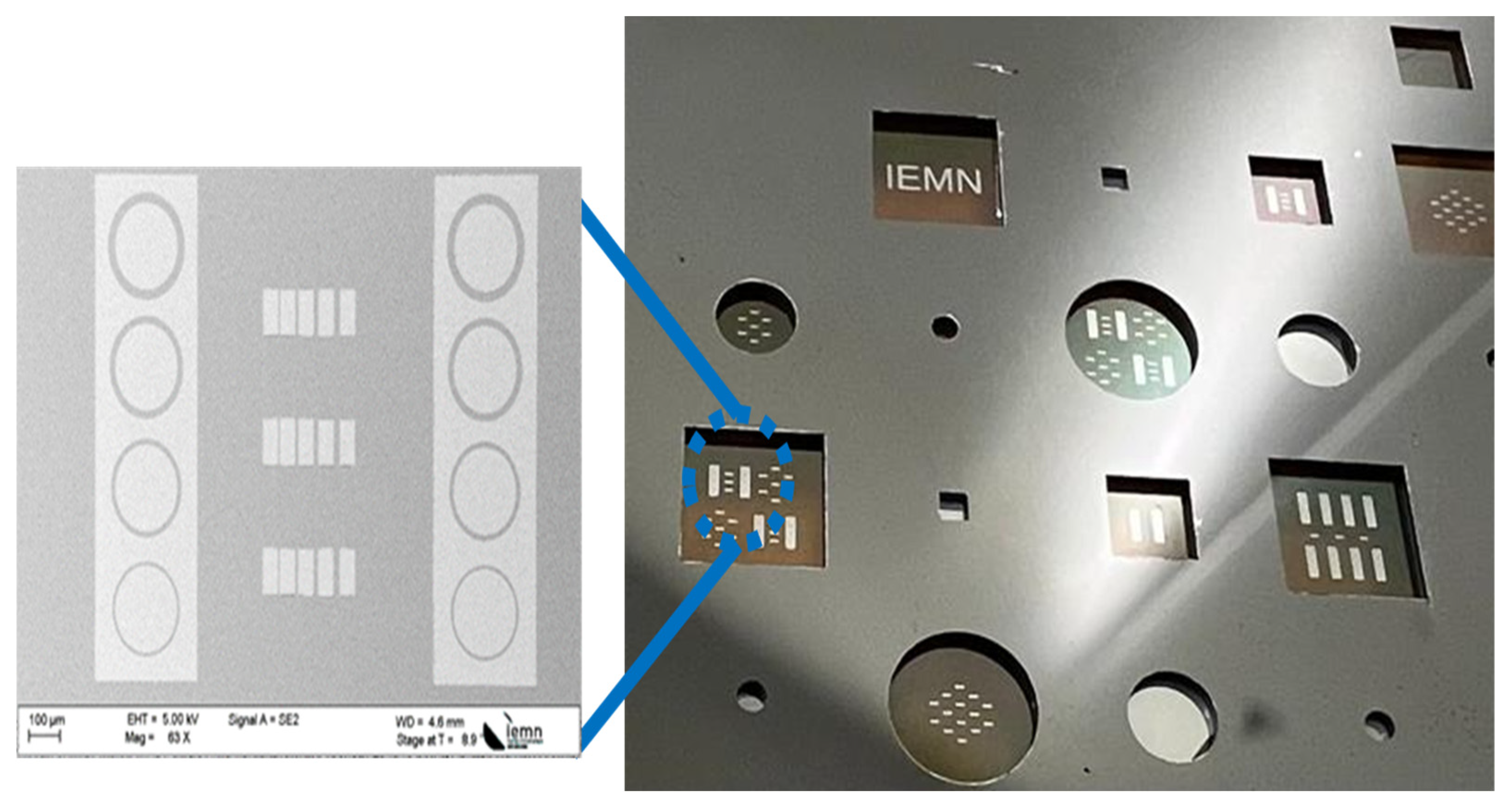

Standard photolithography based on hard mask to pattern the TLM through the resist was not feasible due to the large gap between the GaN membrane surface and the optical exposure level. Therefore, direct laser writing was applied to achieve the TLM patterns. The vertical device processing concluded with the deposition of a Ti (25 nm)/Al (100 nm) contact layer using evaporation and subsequent lift-off on the backside (Figure 4). The aforementioned recipe was used to generate several samples from the same wafer avoiding any epi-variation. The various samples were used to define a design of experiment prior to the deposition of the contact layer as follows:

Control samples B1 and B2 were metallized without any treatment, with a delay of 10 minutes and 24 hours after buffer etching, respectively.

To investigate the time dependence, samples C1, C2, C3, and C4 were treated with HCl (37%) at 70°C for 1 min, 2 min, 3 min, and 5 min prior to metallization, respectively.

To investigate the temperature dependence, samples D1, D2, and D3 were treated with HCl (37%) for 1 minute at room temperature, 55°C, and 70°C prior to metallization, respectively.

An additional sample, referred to as sample A, was prepared with a pseudo-vertical structure. This configuration involved contacting the n+ layer from the front side on the Ga-face after ICP mesa etching (Figure 2b) to compare the Ti/Al ohmic contact quality with the N-face from the same GaN layer.

Transmission line measurements (TLMs) were performed to assess the electrical quality of the ohmic contacts in all cases. In addition to electrical characterization, the samples were also structurally characterized using XPS and SEM. XPS analysis have been performed right after the HCl treatment using a Sigma Probe instrument of Thermo Fisher Scientific Inc. with a base pressure of approximately 10

-9 mbar. A monochromatic Al Kα X-ray source is used as the excitation source. The spectra are calibrated by setting the N-Ga component in the N1s spectra to 397.7 eV [

21,

22,

23,

24]. Next, the O-Ga to Ga ratio in the Ga3d spectra is determined by fitting the spectra using CasaXPS (Casa Software Ltd.). The error on the atomic concentrations obtained via CasaXPS is typically estimated to be roughly 10% of the reported value. After XPS, SEM images are obtained from the samples using an FEI Quanta 200F instrument. Cross-sectional images are obtained after cleaving the samples.

Figure 4.

SEM and optical images of vertical GaN membranes with TLM patterns after metallization and lift-off.

Figure 4.

SEM and optical images of vertical GaN membranes with TLM patterns after metallization and lift-off.

3. Results

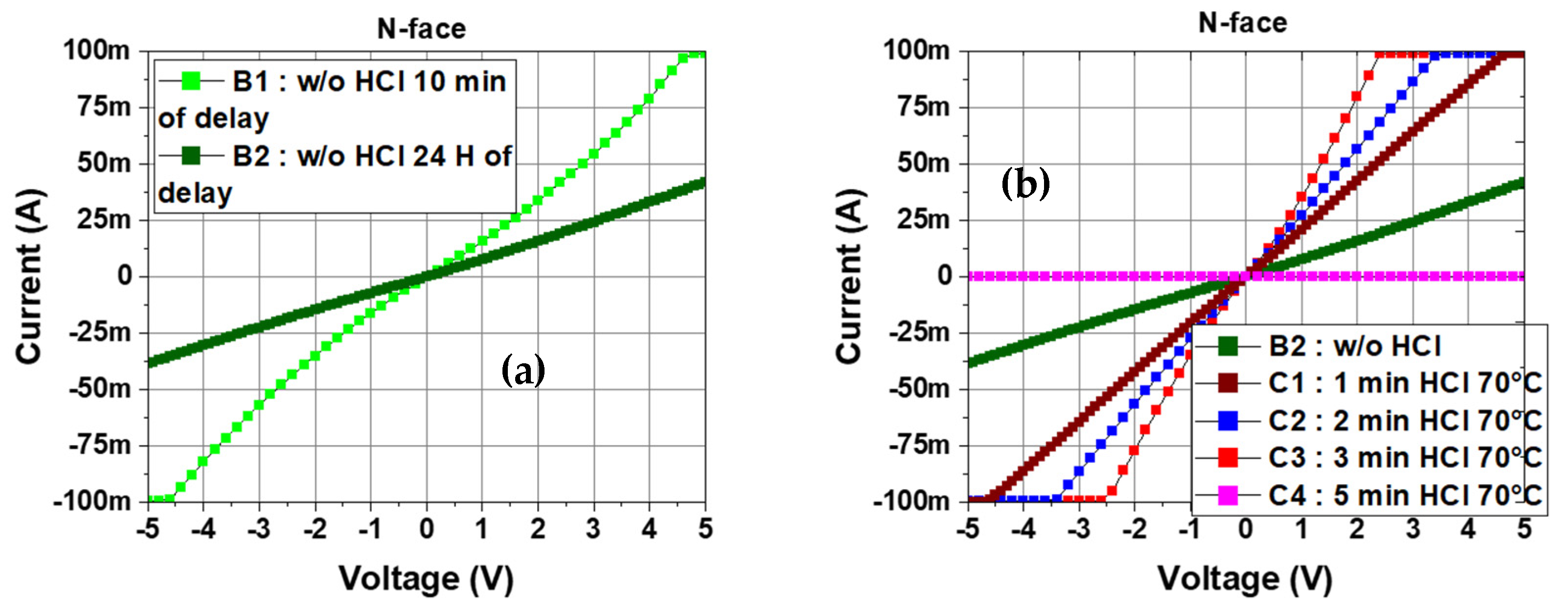

Figure 5a shows TLM measurements on the N-face for a 10-minute delay between the buffer etching and the deposition of metal (sample B1). The IV characteristics reveal a poor linear behaviour although a rather high current of 100 mA at 4.5 V is observed resulting in 2.4×10

-4 Ω.cm² contact resistances. When increasing the delay to 24 hours (sample B2), the measured current drops to 40 mA at 5 V due to much higher contact resistances >10

-3 Ω.cm². These results suggest that an oxidation phenomenon occurs during the delay time. An HCl (37%)-based wet treatment was developed with a temperature initially fixed at 70°C in agreement with reported results in [

25] demonstrating the need of high temperature to efficiently remove the native oxide.

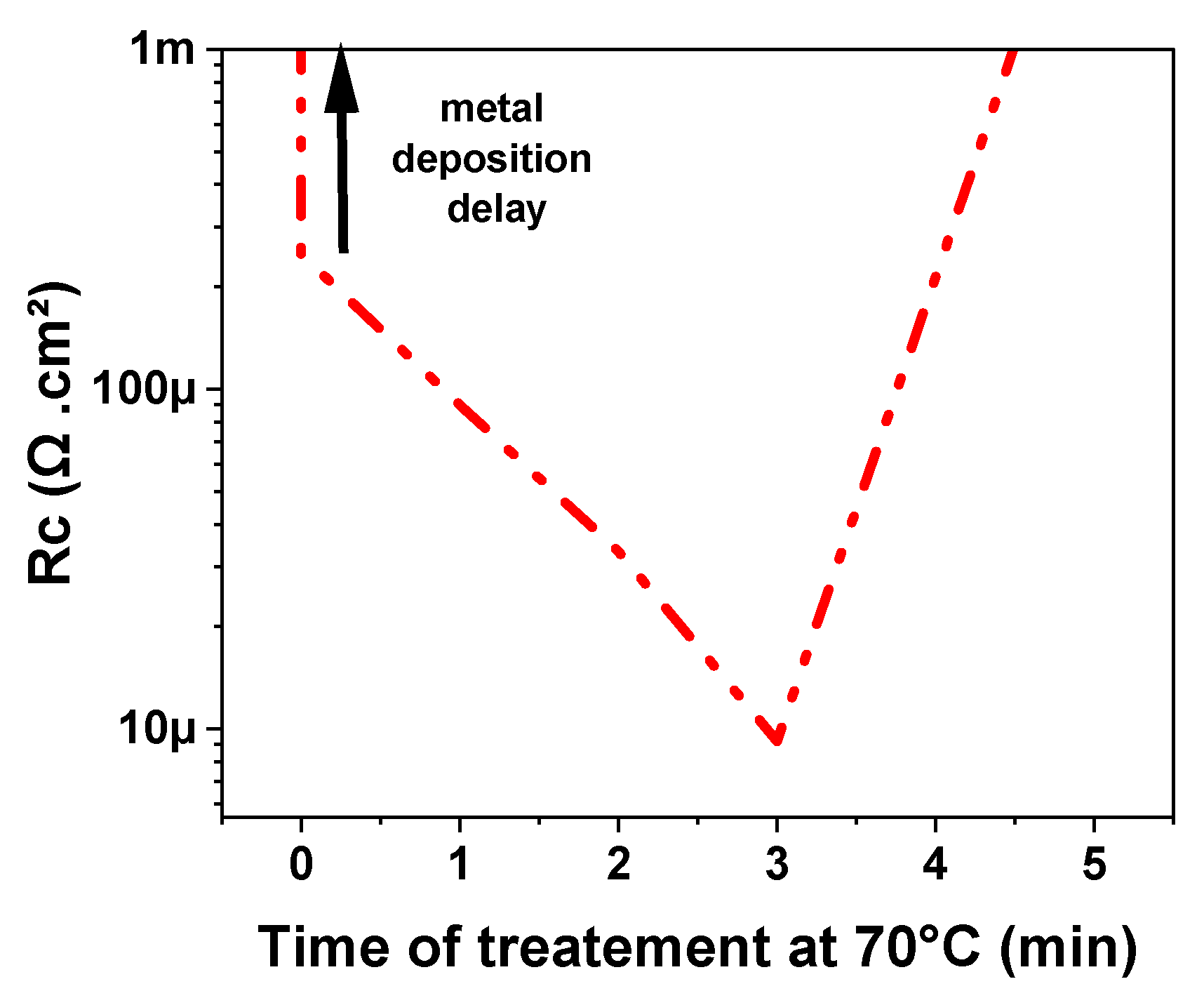

Figure 5b shows the time dependence of the HCl wet treatment at 70°C on the ohmic contact resistance. Up to 3 min time duration (samples C1, C2, and C3), the HCl treatment reduces significantly the contact resistance down to 9×10-6 Ω.cm² without additional annealing (see Figure 6), making this approach fully compatible with any frontside post-process. On the other hand, when further increasing the treatment time up to 5 min and above (sample C4), the quality of the ohmic contacts severely deteriorates, and the extracted current drops dramatically, indicating a surface degradation due to prolonged treatment.

Figure 5.

(a) TLM measurements of the N-face ohmic contact without treatment after various time duration between buffer etching and metal deposition. (b) N-face TLM measurements comparison of different HCl treatment time (0-5 min) at 70°C.

Figure 5.

(a) TLM measurements of the N-face ohmic contact without treatment after various time duration between buffer etching and metal deposition. (b) N-face TLM measurements comparison of different HCl treatment time (0-5 min) at 70°C.

Figure 6.

Rc versus time of treatment at 70°C.

Figure 6.

Rc versus time of treatment at 70°C.

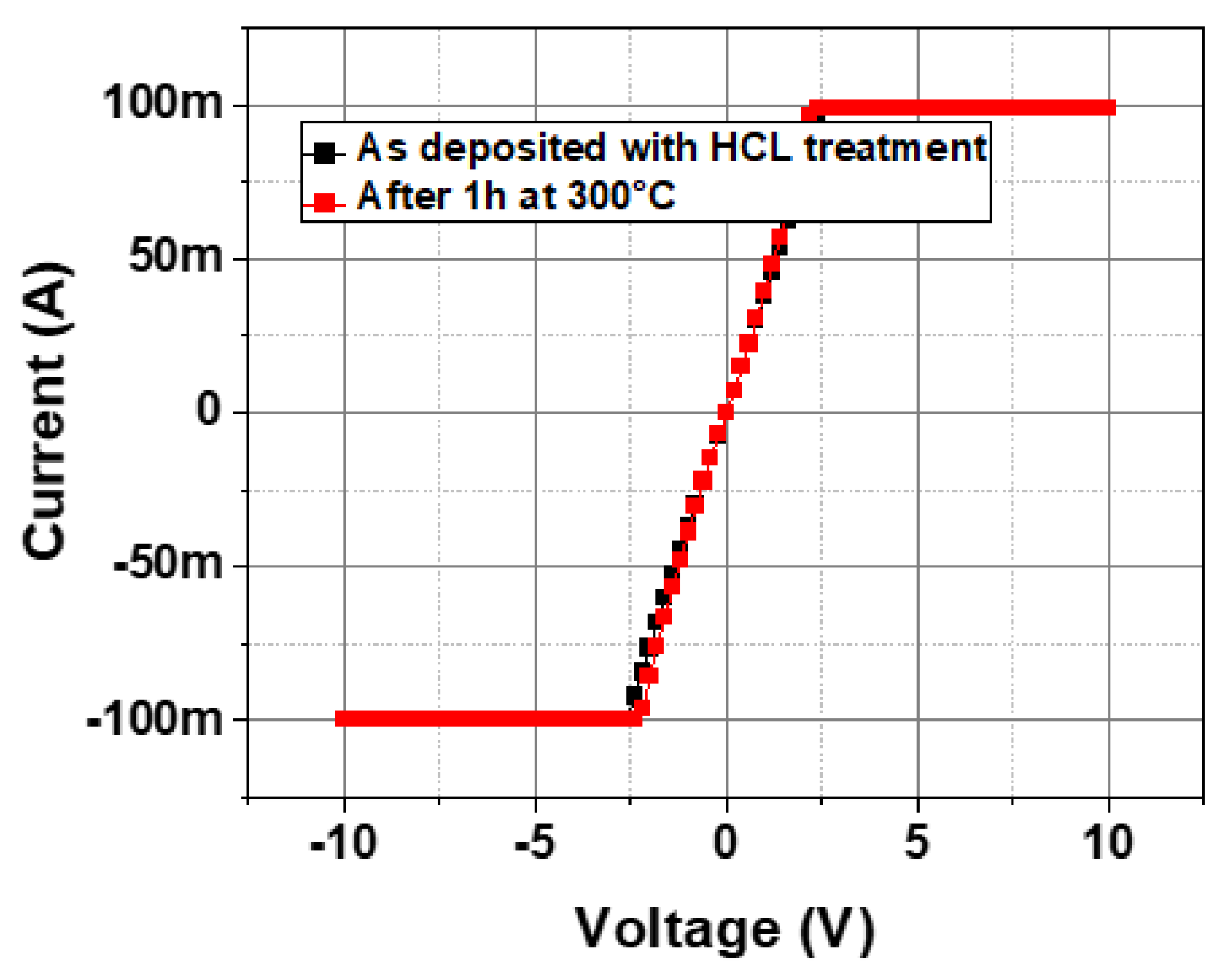

An additional test was performed in order to get some initial insights about the thermal stability of the ohmic contacts. Sample C3 (using the optimum conditions of 3 min HCl treatment at 70 °C) has been introduced in an oven in rich N2 environment at 300 °C for 1 h. Figure 7 shows the electrical current-voltage TLM measurements before and after 1 h thermal stress at 300 °C. The identical IV curves clearly indicate that the ohmic contacts are stable with no short-term impact of the temperature on the applied wet pretreatment.

Figure 7.

TLM measurements of the N-face ohmic contact with HCl pretreatment before and after thermal stress during 1 h at 300°C.

Figure 7.

TLM measurements of the N-face ohmic contact with HCl pretreatment before and after thermal stress during 1 h at 300°C.

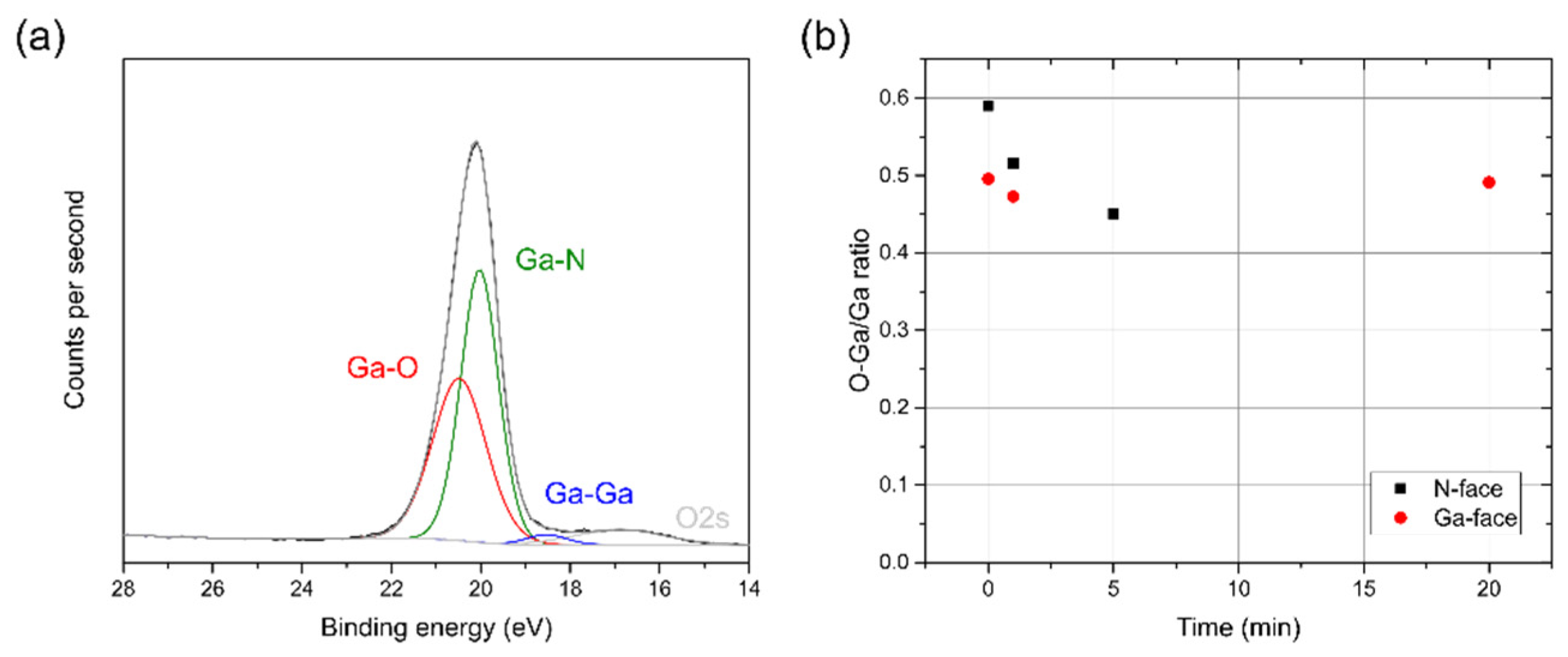

To observe the chemical modification of the GaN surface with the HCl treatment, various N-face and Ga-face samples have been treated with HCl at 70 °C for time duration ranging between 1-20min and immediately measured by XPS. The oxidation state of the surface can be determined by deconvoluting the Ga3d spectra into three peaks: Ga-N, Ga-O and Ga-Ga at a binding energy of 20.0-20.1eV, 20.5-21.0eV and 18.5-19.1eV, respectively.[

21,

22,

24] As an example, the deconvolution of the Ga3d spectrum of the 5 min HCl treated N-face sample can be found in Figure 8a. Using these fits, the O-Ga to Ga ratio is then calculated and plotted as a function of HCl treatment time at 70 °C in Figure 8b. The data shows that the untreated N-face is oxidized to a greater extent than the untreated Ga-face. In addition, the HCl treatment is observed to reduce the N-face upon treatment time, while even after a treatment time of 20 min, the Ga-face remains roughly unaffected. These findings correspond well to the electrical results, showing no impact of the HCl treatment for the Ga-face, while an initial increase in contact quality is found upon removal of the Ga-O surface species for the N-face. The latter is also in agreement with literature, reporting that the removal of native oxide from the GaN surface is crucial to obtain low resistance ohmic contacts [

18,

26].

Figure 8.

(a) Ga3d spectra of the 5min HCl-treated N-face sample demonstrating how the spectra is fitted. (b) O-Ga/Ga ratio in the Ga3d spectra as measured by XPS as a function of HCl treatment time at 70 °C for N-face (squares) and Ga-face (circles).

Figure 8.

(a) Ga3d spectra of the 5min HCl-treated N-face sample demonstrating how the spectra is fitted. (b) O-Ga/Ga ratio in the Ga3d spectra as measured by XPS as a function of HCl treatment time at 70 °C for N-face (squares) and Ga-face (circles).

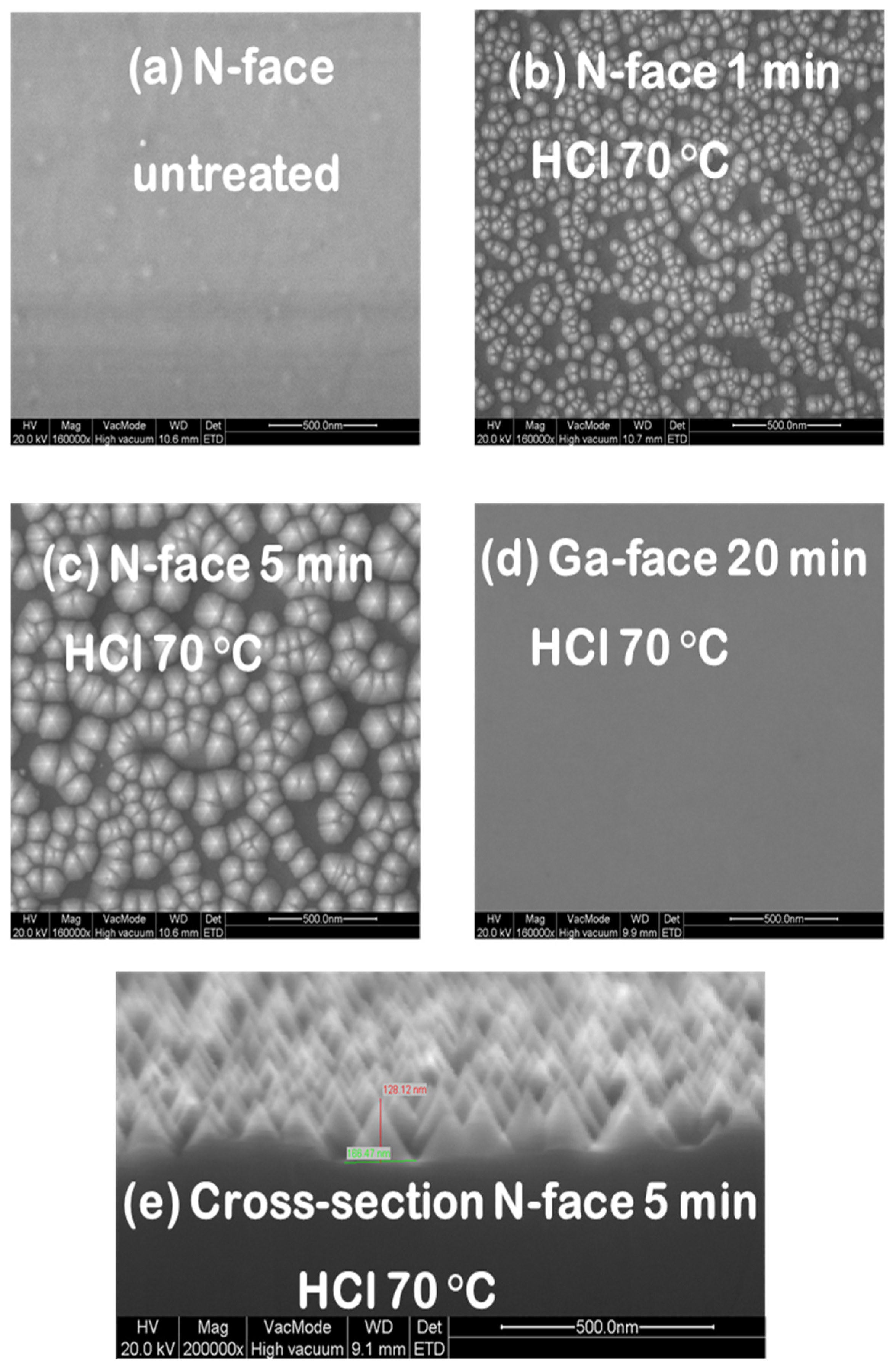

SEM images display that the HCl treatment not only reduces the N-face, but can also be associated with the formation of hexagonal pyramid-shaped features at the surface, as displayed in Figure 9. While the Ga-face again remains unaffected even after 20 min HCl treatment at 70 °C (Figure 9d), the features are observed to enlarge upon treatment time for the N-face (Figure 9a-c). After 5 min HCl treatment, the height and width of the features is estimated to be approximately 128 nm and 166 nm, respectively (Figure 9e). Similarly, [

27] report the formation of sixfold nanopyramids on N-face GaN after etching for 45 min in 2 M KOH at 90 °C whereas the Ga-face is observed to remain smooth. Their observations demonstrate that the hexagonal pyramid shape is originating from preferential etching of crystal-line planes. Also in [

28,

29] report the formation of pyramid shapes which are observed to increase upon time after etching in heated KOH or H3PO4 solutions.

Figure 9.

SEM images of the HCl treated GaN surfaces.

Figure 9.

SEM images of the HCl treated GaN surfaces.

The formation of these features is accompanied by an increase in roughness of the surface. Hypothetically, this increase in roughness might explain why the 5 min HCl treated sample behaves poor in comparison to the 3 min HCl treated sample as observed by TLM. This would suggest that an optimal HCl treatment time exists on N-face GaN, showing the perfect trade-off between native oxide removal and surface roughness increase to obtain the lowest contact resistances.

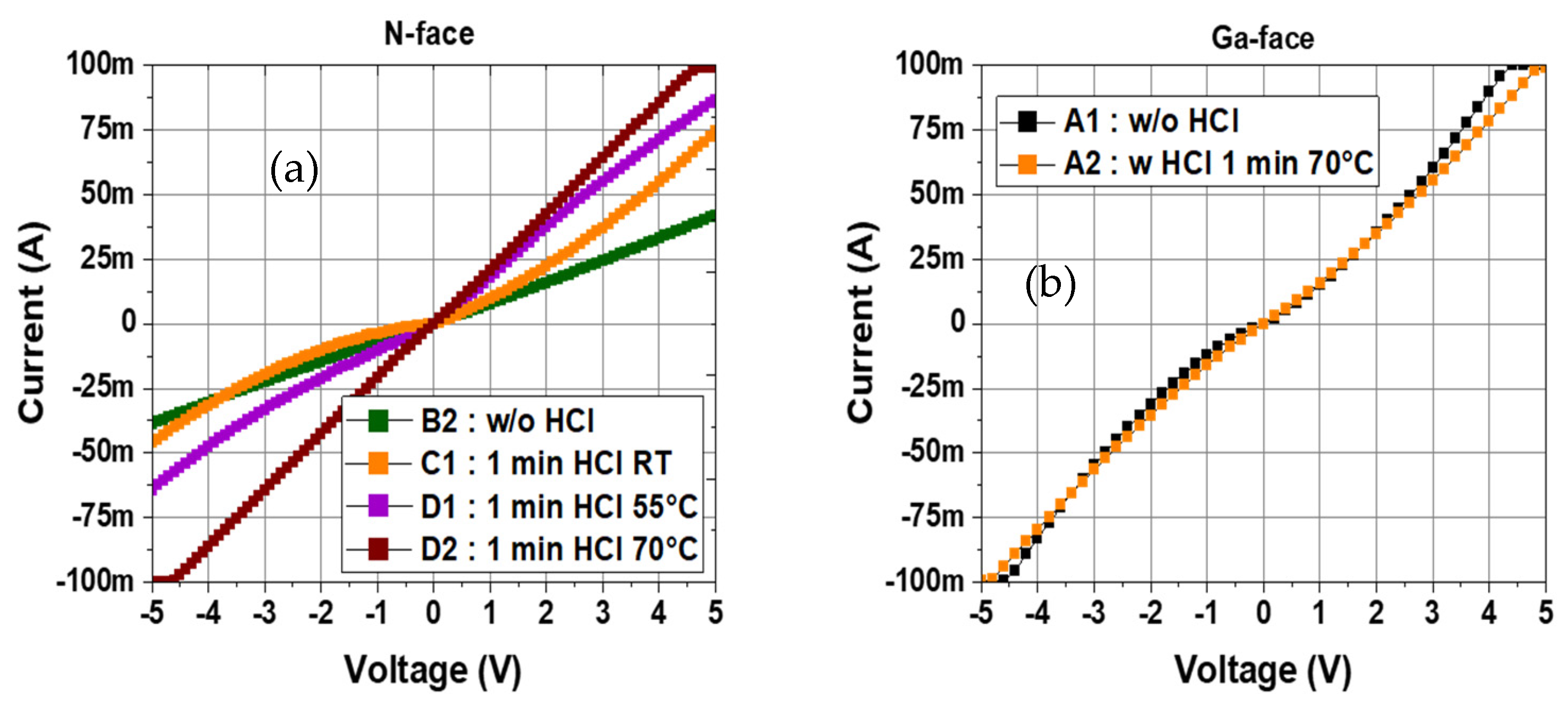

Figure 10a compares TLM measurements of different samples treated with HCl for 1 minute at various temperatures to study the impact of treatment temperature on the ohmic contact quality. Sample B2 is the control sample without any treatment. It can be observed that room temperature (RT) treatment (sample D1) improves the TLM characteristics with a higher current. This is also the case for the 55°C treatment (sample D2) delivers still high contact resistances >10-3 Ω.cm2. The most effective treatment temperature was found to be at 70°C (sample C1), resulting in a significantly improved current level with an associated contact resistance of 7-8 10-5 Ω.cm². It is important to note that additional samples were treated with longer treatment times at RT and 55°C, but the ohmic contact resistances never reached the ones achieved at 70°C.

For a fair benchmark, contact resistances on Ga-face n+ GaN layer were measured with (sample A1) and without HCl treatment at 70°C (sample A2) (Figure 10b). Despite the absence of pretreatment, Ga-face contact resistances are comparable to the N-face in sample B1 without delay between buffer etching and metallization. Furthermore, no impact of HCl wet treatment at 70°C was observed on Ga-face ohmic contacts that generally require extra annealing to further reduce the contact resistances. These results confirm that the properties of N-face are significantly different from those of Ga-face GaN layer, suggesting that the native oxide of N-face GaN layer is the major factor influencing the ohmic contact quality but can be mitigated using a proper wet pretreatment without any annealing.

Figure 8.

(a) N-face TLM measurements for samples treated with HCl treatment at different temperature (RT, 55°C, and 70°C) (b) Ga-face TLM measurements comparison with and without HCL treatment.

Figure 8.

(a) N-face TLM measurements for samples treated with HCl treatment at different temperature (RT, 55°C, and 70°C) (b) Ga-face TLM measurements comparison with and without HCL treatment.

5. Conclusions

In this work, N-face backside ohmic contacts in fully vertical GaN-on-Silicon PIN diodes are assessed. Direct laser writing lithography enabled to pattern TLMs inside the membrane, as standard photolithography could not be used in this frame. TLM measurements from as deposited metal stack showed high contact resistances, which degrades over time between membrane opening and metal deposition. This suggests a gradual oxidation of the N-face GaN. Therefore, an HCl treatment was developed and found to be effective in reducing contact resistances and improving the maximum current. The optimum HCl treatment was found to be 3 minutes at 70°C while the contacts were severely degraded for longer time. It can be pointed out that short-term thermal stability up to 300°C shows no degradation of the optimized ohmic contacts. XPS analysis revealed a clear reduction in Ga-oxide with the HCl treatment. Moreover, SEM images showed the formation of pyramids, especially for prolonged HCl treatment explaining the ohmic contact drastic degradation for longer time. Finally, it has also been shown that the treatment temperature of 70°C is critical as much lower improvement occurs when reducing the temperature. This simple approach can be used for fabricating any types of fully vertical GaN-on-silicon devices as no extra annealing is required to achieve negligible backside contact resistances and thus fully compatible with frontside processing.

Funding

This project has received funding from the ECSEL Joint Undertaking (JU) under grant agreement No 101007229. The JU receives support from the European Union’s Horizon 2020 research & innovation programme and Germany, France, Belgium, Austria, Sweden, Spain, Italy. This work was also supported by the French RENATECH Network.

References

- Abid, I.; Canato, E.; Meneghini, M.; Meneghesso, G.; Cheng, K.; Medjdoub, F. GaN-on-Silicon Transistors with Reduced Current Collapse and Improved Blocking Voltage by Means of Local Substrate Removal. Appl. Phys. Express 2021, 14, 036501. [Google Scholar] [CrossRef]

- Mishra, U.K.; Parikh, P. ; Yi-Feng Wu AlGaN/GaN HEMTs-an Overview of Device Operation and Applications. Proc. IEEE 2002, 90, 1022–1031. [Google Scholar] [CrossRef]

- Hamdaoui, Y.; Abid, I.; Michler, S.; Ziouche, K.; Medjdoub, F. Demonstration of Avalanche Capability in 800 V Vertical GaN-on-Silicon Diodes. Appl. Phys. Express 2023, 17, 016503. [Google Scholar] [CrossRef]

- Brusaterra, E.; Bahat Treidel, E.; Brunner, F.; Wolf, M.; Thies, A.; Würfl, J.; Hilt, O. Optimization of Vertical GaN Drift Region Layers for Avalanche and Punch-Through Pn-Diodes. IEEE Electron Device Lett. 2023, 44, 388–391. [Google Scholar] [CrossRef]

- Abdul Khadar, R.; Liu, C.; Zhang, L.; Xiang, P.; Cheng, K.; Matioli, E. 820-V GaN-on-Si Quasi-Vertical p-i-n Diodes With BFOM of 2. 0 GW/Cm2. IEEE Electron Device Lett. 2018, 39, 401–404. [Google Scholar] [CrossRef]

- Guo, X.; Zhong, Y.; Zhou, Y.; Chen, X.; Yan, S.; Liu, J.; Sun, X.; Sun, Q.; Yang, H. 1200-V GaN-on-Si Quasi-Vertical p-n Diodes. IEEE Electron Device Lett. 2022, 43, 2057–2060. [Google Scholar] [CrossRef]

- Jia, F.; Ma, X.; Yang, L.; Zhang, X.; Hou, B.; Zhang, M.; Wu, M.; Niu, X.; Du, J.; Liu, S.; et al. 930V and Low-Leakage Current GaN-on-Si Quasi-Vertical PiN Diode With Beveled-Sidewall Treated by Self-Aligned Fluorine Plasma. IEEE Electron Device Lett. 2022, 43, 1400–1403. [Google Scholar] [CrossRef]

- Harrison, S.E.; Shao, Q.; Frye, C.D.; Voss, L.F.; Nikolic, R.J. 1.1 kV Vertical p-i-n GaN-on-Sapphire Diodes. In Proceedings of the 2018 76th Device Research Conference (DRC); IEEE: Santa Barbara, CA, June 2018; pp. 1–2.

- Aktas, O.; Kizilyalli, I.C. Avalanche Capability of Vertical GaN P-n Junctions on Bulk GaN Substrates. IEEE Electron Device Lett. 2015, 36, 890–892. [Google Scholar] [CrossRef]

- Fu, K.; He, Z.; Yang, C.; Zhou, J.; Fu, H.; Zhao, Y. GaN-on-GaN p-i-n Diodes with Avalanche Capability Enabled by Eliminating Surface Leakage with Hydrogen Plasma Treatment. Applied Physics Letters 2022, 121, 092103. [Google Scholar] [CrossRef]

- Zhang, Y.; Dadgar, A.; Palacios, T. Gallium Nitride Vertical Power Devices on Foreign Substrates: A Review and Outlook. J. Phys. D: Appl. Phys. 2018, 51, 273001. [Google Scholar] [CrossRef]

- Hamdaoui, Y.; Abid, I.; Ziouche, K.; Medjdoub, F. Local Substrate Removal for next Generation GaN-on-Silicon Power Transistors.

- Zhang, Y.; Yuan, M.; Chowdhury, N.; Cheng, K.; Palacios, T. 720-V/0 35-m $\Omega \cdot$ Cm 2 Fully Vertical GaN-on-Si Power Diodes by Selective Removal of Si Substrates and Buffer Layers. IEEE Electron Device Lett. 2018, 39, 715–718. [Google Scholar] [CrossRef]

- Chung, R.B.; Chen, H.-T.; Pan, C.-C.; Ha, J.-S.; DenBaars, S.P.; Nakamura, S. The Polarization Field Dependence of Ti/Al Based Ohmic Contacts on N-Type Semipolar GaN. Applied Physics Letters 2012, 100, 091104. [Google Scholar] [CrossRef]

- Jang, T.; Lee, S.N.; Nam, O.H.; Park, Y. Investigation of Pd∕Ti∕Al and Ti∕Al Ohmic Contact Materials on Ga-Face and N-Face Surfaces of n-Type GaN. Applied Physics Letters 2006, 88, 193505. [Google Scholar] [CrossRef]

- Young Moon, S.; Ho Son, J.; Jin Choi, K.; Lee, J.-L.; Jang, H.W. Indium as an Efficient Ohmic Contact to N-Face n -GaN of GaN-Based Vertical Light-Emitting Diodes. Applied Physics Letters 2011, 99, 202106. [Google Scholar] [CrossRef]

- Seo, H.; Cha, Y.-J.; Islam, A.B.M.H.; Kwak, J.S. Improvement of Ti/Al Ohmic Contacts on N-Face n-Type GaN by Using O2 Plasma Treatment. Applied Surface Science 2020, 510, 145180. [Google Scholar] [CrossRef]

- Motayed, A.; Jah, M.; Sharma, A.; Anderson, W.T.; Litton, C.W.; Mohammad, S.N. Two-Step Surface Treatment Technique: Realization of Nonalloyed Low-Resistance Ti/Al/Ti/Au Ohmic Contact to n-GaN. Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures Processing, Measurement, and Phenomena 2004, 22, 663–667. [Google Scholar] [CrossRef]

- Redaelli, L.; Muhin, A.; Einfeldt, S.; Wolter, P.; Weixelbaum, L.; Kneissl, M. Ohmic Contacts on N-Face n-Type GaN After Low Temperature Annealing. IEEE Photon. Technol. Lett. 2013, 25, 1278–1281. [Google Scholar] [CrossRef]

- Zywietz, T.K.; Neugebauer, J.; Scheffler, M. The Adsorption of Oxygen at GaN Surfaces. Applied Physics Letters 1999, 74, 1695–1697. [Google Scholar] [CrossRef]

- Grodzicki, M.; Rousset, J.-G.; Ciechanowicz, P.; Piskorska-Hommel, E.; Hommel, D. XPS Studies on the Role of Arsenic Incorporated into GaN. Vacuum 2019, 167, 73–76. [Google Scholar] [CrossRef]

- Li, D.; Sumiya, M.; Fuke, S.; Yang, D.; Que, D.; Suzuki, Y.; Fukuda, Y. Selective Etching of GaN Polar Surface in Potassium Hydroxide Solution Studied by X-Ray Photoelectron Spectroscopy. Journal of Applied Physics 2001, 90, 4219–4223. [Google Scholar] [CrossRef]

- Prabhakaran, K.; Andersson, T.G.; Nozawa, K. Nature of Native Oxide on GaN Surface and Its Reaction with Al. Applied Physics Letters 1996, 69, 3212–3214. [Google Scholar] [CrossRef]

- Kushvaha, S.S.; Kumar, M.S.; Shukla, A.K.; Yadav, B.S.; Singh, D.K.; Jewariya, M.; Ragam, S.R.; Maurya, K.K. Structural, Optical and Electronic Properties of Homoepitaxial GaN Nanowalls Grown on GaN Template by Laser Molecular Beam Epitaxy. RSC Adv. 2015, 5, 87818–87830. [Google Scholar] [CrossRef]

- Choi, B.S.; Um, J.H.; Eom, H.J.; Jeon, D.-W.; Hwang, S.; Kim, J.K.; Yun, Y.H.; Cho, H. Wet etching of α-Ga2O3 epitaxy film using a HCl-based solution. Journal of the Korean Crystal Growth and Crystal Technology 2022, 32, 40–44. [Google Scholar] [CrossRef]

- Jang, J.-S.; Park, S.-J.; Seong, T.-Y. Effects of Surface Treatment on the Electrical Properties of Ohmic Contacts to (In)GaN for High Performance Optical Devices. phys. stat. sol. (a) 2002, 194, 576–582. [Google Scholar] [CrossRef]

- Ng, H.M.; Weimann, N.G.; Chowdhury, A. GaN Nanotip Pyramids Formed by Anisotropic Etching. Journal of Applied Physics 2003, 94, 650–653. [Google Scholar] [CrossRef]

- Jung, Y.; Ahn, J.; Baik, K.H.; Kim, D.; Pearton, S.J.; Ren, F.; Kim, J. Chemical Etch Characteristics of N-Face and Ga-Face GaN by Phosphoric Acid and Potassium Hydroxide Solutions. J. Electrochem. Soc. 2011, 159, H117–H120. [Google Scholar] [CrossRef]

- Han, S.-C.; Kim, J.-K.; Kim, J.Y.; Kim, K.-K.; Tampo, H.; Niki, S.; Lee, J.-M. Formation of Hexagonal Pyramids and Pits on V-/VI-Polar and III-/II-Polar GaN/ZnO Surfaces by Wet Etching. J. Electrochem. Soc. 2010, 157, D60. [Google Scholar] [CrossRef]

|

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).