1. Introduction

With the development of aeronautics and astronautics, location services and scale applications, air to earth and sea technology, high-tech communication, and high precision radar detection, the measuring precision of frequency signals, especially RF signal, is required to be higher [

1,

2,

3]. At present, frequently used frequency detecting technologies are mainly pulse frequency measuring technology, analog interpolation detecting technology, multi-cycle synchronous measuring technology and time vernier detecting technology, etc. The pulse frequency measuring and multi-cycle synchronous measuring technologies exist the counting error with ± 1 word [

4,

5,

6]. Due to the filling frequencies often no more than 10

−9Hz, the frequency detecting’s accuracy is Often no more than 10

−9/s. The produced frequency detecting meter via these methods has the characteristics of simple equipment structure and low developing cost, but its detecting precision is very low. The counting error with ± 1 word still exists in the analog interpolation detecting and time vernier detecting technologies, but it can be down to about 0.0001 by using the interpolator, the detecting precision can also reach the 10

−11/s. The frequency detecting instruments using these two technologies have good accuracy, but the system’s structure and design are the obvious complexity, at the same time, the higher developing costs limit their applications [

7,

8,

9]. The frequency measuring technology by phase coincidence detecting effectively eliminates the counting error with ± 1 word in the frequency detecting, making the frequency detecting precision up to the 10

−10/s, but the phase coincidence points are not unique and random, further improving frequency detecting precision is very difficult.

Considering the above, a precise frequency detecting technology is proposed based on group period synchronization. The technology combines the group period’s change rule and the compared signals’ frequency relations, which not only solves many frequency measuring’s problems for phase coincidence detecting, but also miniaturizes the equipment, narrows the developing costs, and increases the system’s frequency measuring accuracy.

2. Methods

A number of tests indicate that the phase coincidence points between two different frequency signals repeats at the group period intervals, that is, group period synchronization [

10,

11]. A precise frequency measuring can be get by using the change rule [

12,

13].

Suppose that there are two stable signals,

and

, the

and

signals’ period are the

and

, respectively. Then the relationship between the signals

and

is as follows.

In Formula (3),

and

(

) are integers greater than zero, respectively. The

is called the least common multiple period, and the

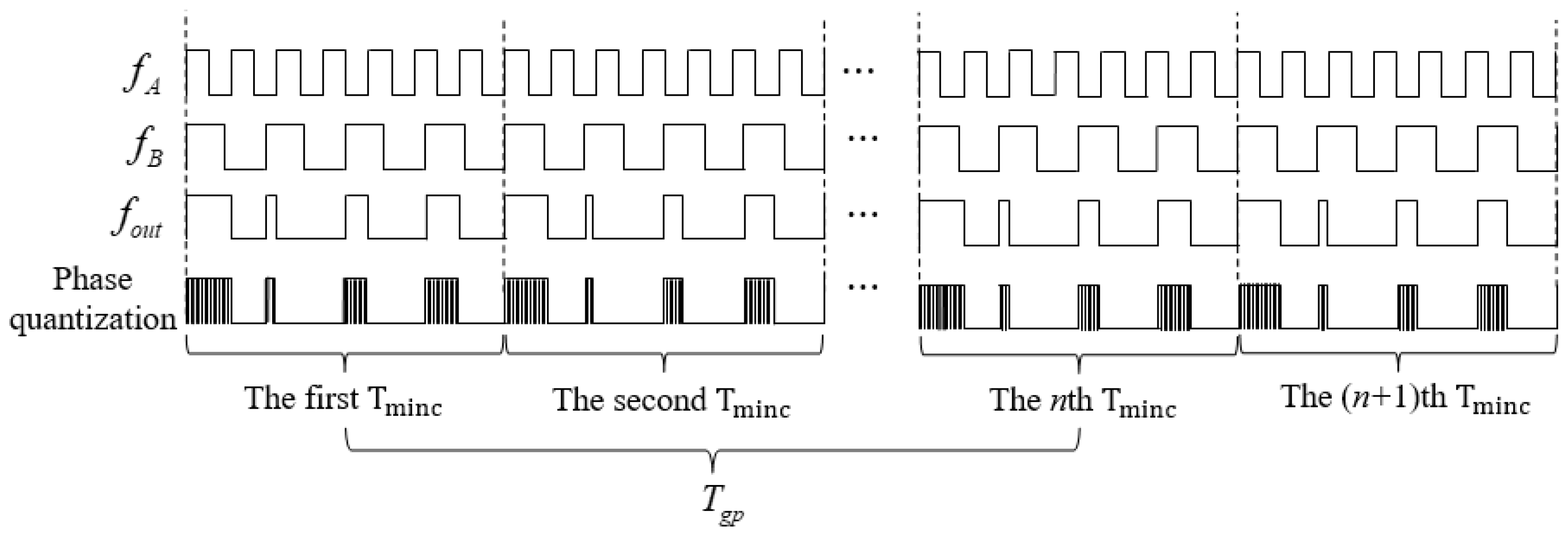

is called the greatest common factor period. As shown in

Figure 1. In

Figure 1, the

and

are the reference and measured signals, the

is the phase coincidence point.

As you can see, in a

,

When the

and

maintain integer multiples, the phase differences in a

are shown in Formula (5).

From the Formula (5) , the , , ... , and are some phase differences in the , and are the numbers for front edge pulses. When the signals and do not maintain integer multiples, let , is the phase shift caused by the frequency deviation between the and . The phase differences in a are described below.

The differences of phases within the 1st

are

The differences of phases within the 2nd

are

The differences of phases within the 3rd

are

The differences of phases within the

are

The differences of phases within the

are

It can be seen from the Formula (6) to the Formula (10) that we can find the regularity of the change of phase differences in the process of phase comparison of different frequencies. In an adjacent

, the value corresponding to the phase difference is equal to

, written as,

. The difference of phase between the 1st

and the

is equal to

in the same position. When

, the phase coincidence points in a

will change periodically. The time interval among the periodic changes is equal to a group period

, written as,

Therefore, the

can be obtained by observing the time interval between the periodic changes of the

, and the

can be calculated by the

.

Thus, the signal

can be calculated by the formula

.

It can be seen from Formula (12) that there is a big error in the actual measurement. When counting the

, the ± 1 word-counting error will cause the actual measuring results to be the

integer multiples. Although the period is small, this kind of error is not allowed. By analyzing the

and the

, the phase differences’ change rule can be get. Whenever two identical phase differences occur in the same time, it is a group period shown in

Figure 1. When

and

are counted in a group period, and the results are

and

, the Formula (14) is obtained, and both sides of the Formula (14) represent integral multiples of the group period.

As can be seen in

Figure 1, the 3rd phase coincidence point in the 1st

is the same as the 3rd phase coincidence point in the

nth

, and this phase coincidence point’s repetition occurs at the same time as a

. The 3rd phase coincidence point’s counting value in the 1st

is recorded and used as the gate’s open signal, and the 3rd phase coincidence point’s counting value in the

nth

occurs as the gate’s close signal. By counting the

and

, respectively, between the open and close signals, the frequency of the

is get by Formula (14).

According to the group period’s change rule, the precise frequency linking among different frequencies signals is get, and the measured signal’s period is detected by the reference signal. Because the inherent regularity between the two signals leads to the same phase coincidence point’s repetition, if the between the and is processed, and then the phase quantization results of the phase coincidence point are detected by a high frequency clock, the phase coincidences information can be get conveniently. The signal , the signal , and the phase coincidence point are counted at the same time, and the phase coincidence point is used to generate the gate, and then the signals and are counted at the same gate time, the measuring error resulted in the counting error can be overcome.

If the phase coincidence point counting has a counting error of ± 1 word with a probability of 50%, the close signal must appear at the period of the integer group period, we only need to multiply an integer coefficient

at both ends of Formula (14) to resolve the effect of the counting error.

Therefore, in frequency measuring, even if the phase coincidence point’s counting error is ± 1 word, it will not affect the frequency measuring’s results. But the counting error with ± 1 word in phase coincidence point counting will lead to the gate time prolonged and the measuring speed slowing down.

3. Discussion

According to frequency detecting’s principle by the phase coincidence point, the key to improve the frequency detecting precision lies in the acquisition and measurement of the

. The

are get by the phase comparison between the signals

and

after shaping processing, then the phase coincidence point’s front and back edges are extracted, respectively, and the high frequency clock is counted between the phase coincidence point’s front and back edges, the same counting results are taken as the open and close signals, respectively, and are transmitted to the MCU for data processing and realization.

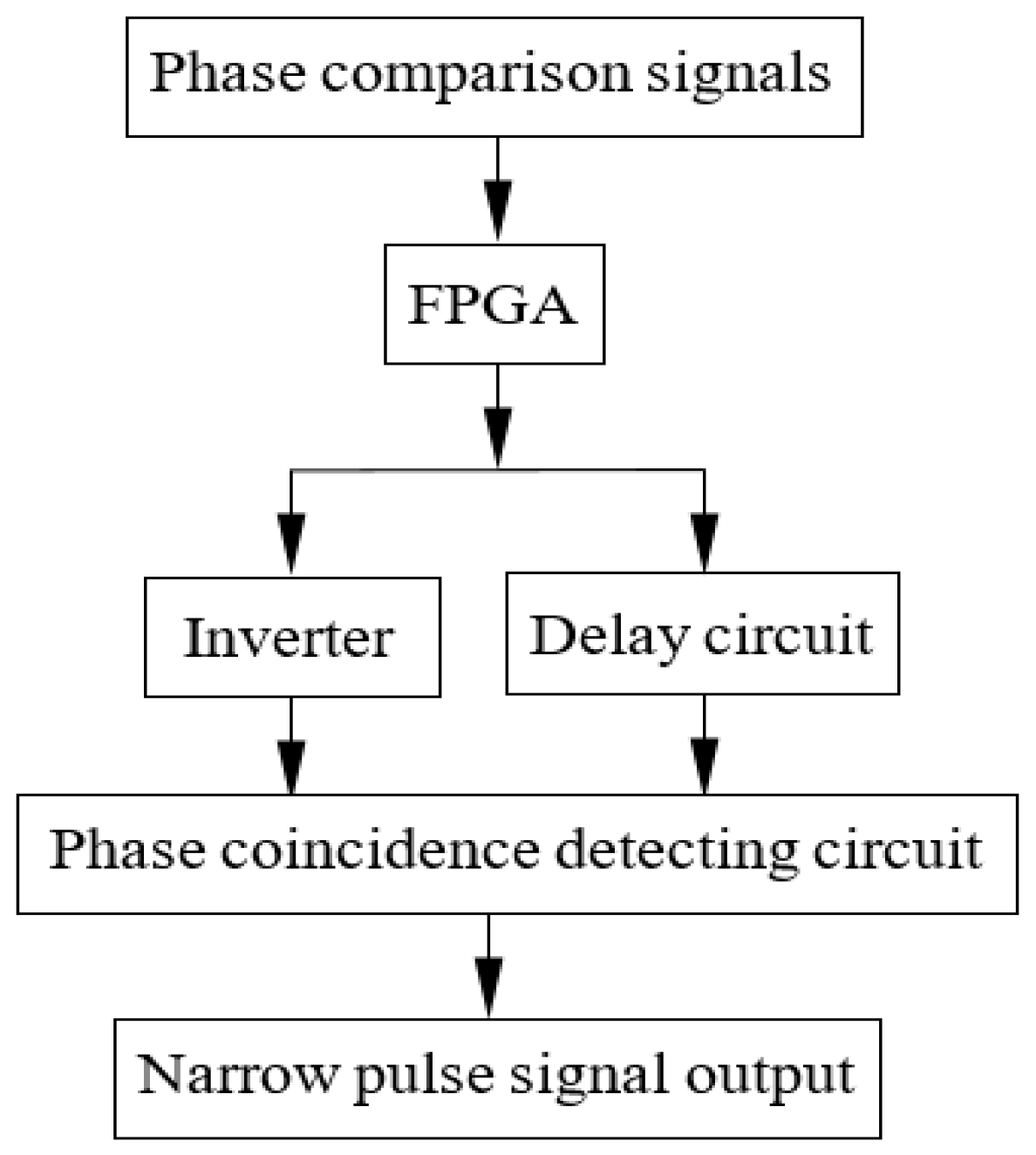

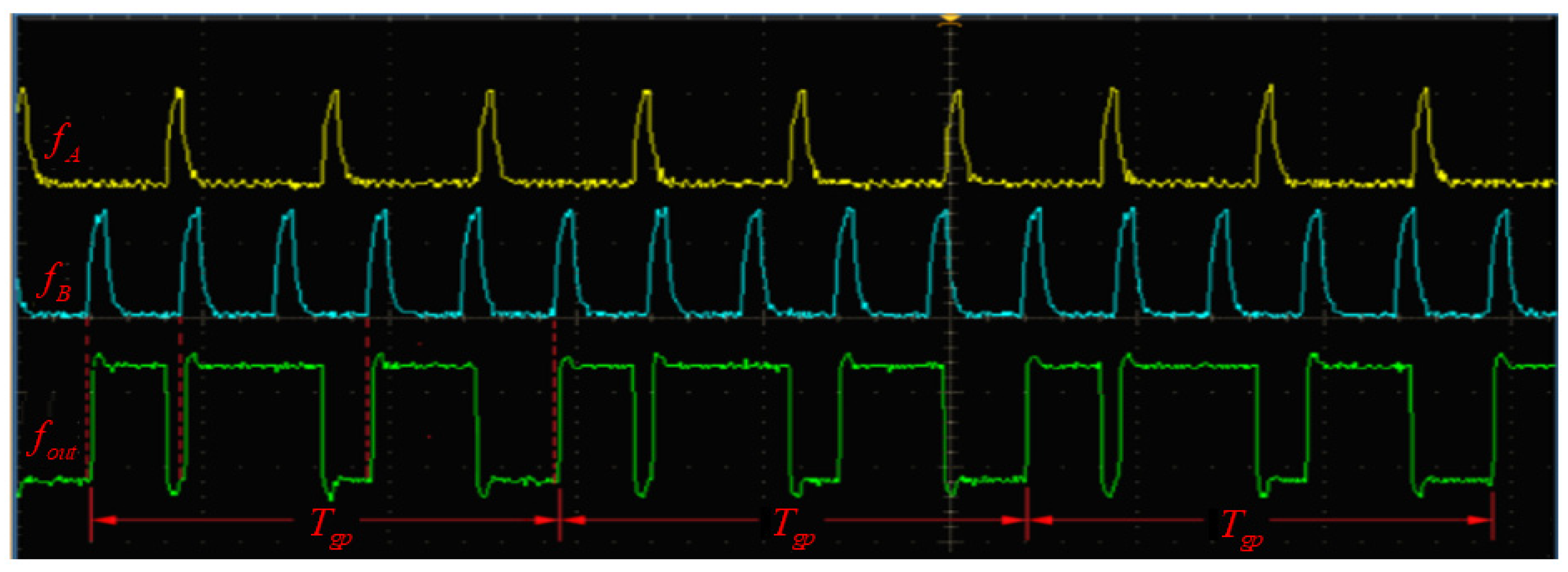

Figure 2 is this system’s frequency detecting design scheme.

The TSG4102A RF signal generator is used to generate the measured signals, the sine wave signals with the 3.3 V amplitude. The reference signal is provided by the BVA8607B-M high stability Crystal oscillator. The measured signal and the reference signal are connected to FPGA through the FPGA chip’s global clock pin, respectively. In this experiment, a 100MHz signal and a 1GHz signal are produced by an internal PLL in FPGA. The 100MHz signal is used to delay the reference and measured signals to produce narrow pulse signals. First, a narrow pulse signal is transmitted to the different frequency phase comparison module to generate a group period consisting. Secondly, a high frequency clock produced by an internal PLL in FPGA is used to quantify and count the . Then, the time when the phase coincidence points are chosen as the counter’s open signal, and the open signal begins to count the pulses. of the and . The same phase coincidence point occurs as the counter’s close signal, and the close signal is used to end the reference and measured signals’ pulses counting. The reference and measured signals’ pulses counting is completed in the gate time. Finally, the reference and measured signals’ pulses counting results are transmitted to the data processing module through the serial port generated by the FPGA instantiation, and the data processing module obtains the measured signal’s frequency measuring result through formula (14).

3.1. Narrow Pulse Extraction

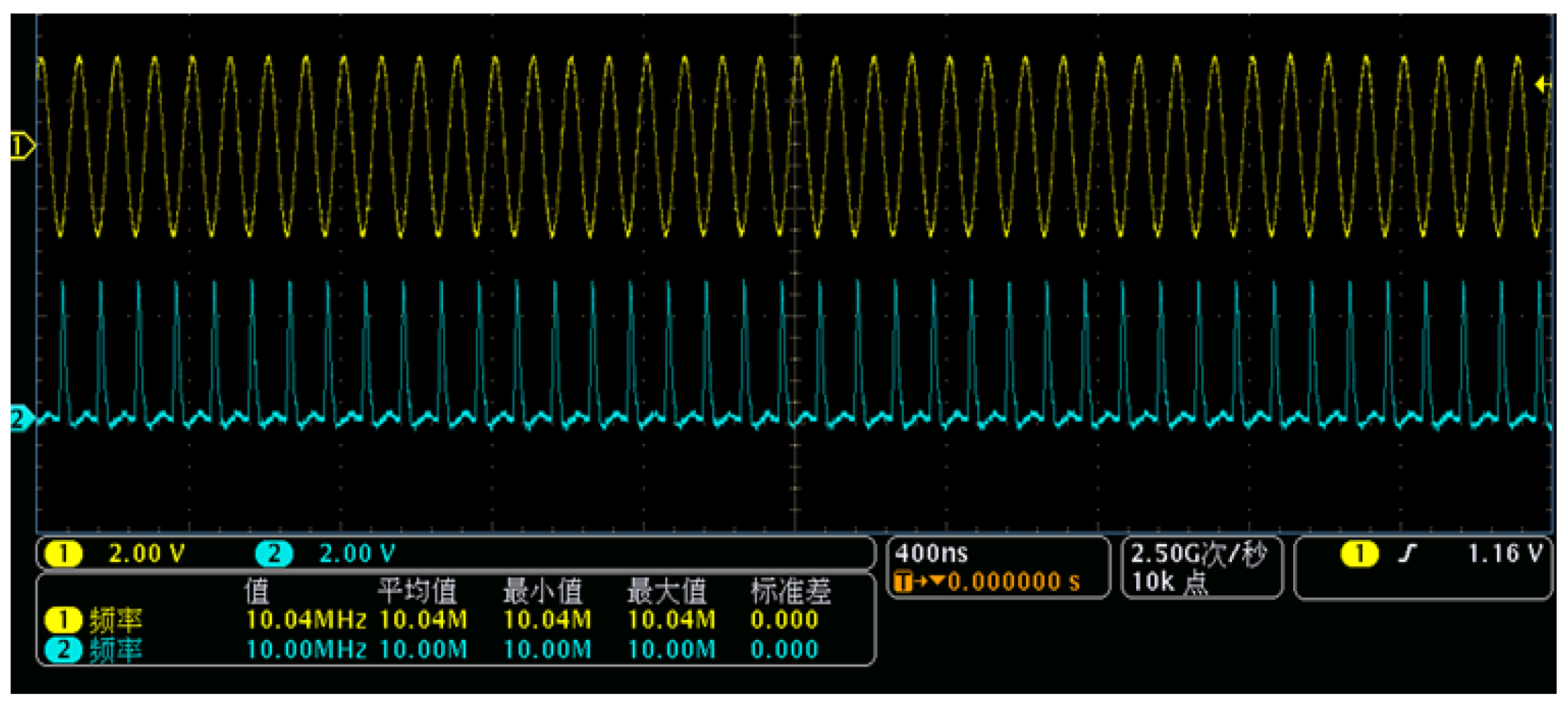

Because FPGA can directly recognize the sine wave that can be converted into a square wave pulse signal in a chip, therefore, two phase comparison signals can be directly transmitted to the clock pin of the FPGA without signal shaping circuit. As shown in

Figure 3.

In

Figure 3, the delay circuit is formed by D flip-flops from the FPGA, and by adjusting the D flip-flop’s clock period, its pulse width is more suitable for the delay width. Besides its own delay effect, the delay circuit can also reduce the comparison signals’ noise. The square wave pulse signal is transmitted to an inverter to get another signal opposite to the original square pulse signal’s phase. The inverse and delayed square wave pulse signals are transmitted to the phase coincidence detecting circuit formed by “AND” logic gate to achieve the narrow pulse signal with the same frequency as the square wave pulse signal. As shown in

Figure 4.

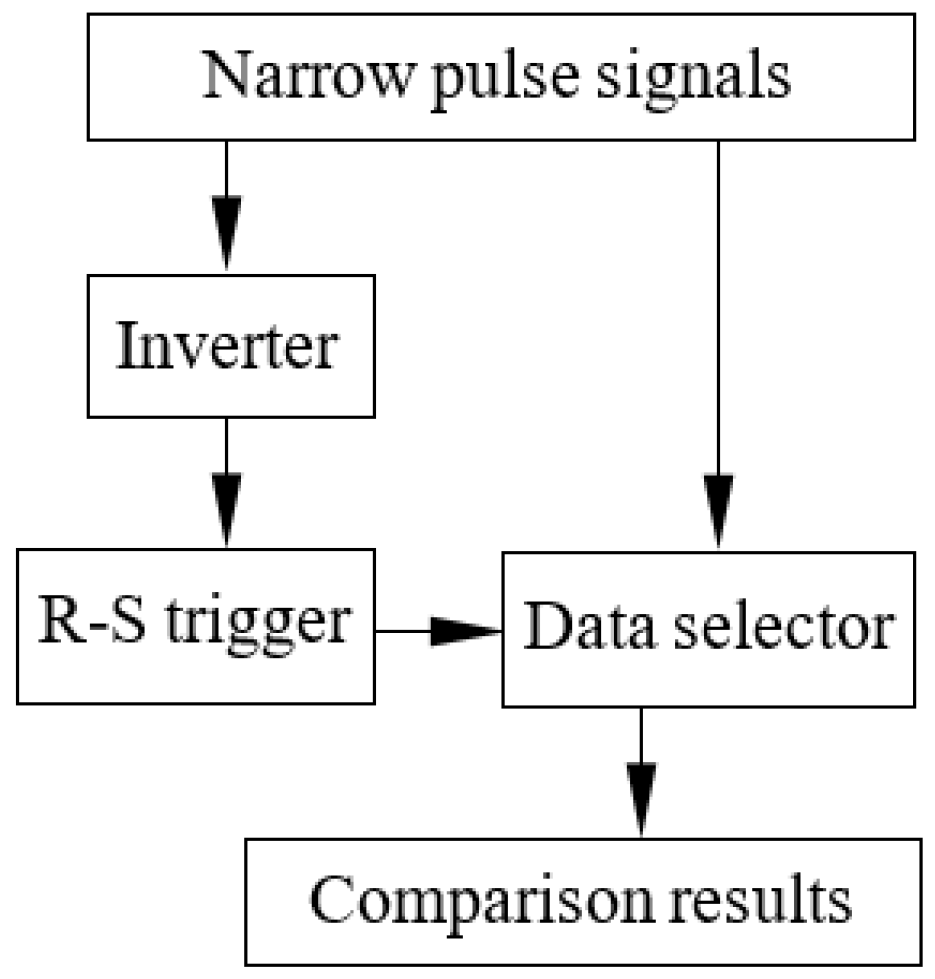

3.2. Different Frequency Phase Comparison

Figure 5 is the different frequency phase comparison scheme.

After pulse extraction, the measured and reference signals are transformed into the same frequency narrow pulse at the same time, which is beneficial to the processing of phase differences and reduces the uncertainty caused by the sine wave signal rising too long, and it makes the phase comparison more stable. If the narrow pulse signals with the same frequency as the reference and measured signals are transmitted to the different frequency phase comparison processing module, the

can be get. As shown in

Figure 6.

3.3. Different Frequency Phase Quantization

After extracting the

in

Figure 6, using a high frequency clock to quantize the phase comparison’s results in FPGA chip to process the

and select the gate signal more conveniently. As shown in

Figure 7.

As can be seen from

Figure 7, each phase coincidence point is quantized during the phase comparison process. The PLL from FPGA provides high-frequency quantizing clock. The quantized phase coincidence points are counted through this high-frequency quantizing clock. The time when the results of two counts are the same is the counter gate.