The functionality of the Ripple Carry Adder (RCA) design using Peres gates was rigorously verified through simulation, encompassing a range of input scenarios. The simulation results confirm the correct operation of the RCA producing accurate sum bits (S[n:0]) and carry out (Cout_n) for different input combinations. The results confirm the adherence to reversible logic principles and the preservation of information throughout the addition process. The simulation results demonstrate that the sum bits (S[n:0]) produced by the RCA accurately reflect the binary addition of the input numbers (A and B) and the carry in (Cin). Each Peres gate strategically placed in the circuit performs a reversible XOR operation contributing to the generation of the sum bits.

The carry out (Cout_n) serves as an overflow indicator revealing whether there is a carry beyond the most significant bit. Simulation results affirm that the circuit correctly calculates Cout_n based on the input numbers and carry ins providing crucial information about the completion of the addition operation.

Data Collection

Data collected during the simulations including verified truth table, waveform, timing diagrams and quantum cost metrics were stored and analyzed to draw meaningful insights into the behavior of the RCA using Peres gates. The simulation setup serves as a crucial foundation for the subsequent analysis, providing a detailed understanding of how the proposed reversible circuit performs under different conditions and shedding light on its potential advantages in reversible and quantum computing applications.

The reversibility of the circuit is a fundamental aspect validated during functionality verification.

The Peres gates by design enable the reconstruction of input states from output states. Simulation results confirm that the RCA and multiplier design exhibits reversibility aligning with the principles of reversible logic.

The controlled NOT (CNOT) operation performed by Peres gates was examined through simulation ensuring that the

NOT operation is selectively applied based on the control bits. The controlled nature of the XOR operations ensures that information is not lost during the addition process. The overall functionality verification provides confidence in the correct operation of the designed RCA and multipliers using Peres gates. The subsequent sections delve into the performance analysis including considerations of speed, quantum cost and comparative assessments with traditional non-reversible designs.

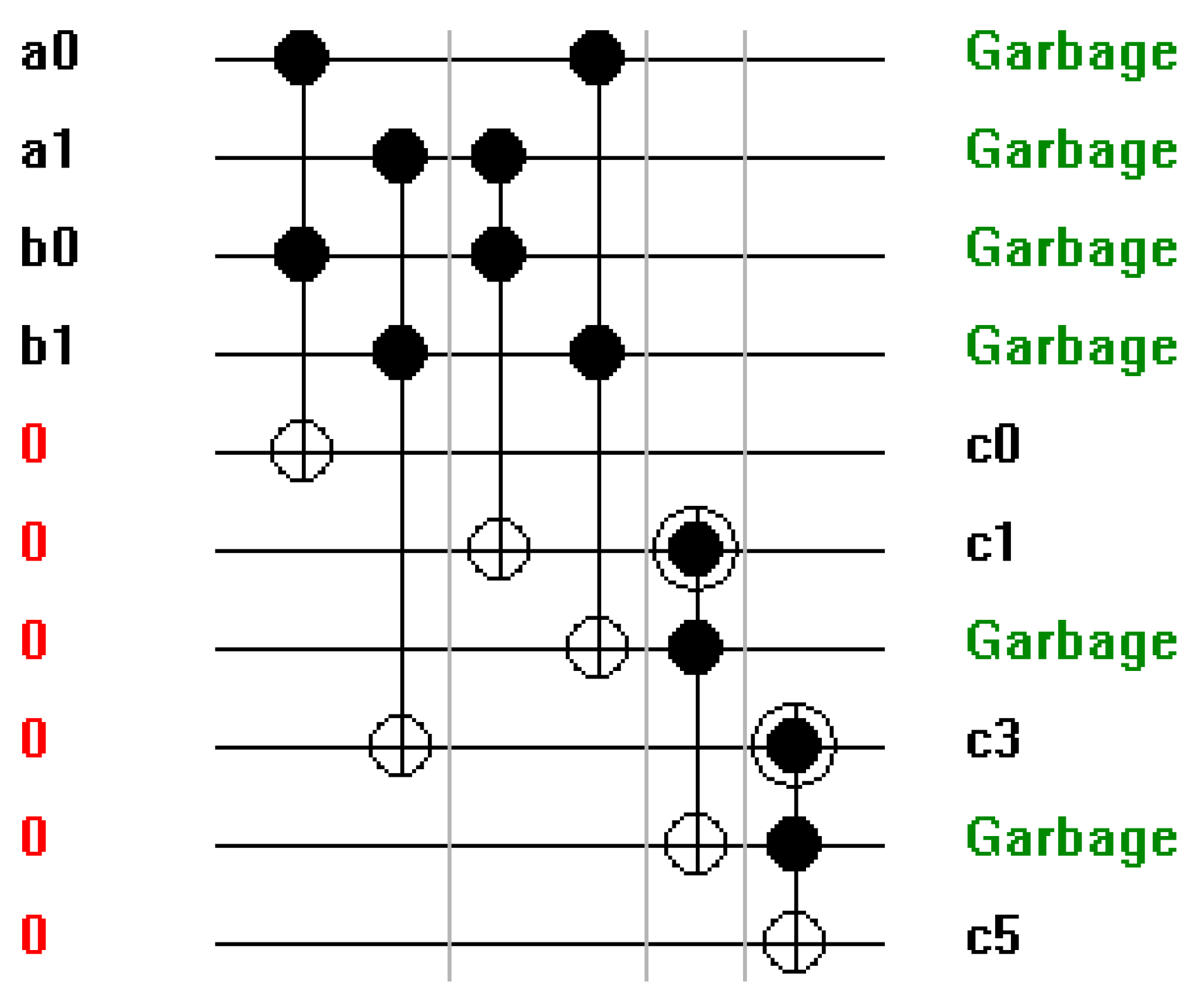

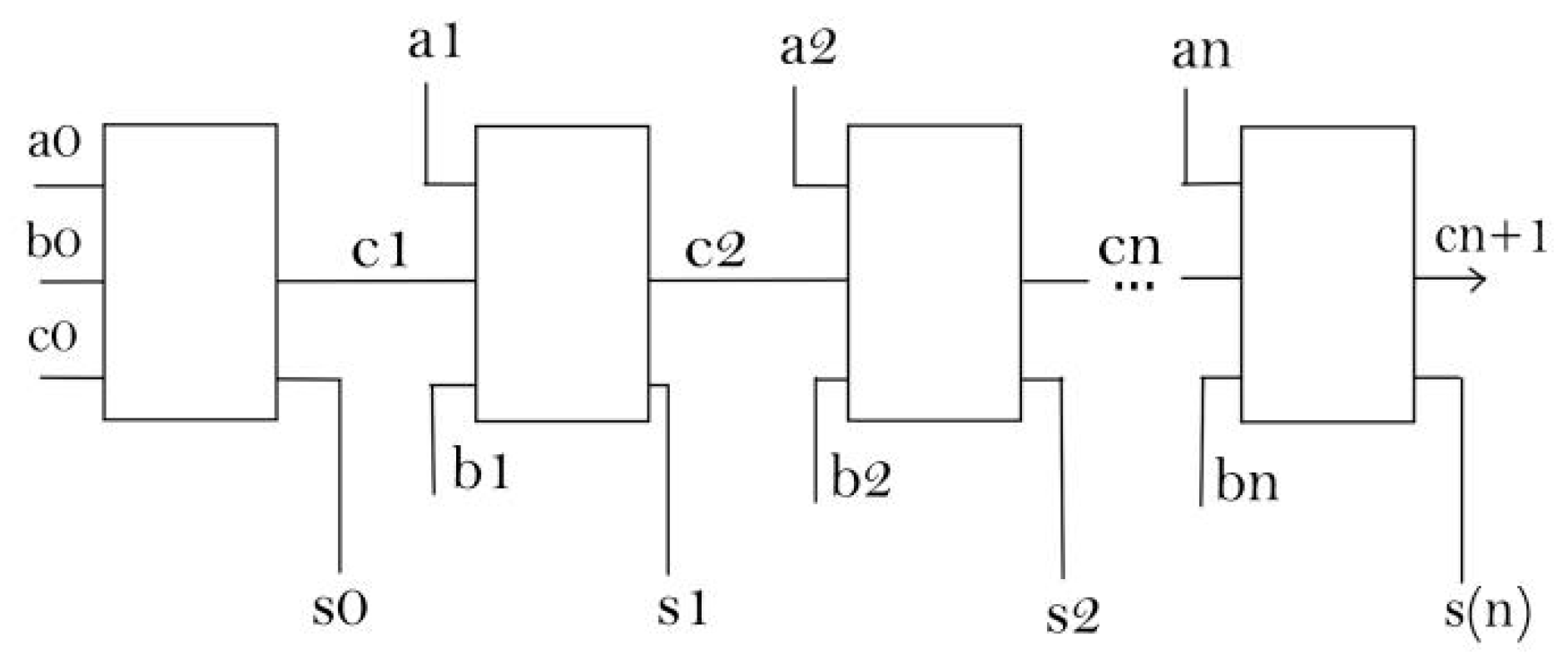

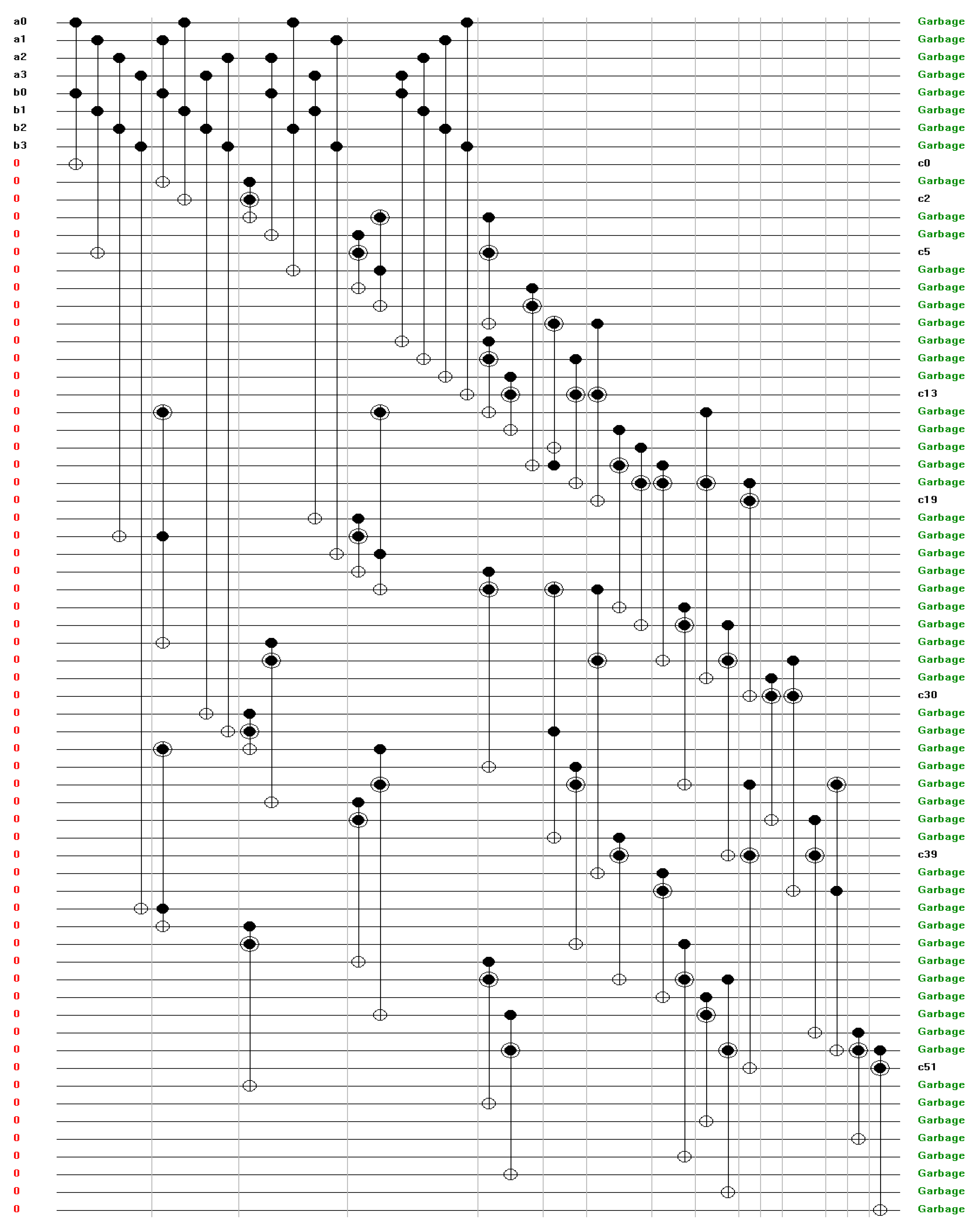

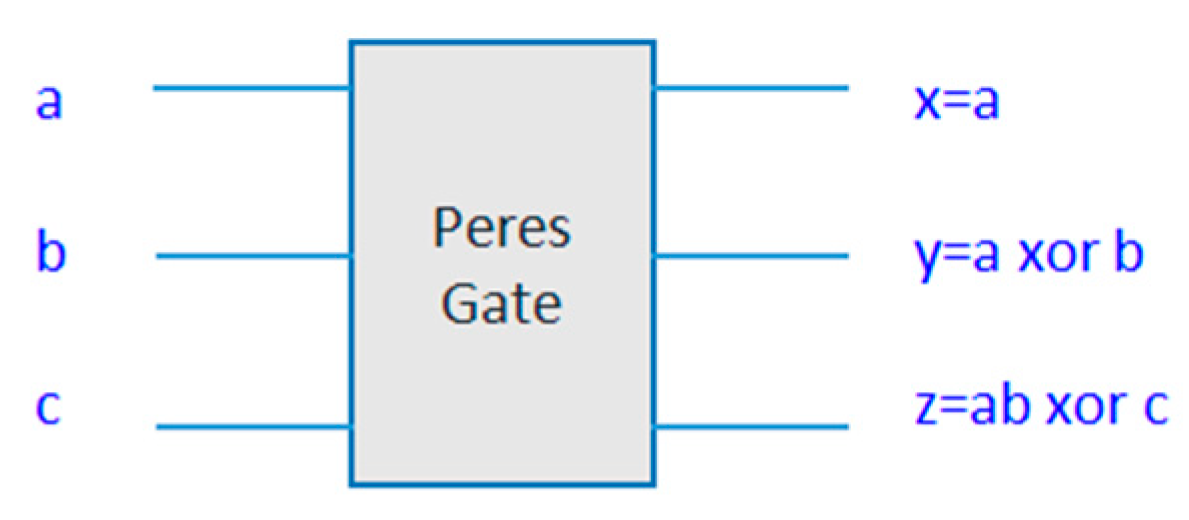

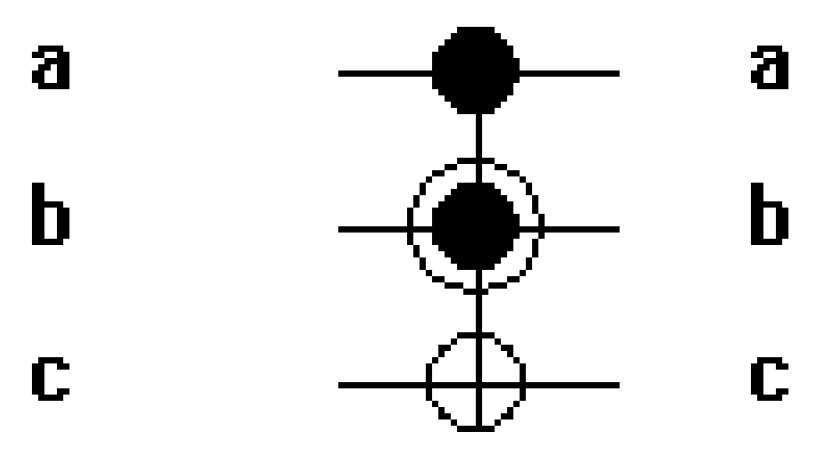

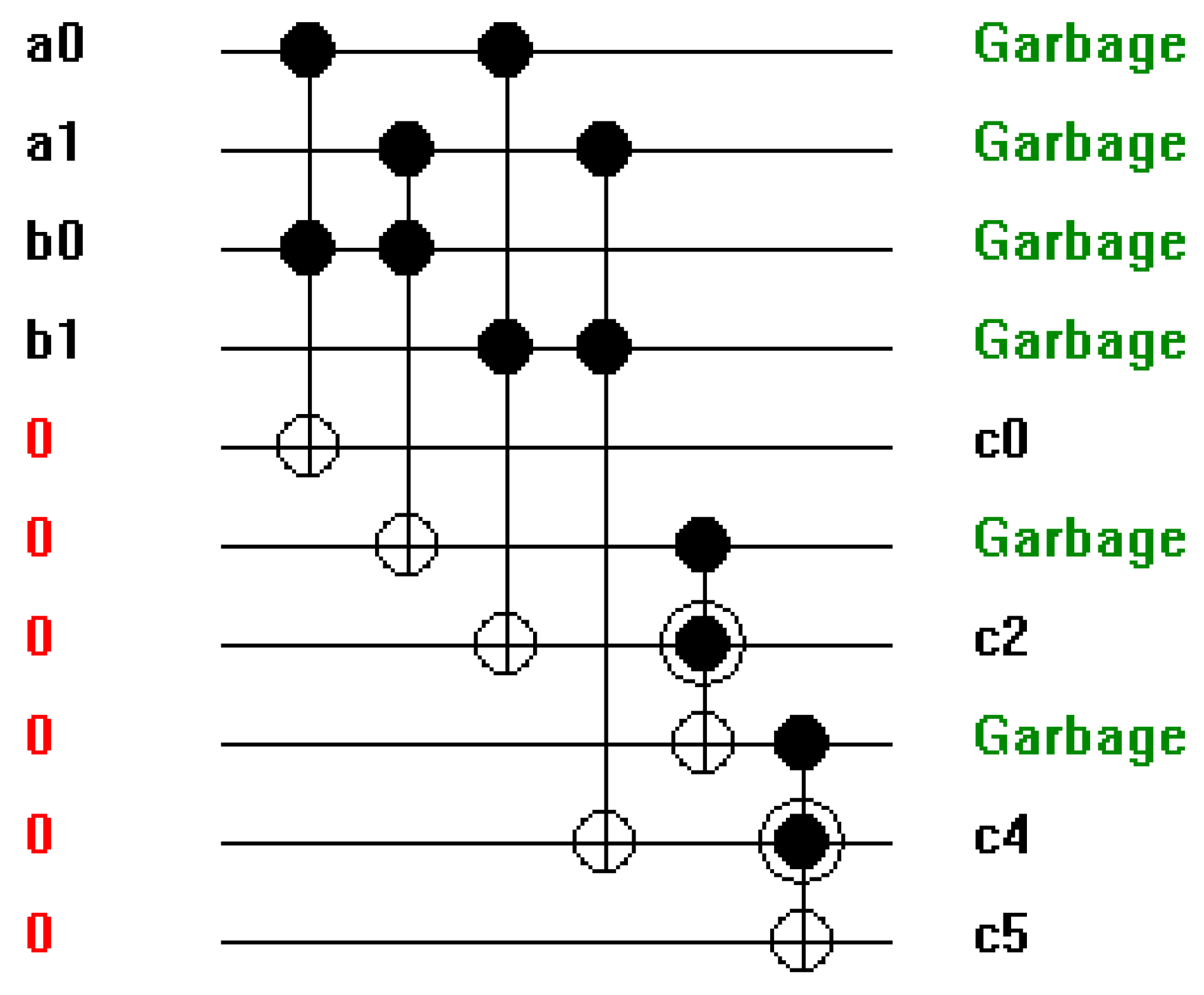

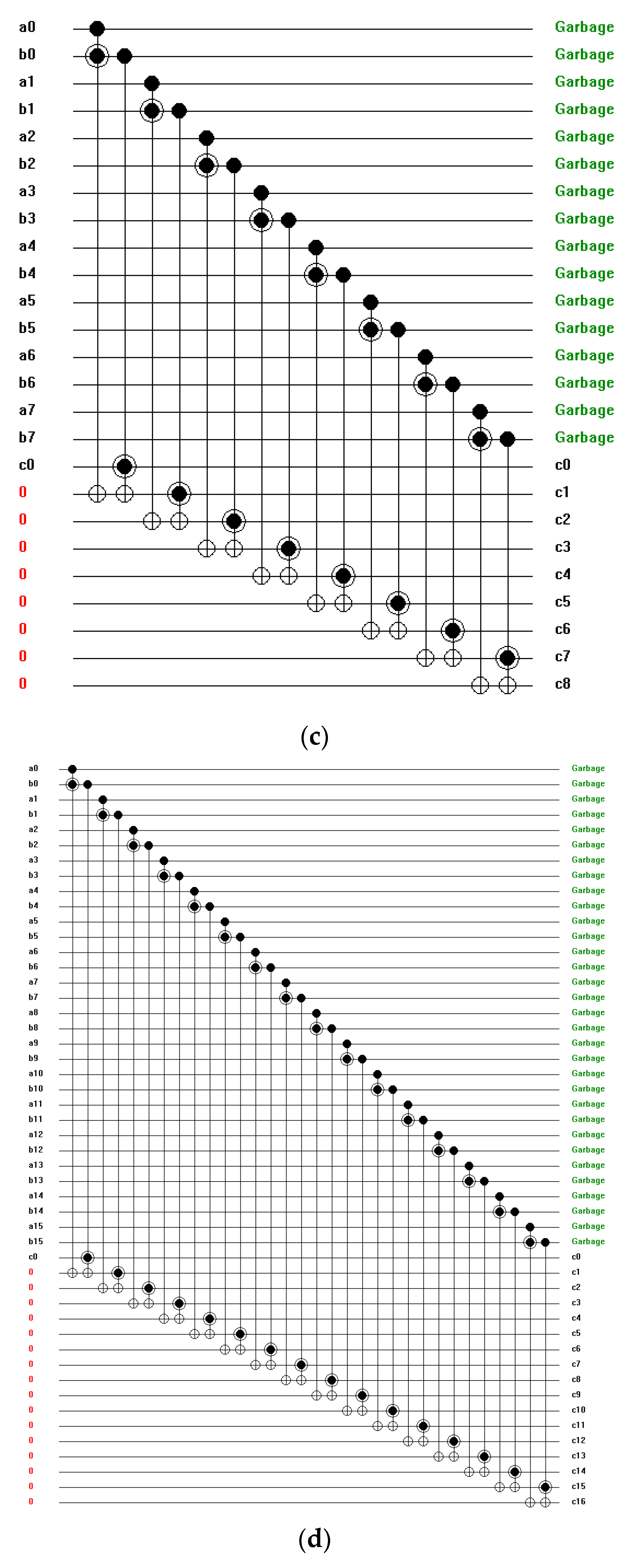

Figure 15.

4X4 multiplier configurations using Toffoli and Peres Gates.

Figure 15.

4X4 multiplier configurations using Toffoli and Peres Gates.

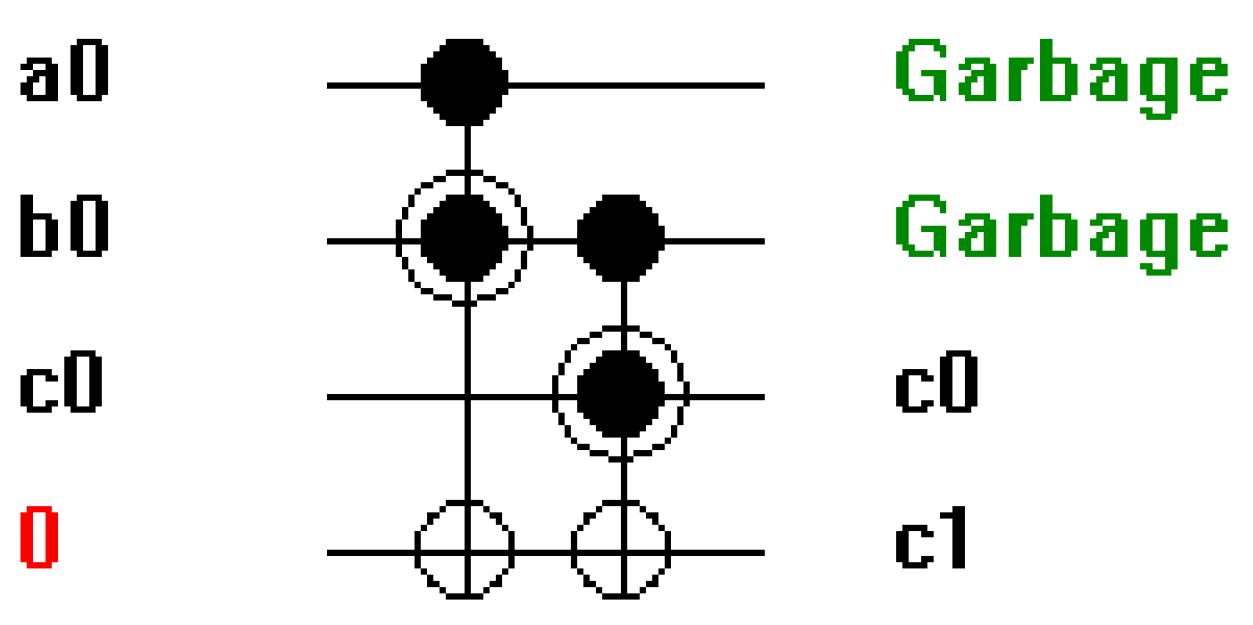

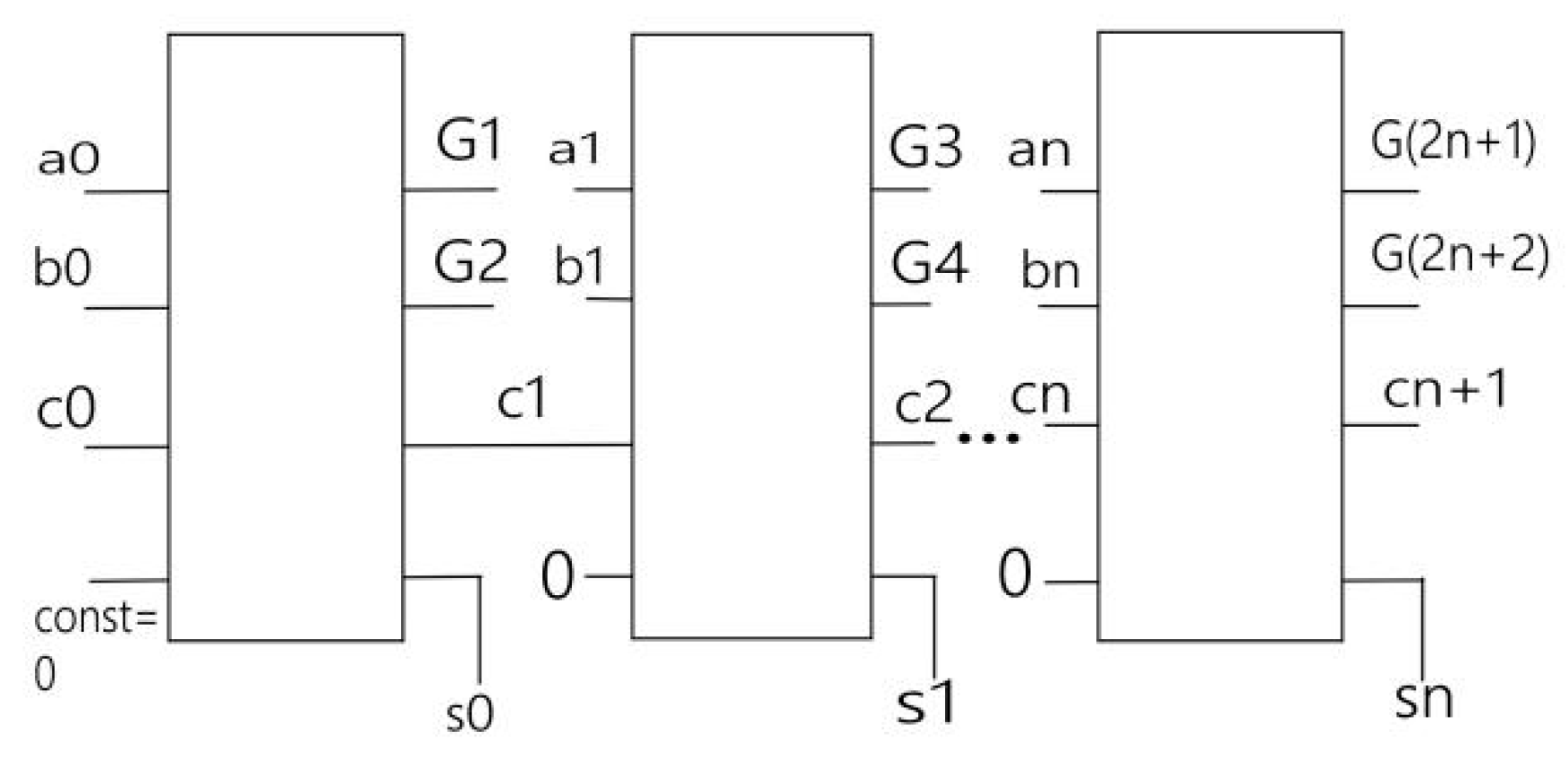

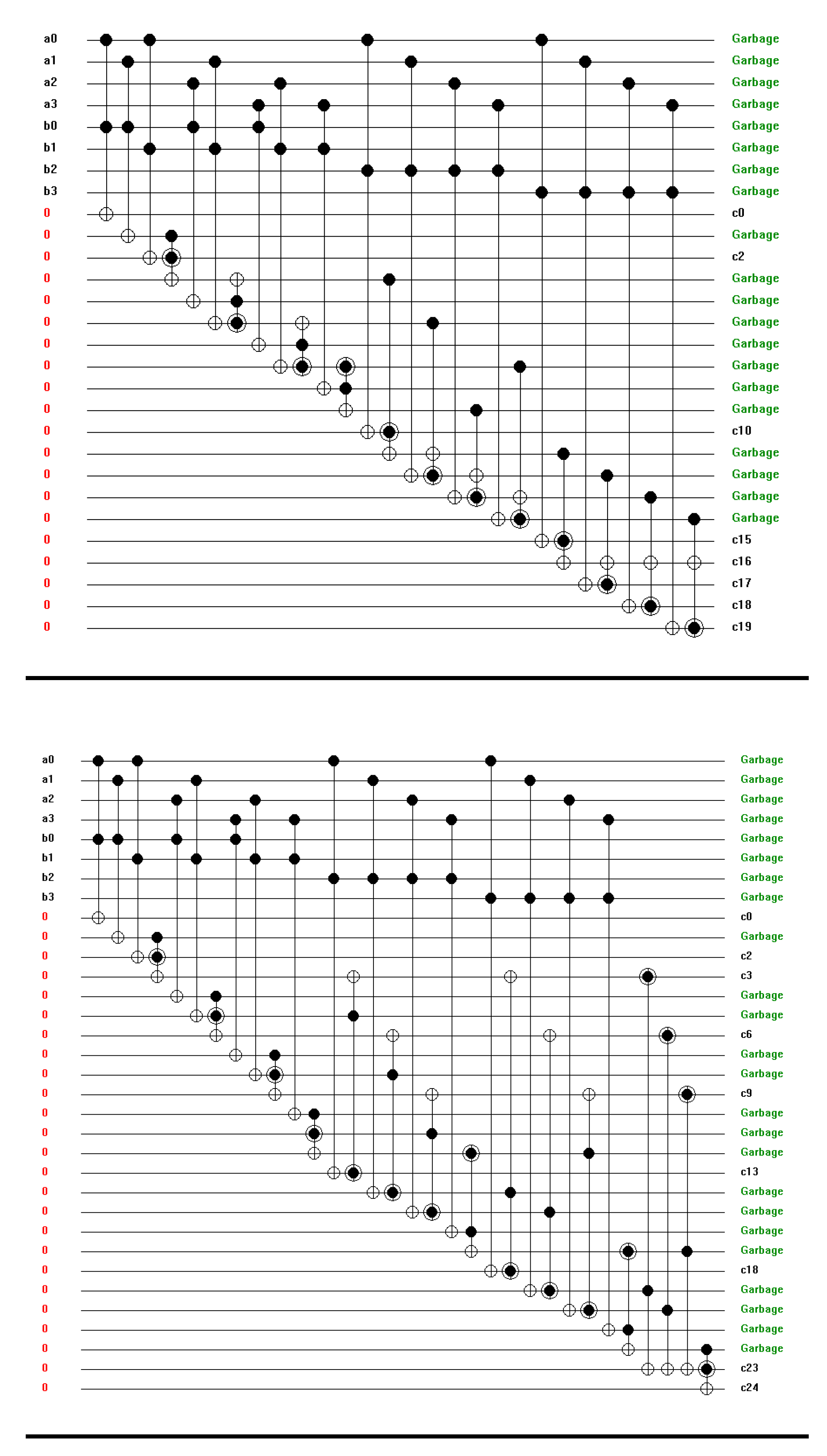

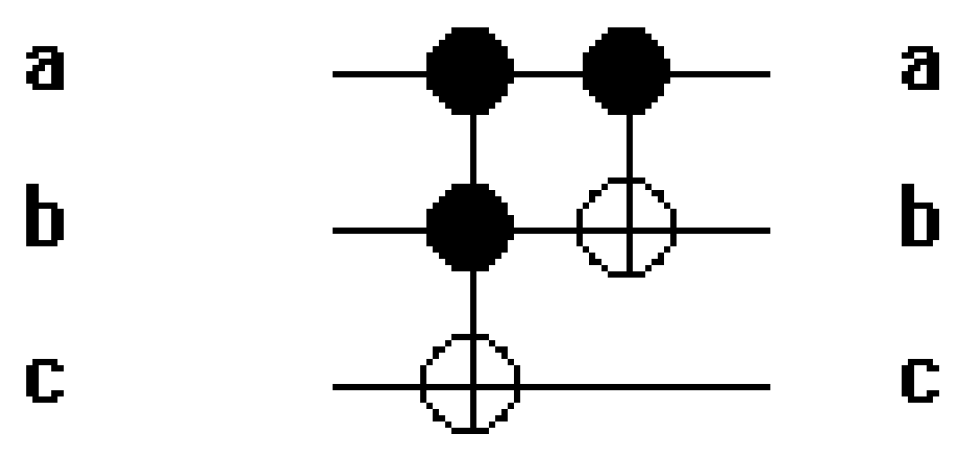

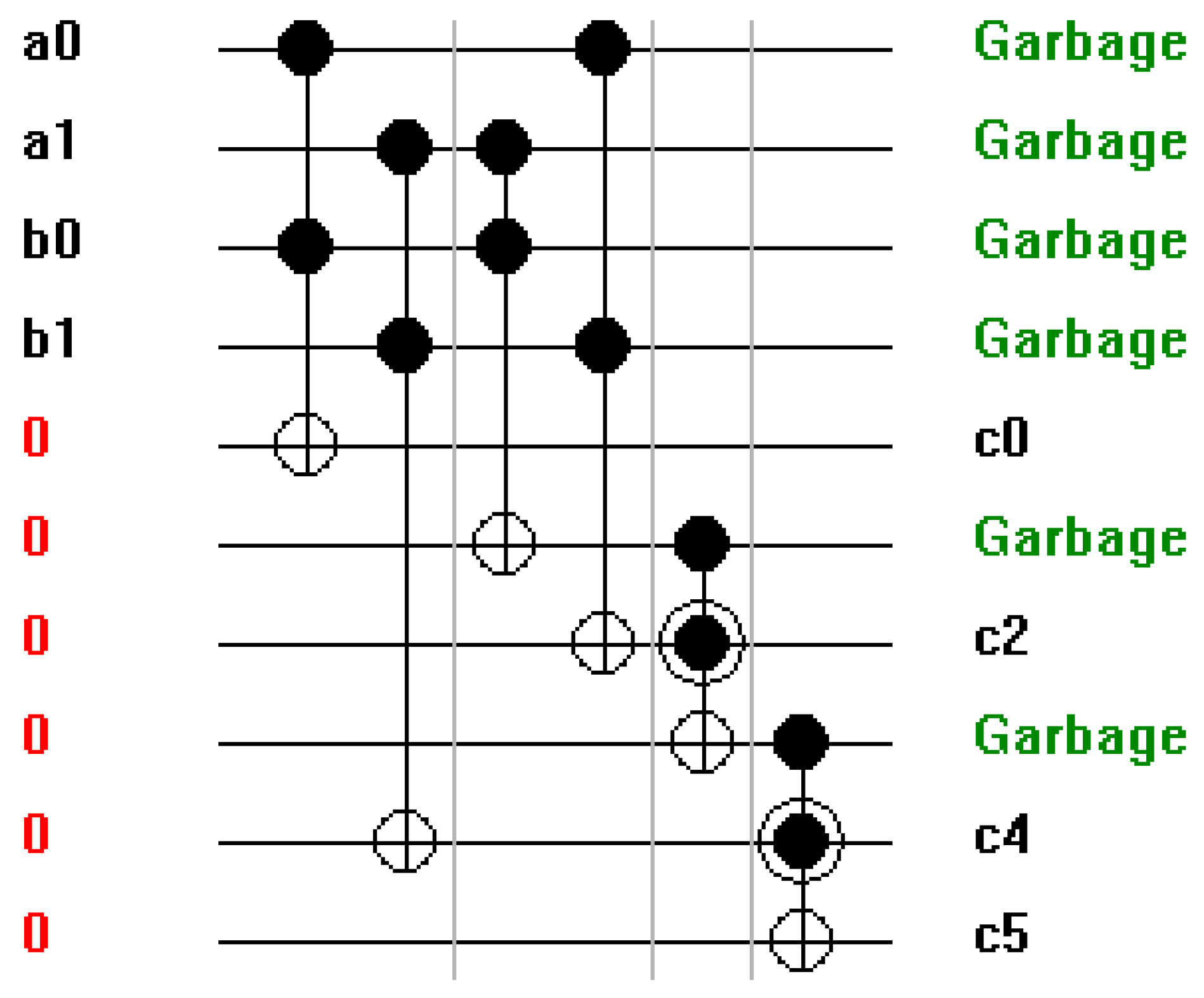

Figure 16.

Level wise decomposition of multiplier configurations using Toffoli and Peres Gates.

Figure 16.

Level wise decomposition of multiplier configurations using Toffoli and Peres Gates.

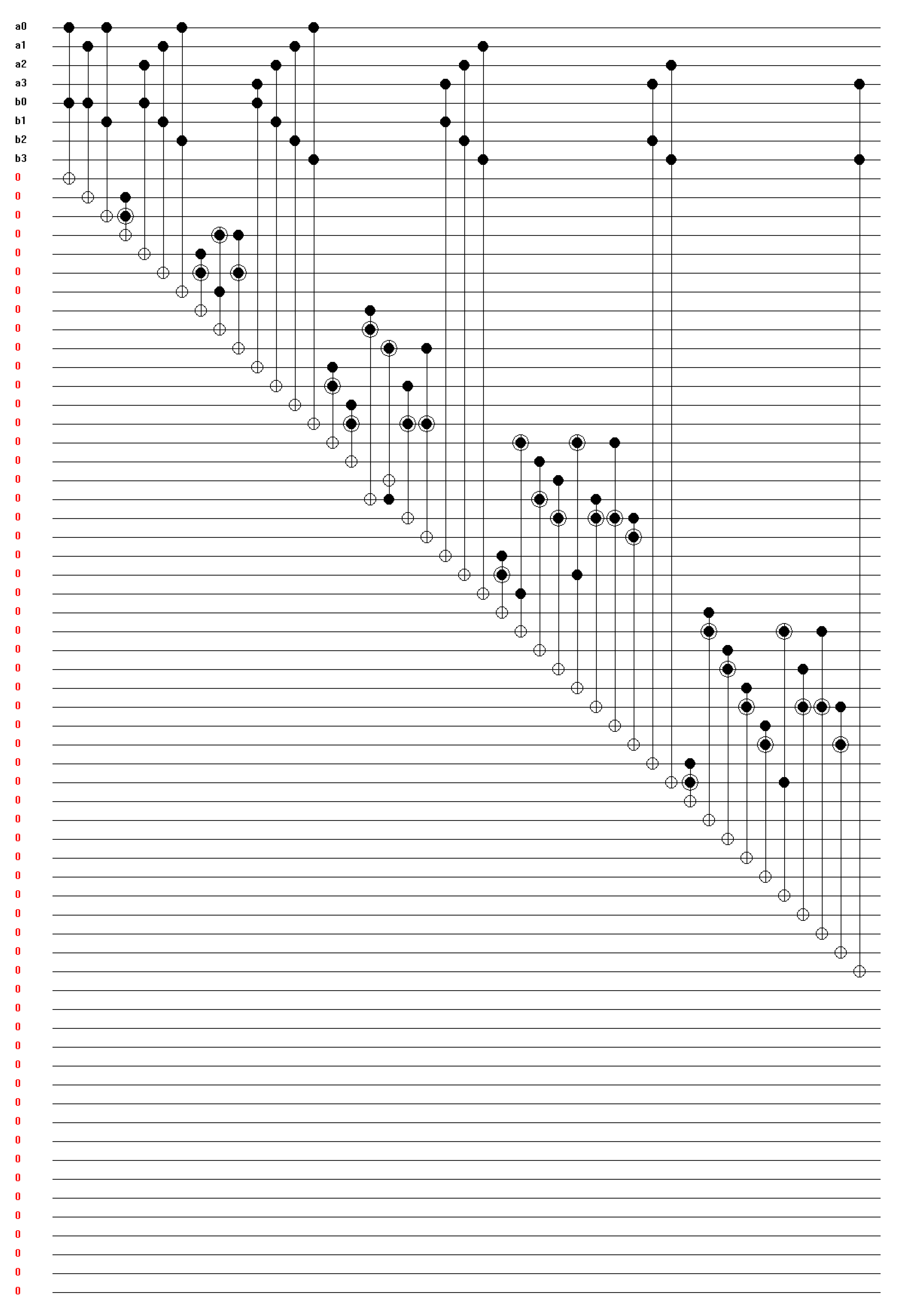

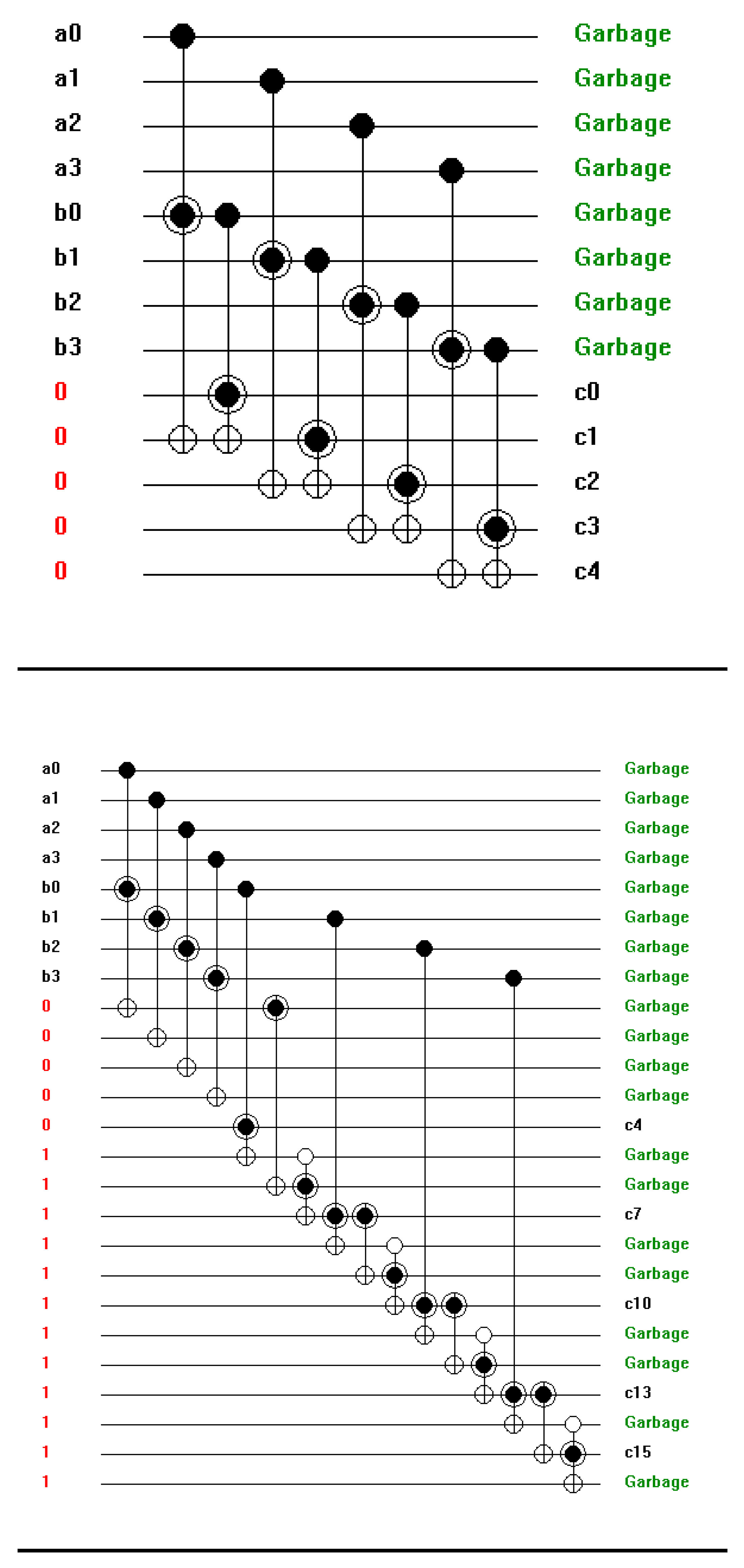

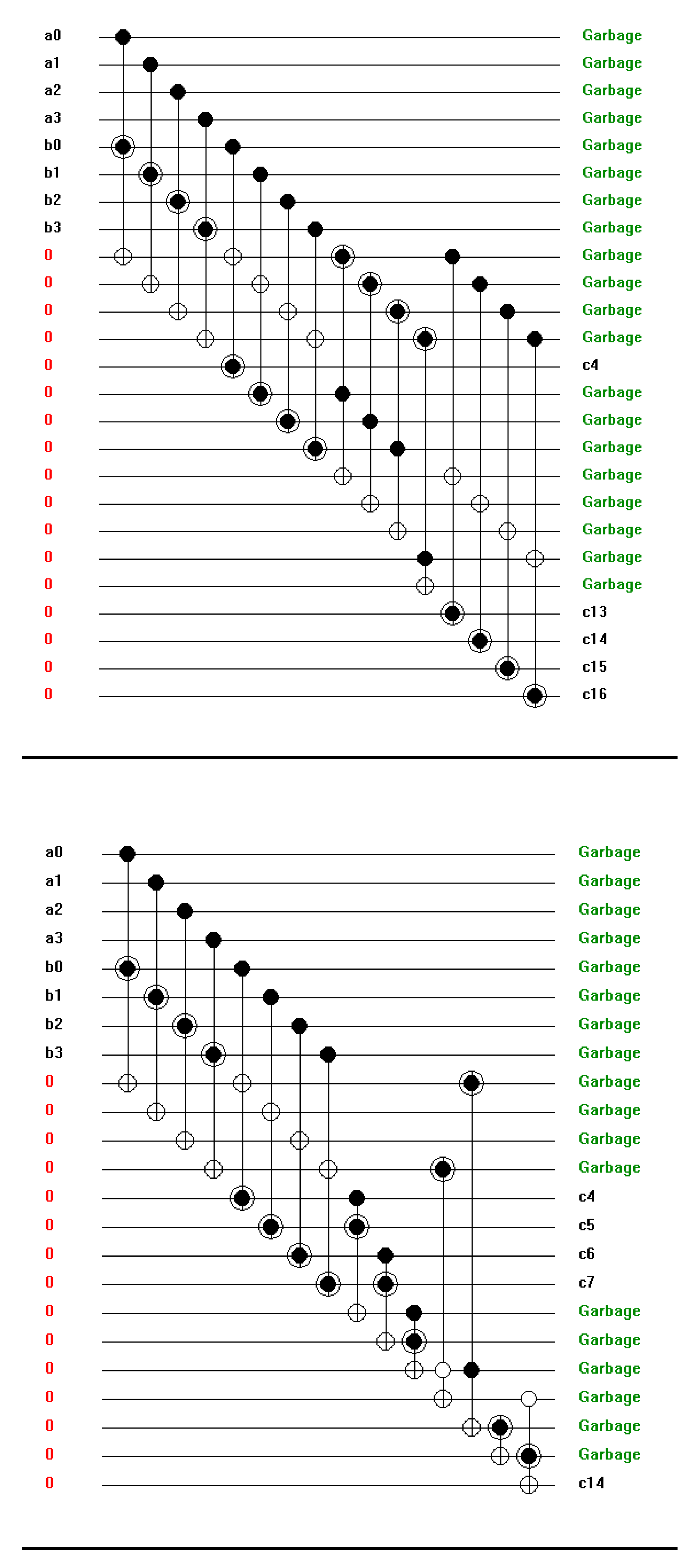

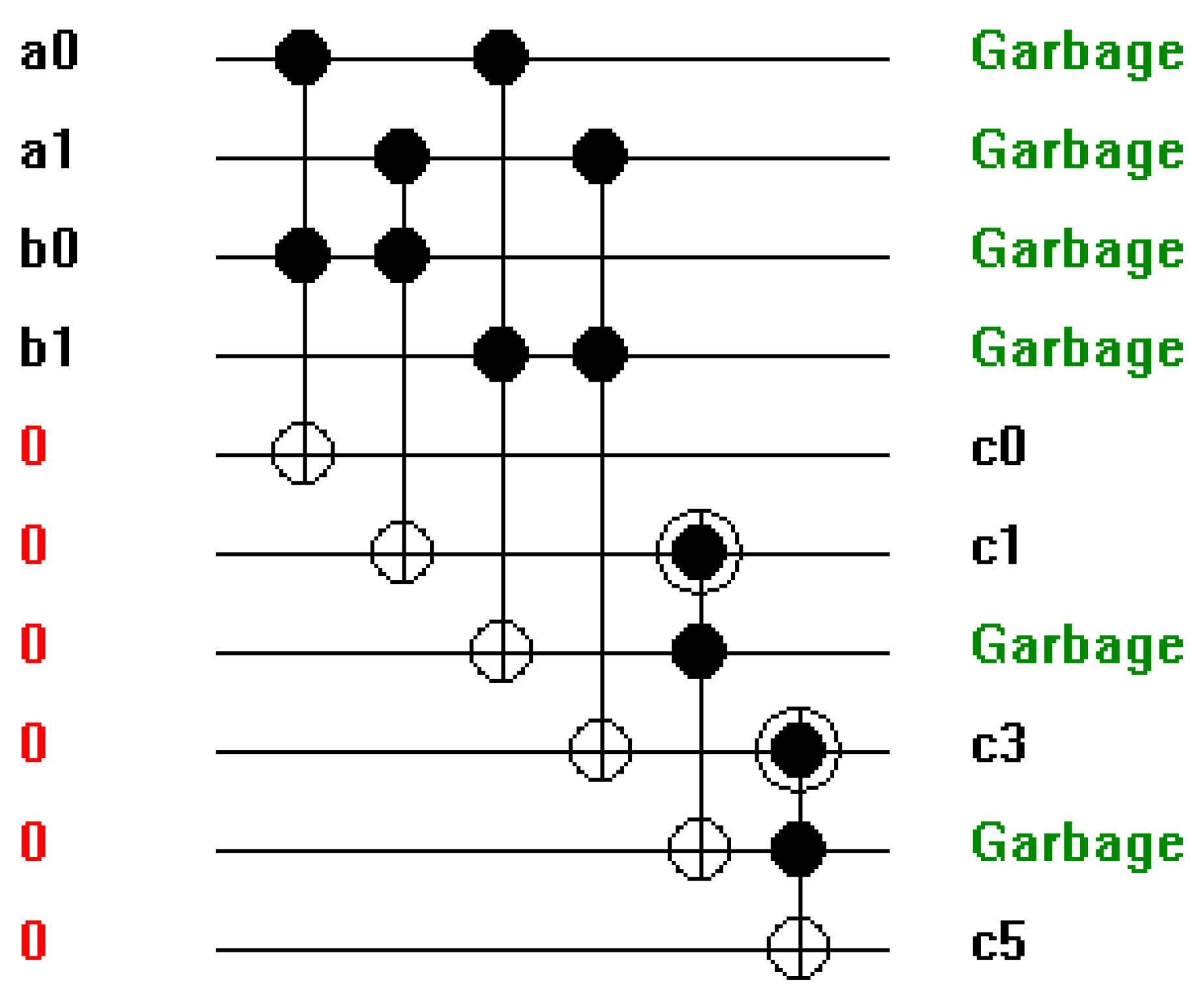

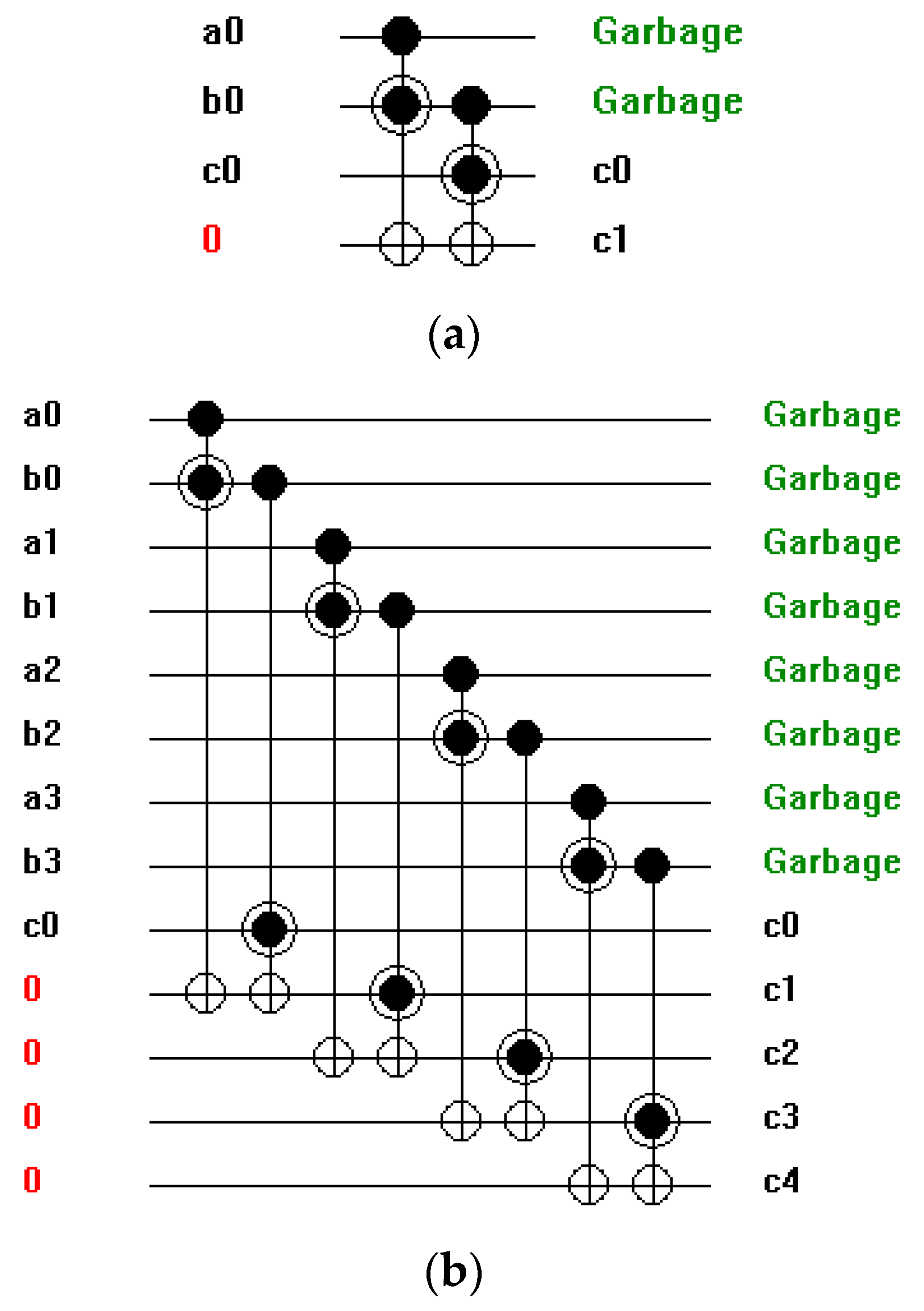

Figure 17.

(a-f) Different 4-bit adder and multiplier configurations using Toffoli and Peres Gates. a. 4-bit Ripple Carry Adder. b. 4-bit Carry Look Ahead Adder. c. 4-bit Carry Save Adder. d. 4-bit Carry Skip/Bypass Adder. e. 4-Bit Multiplier Using Ripple Carry Adder. f. 4-Bit Multiplier Using Carry Save Adder.

Figure 17.

(a-f) Different 4-bit adder and multiplier configurations using Toffoli and Peres Gates. a. 4-bit Ripple Carry Adder. b. 4-bit Carry Look Ahead Adder. c. 4-bit Carry Save Adder. d. 4-bit Carry Skip/Bypass Adder. e. 4-Bit Multiplier Using Ripple Carry Adder. f. 4-Bit Multiplier Using Carry Save Adder.

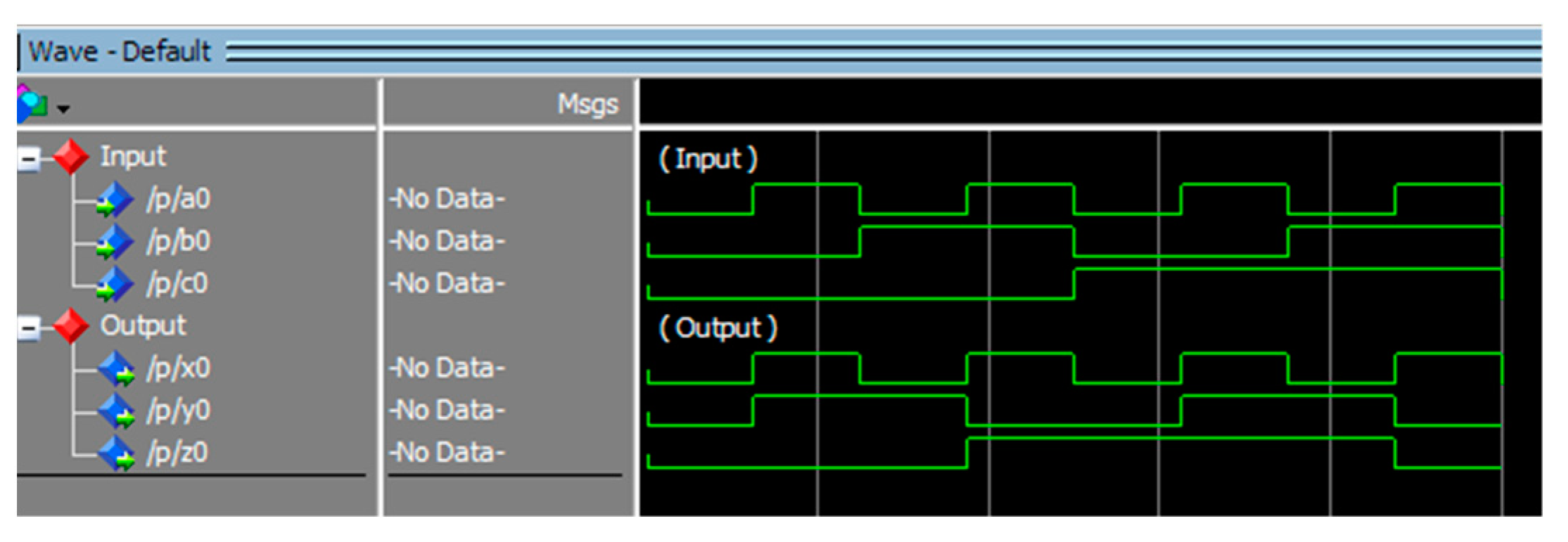

Figure 18.

Simulation result for Peres Gate.

Figure 18.

Simulation result for Peres Gate.

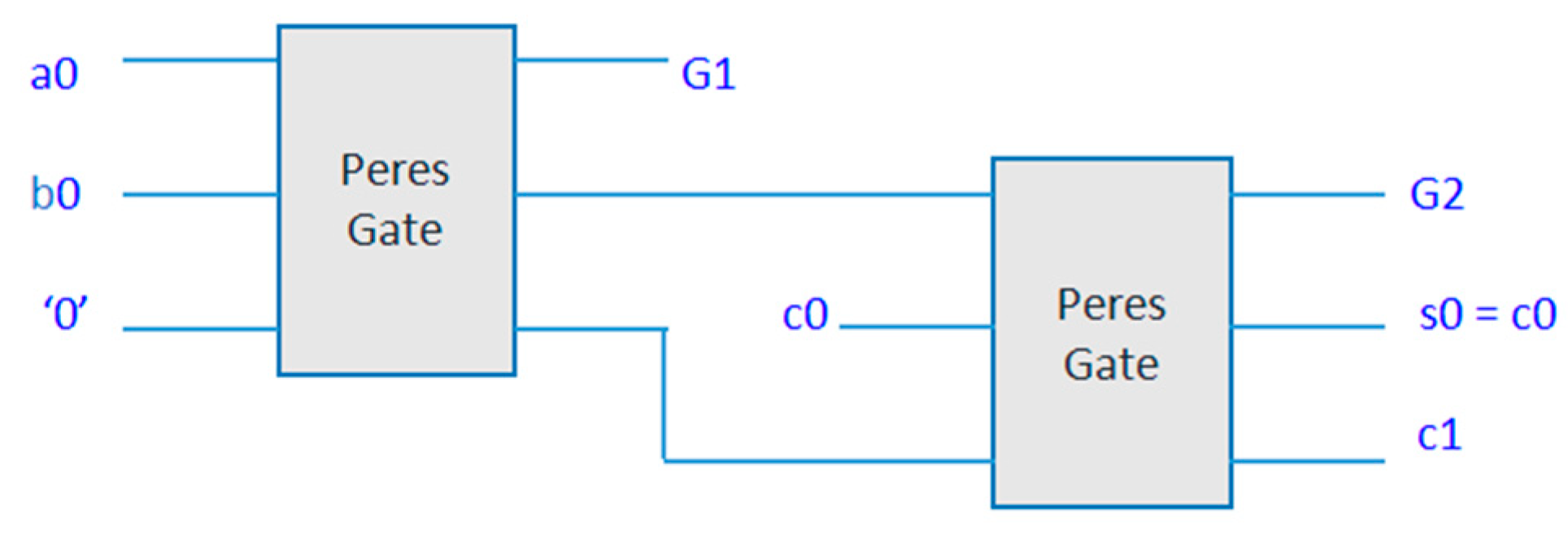

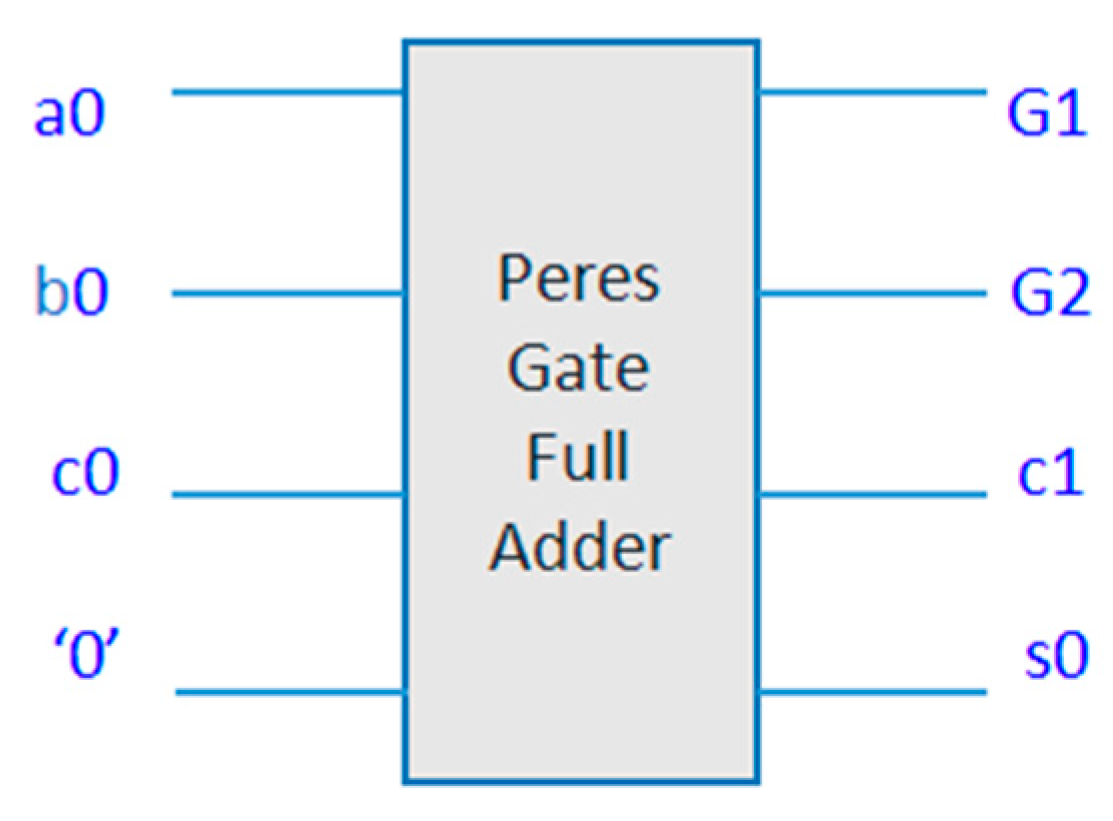

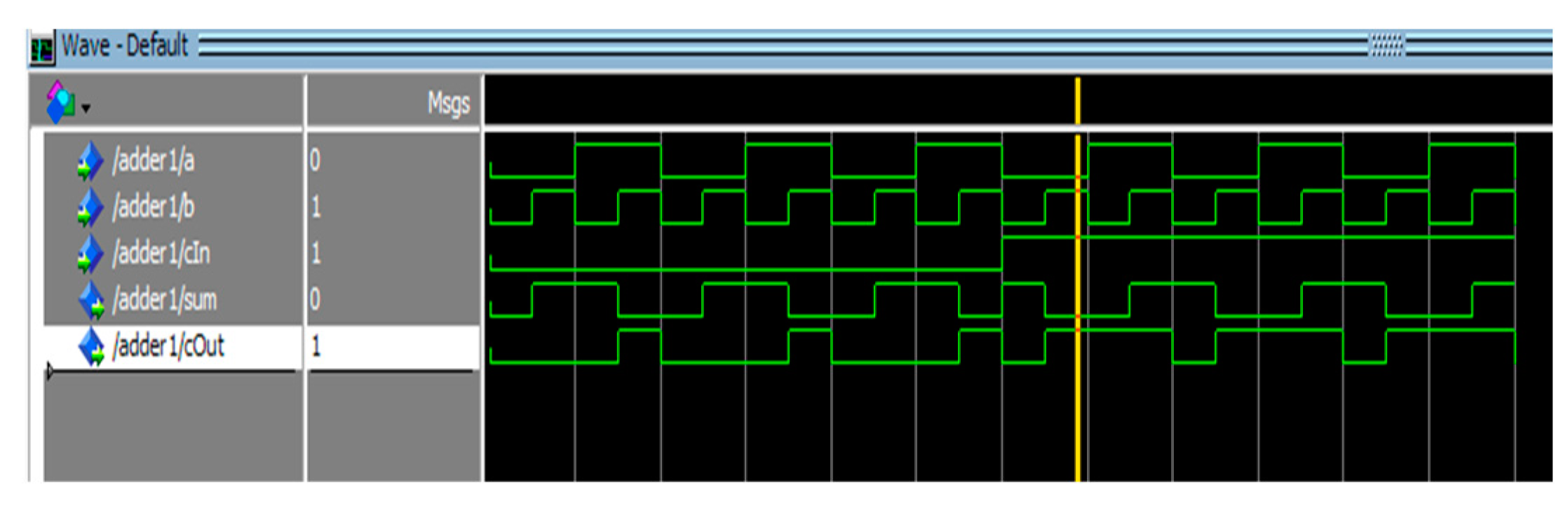

Figure 19.

Simulation result for 1-bit full adder.

Figure 19.

Simulation result for 1-bit full adder.

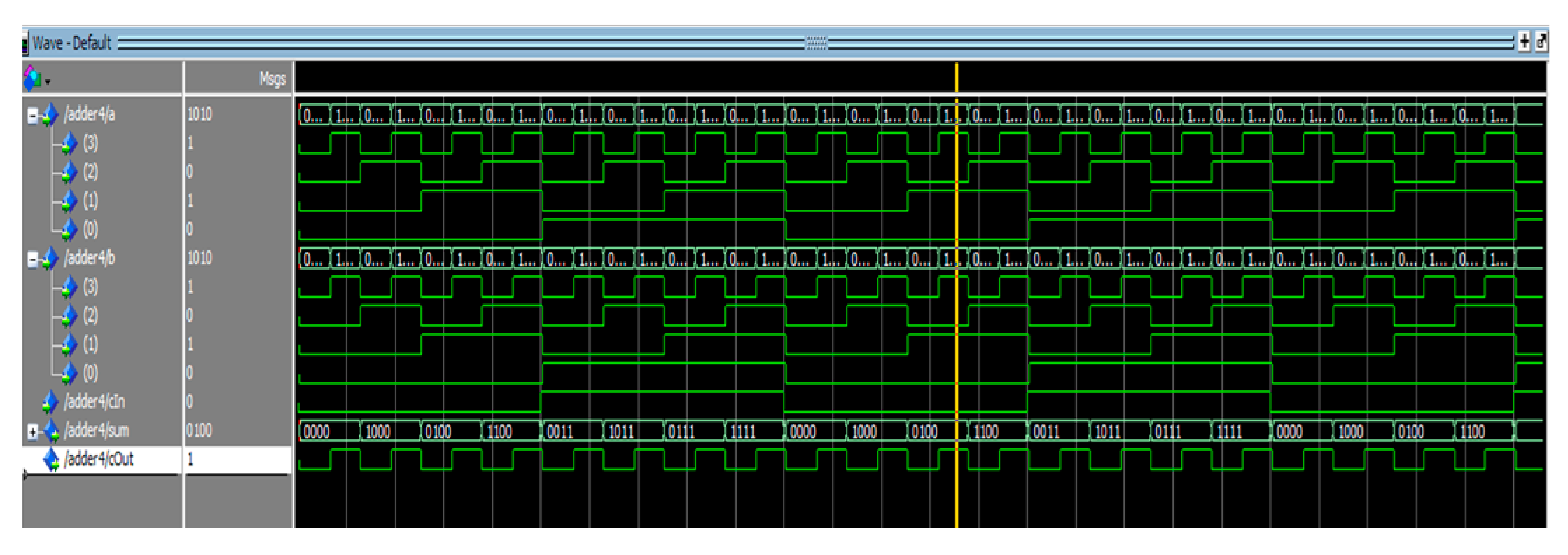

Figure 20.

Simulation result for 4-bit full adder.

Figure 20.

Simulation result for 4-bit full adder.

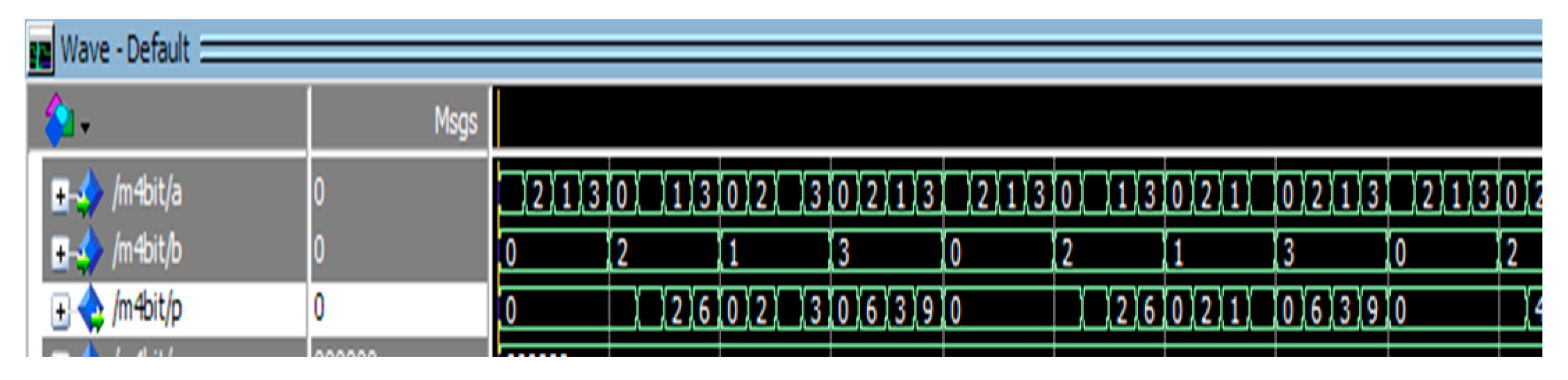

Figure 21.

Simulation result for 2-bit multiplier.

Figure 21.

Simulation result for 2-bit multiplier.

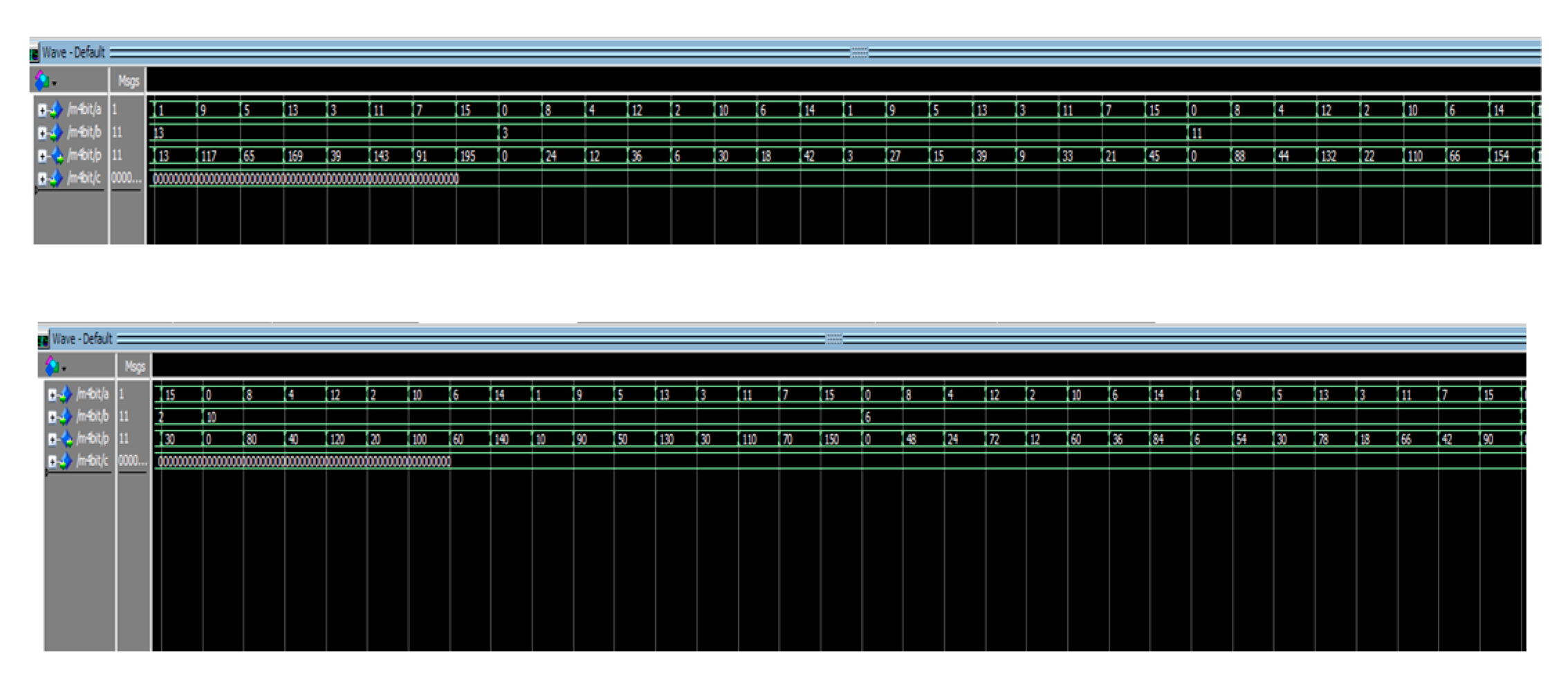

Figure 22.

(a,b) Simulation results for 4-bit multiplier (a) and (b) for different input combinations.

Figure 22.

(a,b) Simulation results for 4-bit multiplier (a) and (b) for different input combinations.

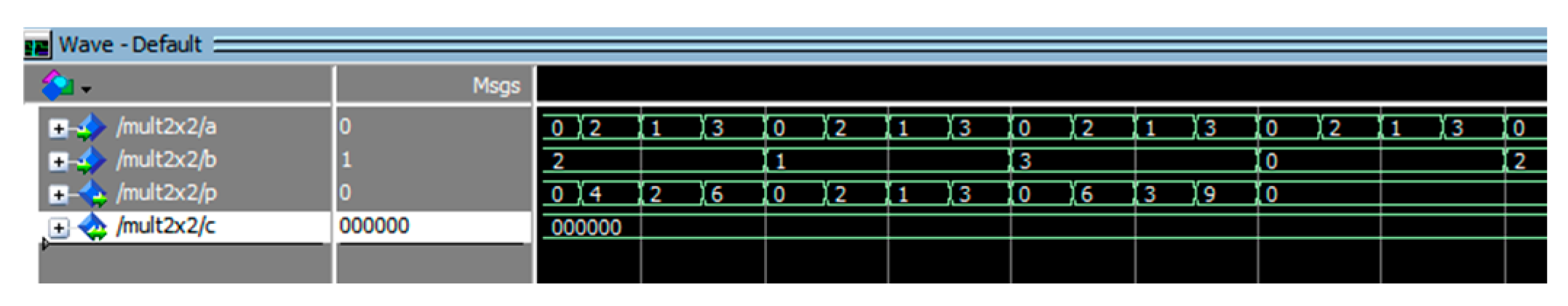

Figure 23.

Simulation result for 2-bit vedic multiplier.

Figure 23.

Simulation result for 2-bit vedic multiplier.

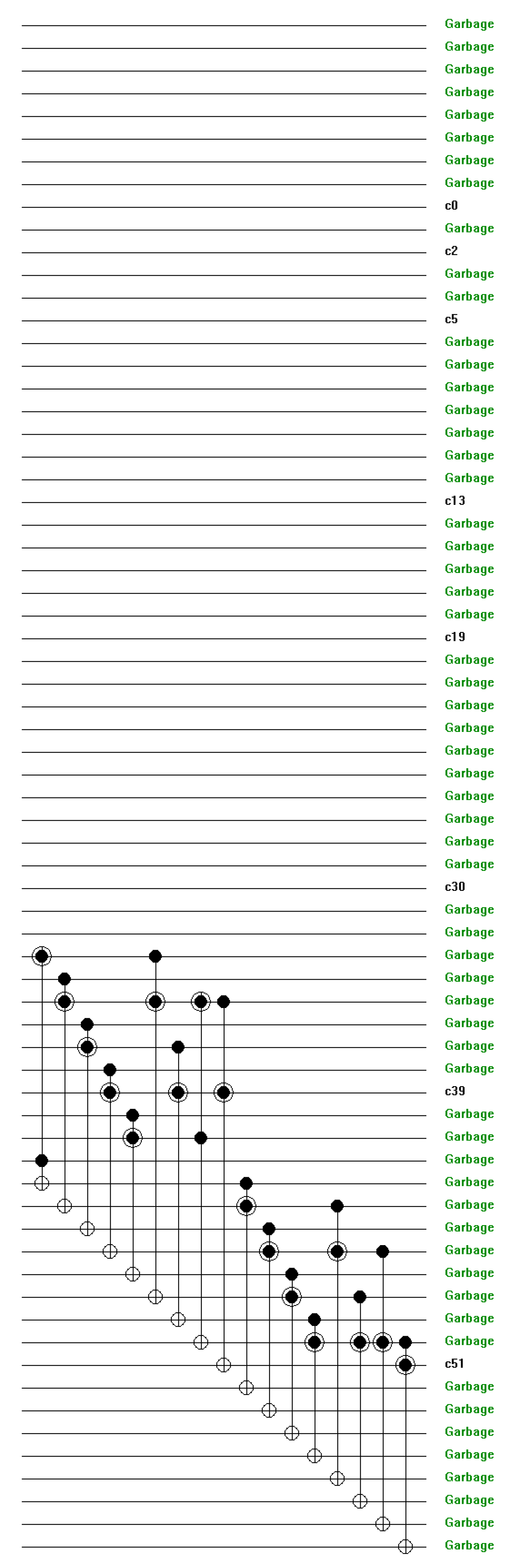

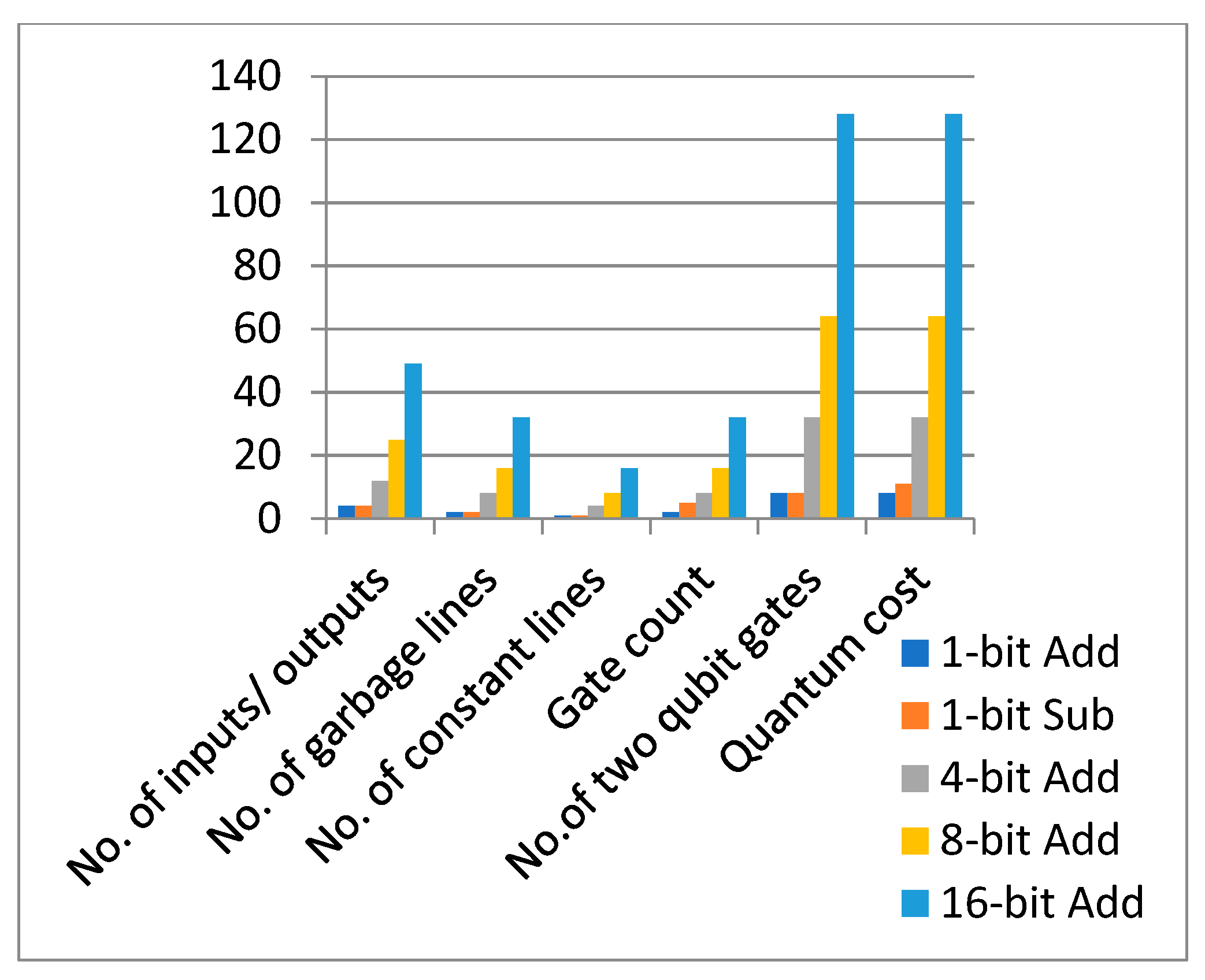

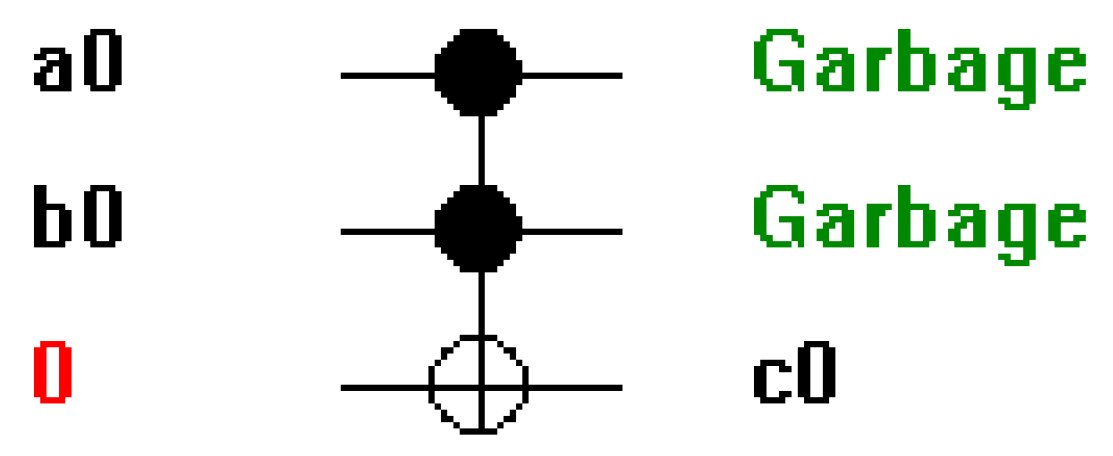

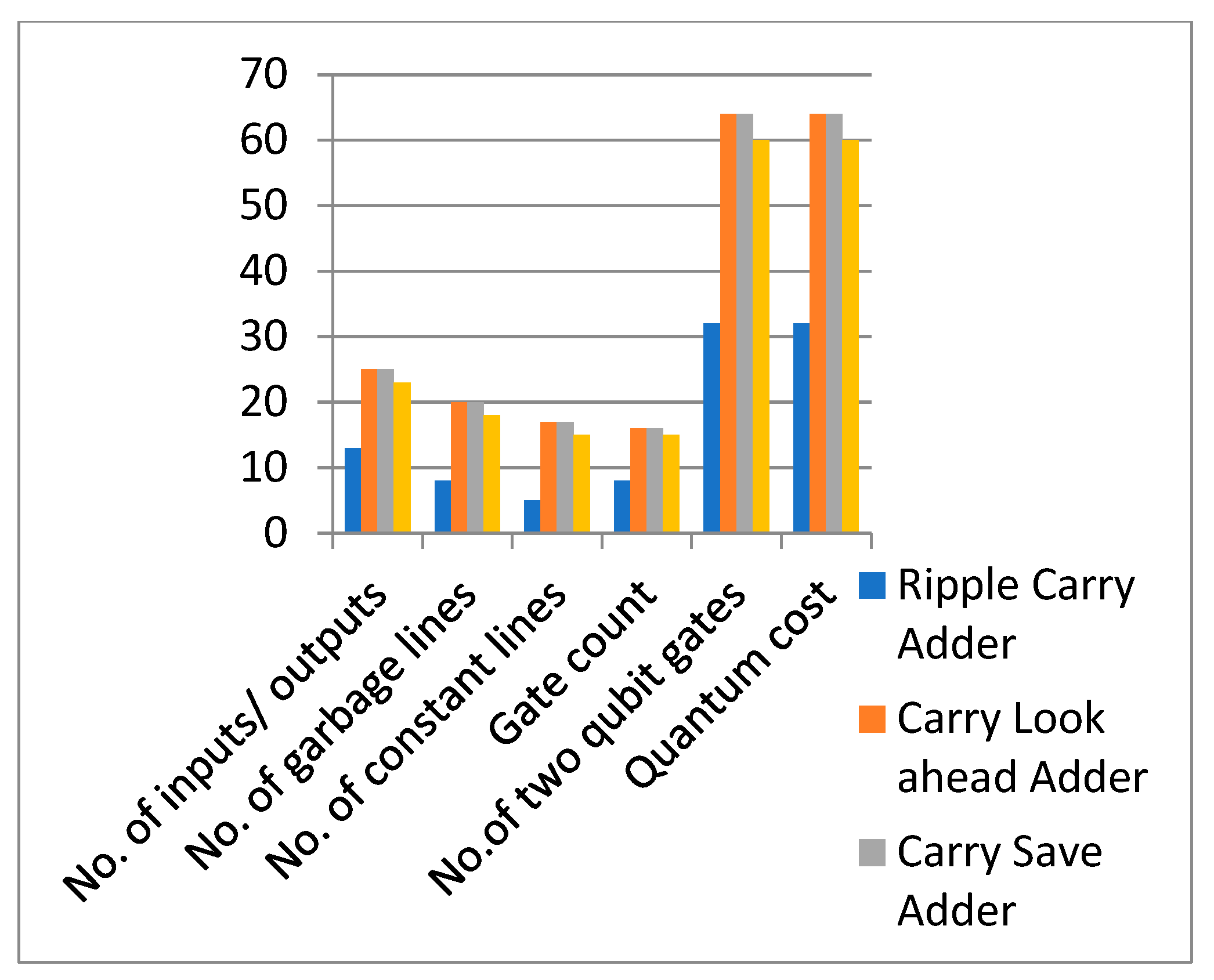

From Figure 26, referring to 1-bit, 4-bit, 8-bit and 16-bit adder configurations verified using RCViewer+ and ModeSim- Intel FPGA starter Edition 10.5b, we can easily develop the following expressions as given below.

-The number of inputs/outputs (n) are calculated as

N= n *3 +1

Where n- number of bits for the adder (in our case 1,4,8,16,….)

-The number of garbage lines (g) can be calculated as g= 2*n

-The number of constant lines c=n

-The number of gates(Gate count) required for constructing adder is calculated as GC=2*n

-The number of two qubit gates(TQ) are given by TQ=8*n

-And finally the quantum cost (QC) is calculated by QC=8*n

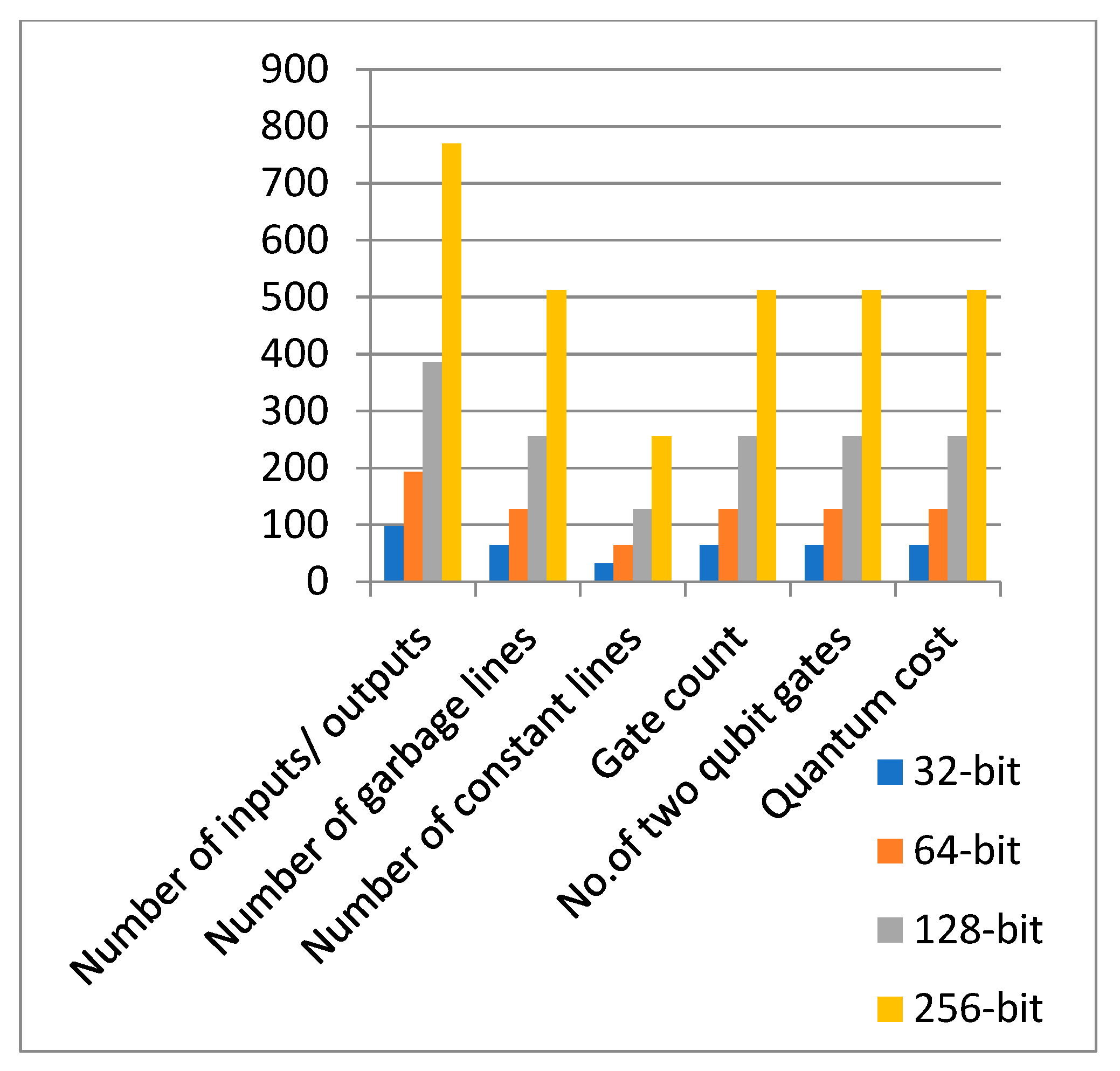

And hence by using above equations we can easily verify the following further adder configurations as shown in Figure 27.

Figure 26.

Performance analysis of Different adder configurations using Peres gates.

Figure 26.

Performance analysis of Different adder configurations using Peres gates.

Figure 27.

Further Performance analysis of Different adder configurations using Peres gates.

Figure 27.

Further Performance analysis of Different adder configurations using Peres gates.

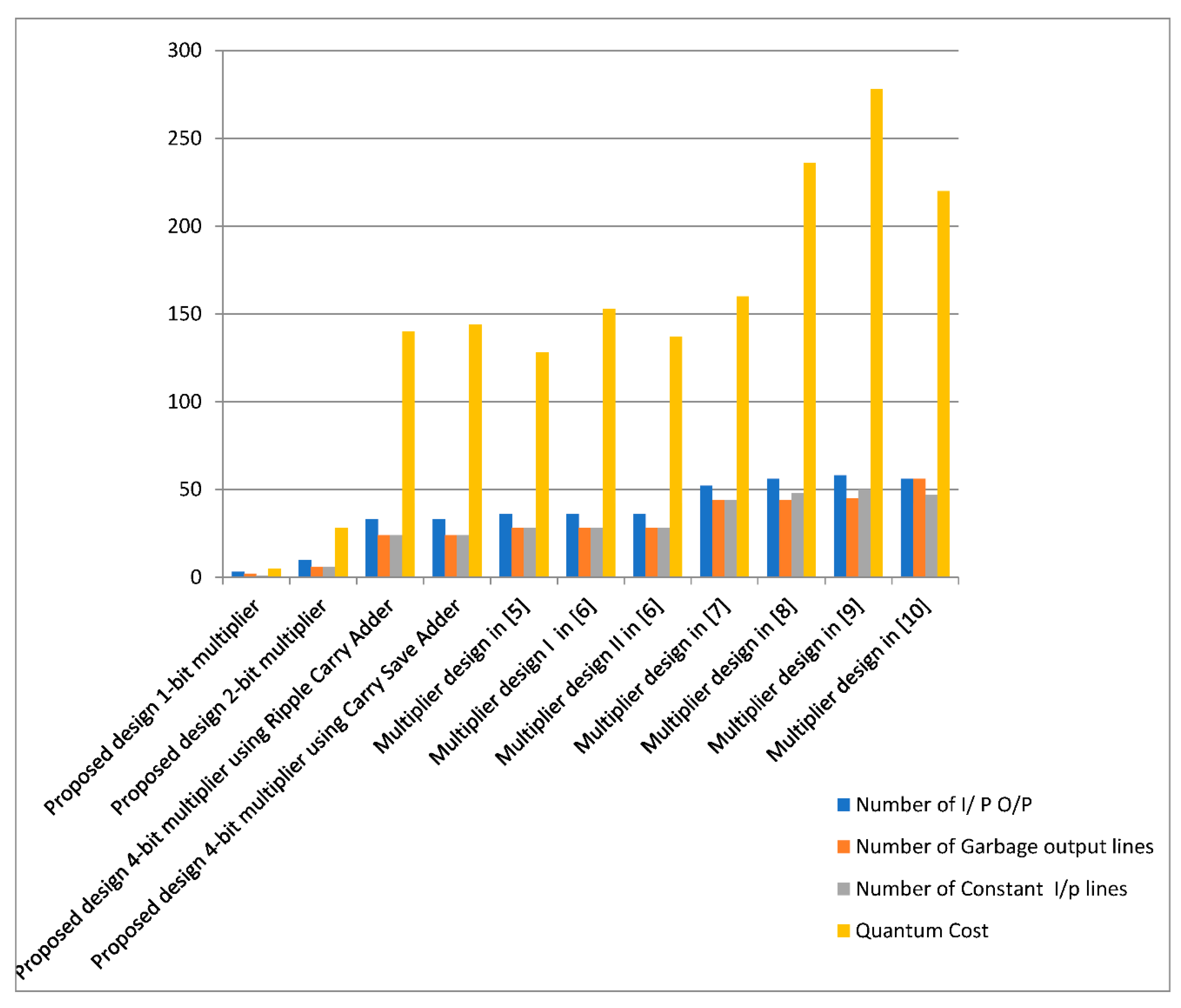

A comparative analysis was conducted between the proposed reversible design and other reversible designs available in literature. This analysis considered factors such as gate count, energy consumption and overall circuit complexity.

The goal was to highlight the potential advantages of the reversible approach especially in terms of information preservation and resource utilization. Quantum speedup potential which is a measure of how much faster a quantum algorithm could perform a specific task compared to its classical counterpart was explored. The inherent reversibility of the designed circuit using Peres gates positions it favorably for potential quantum speedup in certain algorithms contributing to the broader understanding of reversible logic in quantum computation. After comparing all the reversible adders using different techniques, we can say that the ripple carry adder is best suited due to the low metric values as mentioned in

Figure 28. The less number of inputs, constant and garbage lines, quantum cost requirement to design adder circuit are advantageous to use ripple carry adder.

In

Table 2, various reversible logic gates used are Feynman Gate(FG), Toffoli Gate(TG), Fredkin Gate(FRG), Peres Gate(PG), New Gate(NG), TSG Gate(TSG), MKG Gate(MKG), HNG Gate(HNG), PFAG Gate(PFAG) for comparison on the number of gates used for the construction of different reversible multiplier configurations. First three multiplier circuits are designed as a part of research in this research article using only Toffoli and Peres Gates. The other comparative circuits used other reversible gates available in literature as shown in the table. In

Figure 29 the comparison of different multiplier circuits is made in the basis of quantum cost. The 4-bit reversible multiplier proposed in this article has comparable quantum cost as compared to other multiplier circuits. The reduced quantum cost as 256 is the main outcome of this research as compared to more quantum cost for the same circuit design in literature.

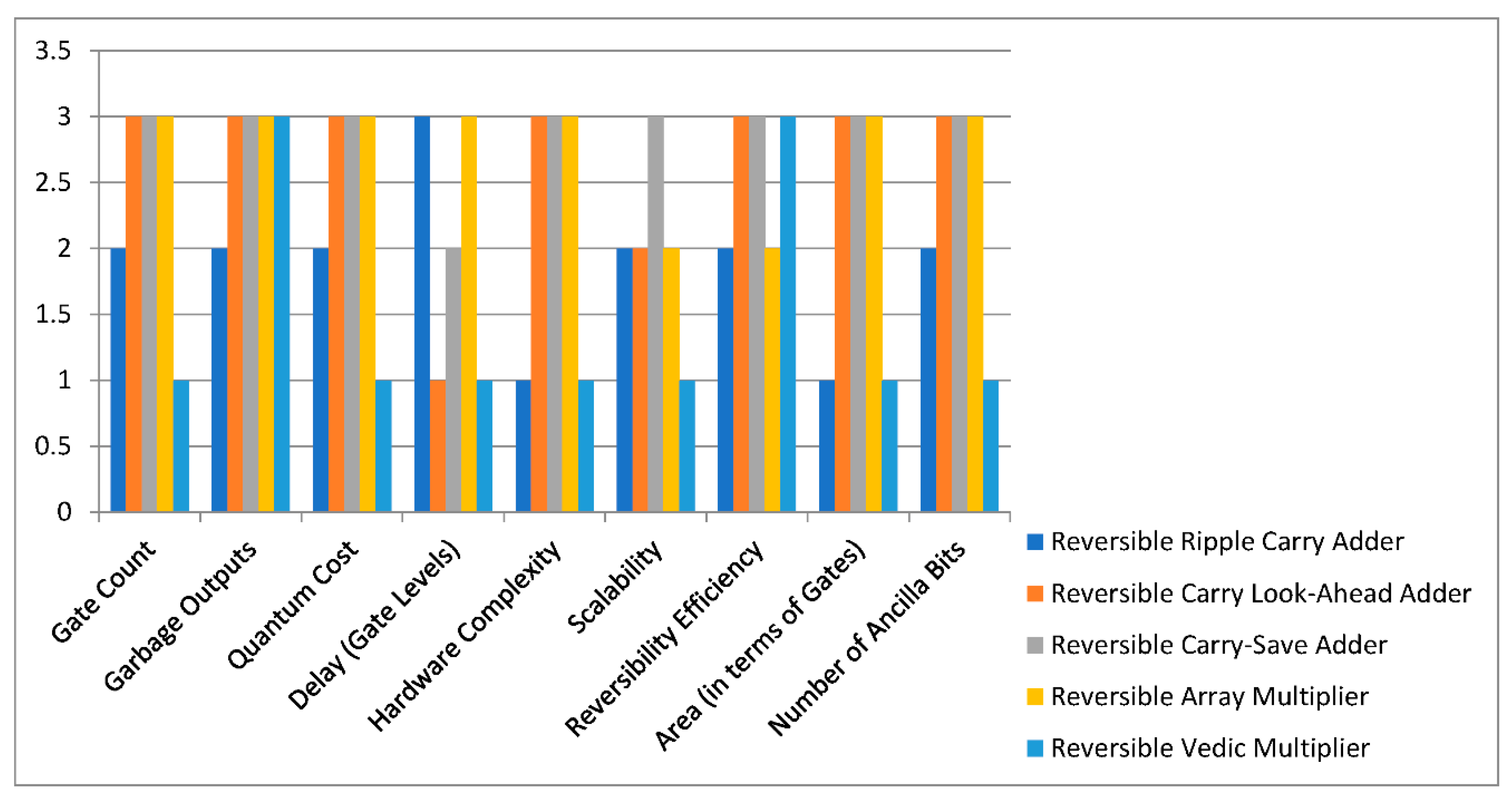

The analysis also considered potential optimization opportunities for the design. This includes exploring advanced reversible gates, circuit restructuring or algorithmic enhancements to further improve performance metrics and address any identified limitations. The comprehensive evaluation of performance metrics provides valuable insights into the strengths and potential areas of improvement for the RCA design using Peres gates. The outcomes of these analyses contribute to the broader understanding of reversible logic circuits and their applications in emerging computational paradigms. In

Figure 30, Levels 1,2 and 3 on Y-axis represents Low, Moderate and High levels respectively. From this figure we can conclude that the vedic multiplier the best reversible multiplier with low gate count, quantum cost, gate level delay, hardware complexity, scalability, area and number of Ancilla bits with high garbage outputs which can be neglected as the reversibility efficiency provided by this circuit is high. The ripple carry adder constructed using reversible logic has all metrics considered to be at moderate level, but it provides higher gate level delays which can be neglected as the hardware complexity and area in terms of gates is also less.

After examining all the adders and multiplier circuits using Toffoli and Peres gates, a comparison table for designing various adders and multipliers using reversible logic is prepared and presented in terms of a chart as shown in

Figure 30. The key parameters considered in the design of reversible circuits includes all the metrics used measure the performance of these circuits.

As a matter of facts the reversible ripple carry adder is suitable for low power applications but has higher delay due to the sequential carry propagation. The reversible carry look-ahead adder is faster than ripple carry due to parallel carry calculation but requires more gates and garbage outputs. The reversible carry save adder is used in multi-operand addition scenarios like in multipliers but with higher complexity. The reversible multiplier is simple design but has high gate count and quantum cost. The reversible adder and multiplier design using vedic mathematics are optimized for high-speed operations but at the cost of significantly increased hardware complexity and power consumption.