1. Introduction

The continuous advancement in semiconductor technology has enabled the development of highly integrated and efficient digital systems. The Arithmetic Logic Unit is a fundamental building block of digital processors responsible for performing arithmetic and logical operations. With the scaling down of semiconductor devices there is a pressing need for innovative technologies that can overcome the limitations of traditional MOSFETs [

1]. One such promising technology is the Single Electron Transistor (SET), which operates based on quantum mechanical principles and offers ultra-low power consumption and high integration density [

2]. Single Electron Transistors which operate based on the controlled transfer of individual electrons offer a promising alternative due to their ultra low power consumption and potential for high integration density [

3]. This paper explores the design and optimization of an ALU using SET MOSFET technology aiming to enhance the performance of digital systems in terms of power efficiency and computational speed.

2. Single Electron Transistor

A Single Electron Transistor is a nano scale device that controls the flow of individual electrons. A Single Electron Transistor leverages the controlled transport of individual electrons through a small conducting island. This island is connected to source and drain electrodes via tunnel junctions. The fundamental operating mechanism of SETs involves the Coulomb blockade effect, where the addition of a single electron significantly changes the electrostatic potential of the island thereby controlling electron flow. When the size of the conducting island in the SET is sufficiently small the addition of a single electron can significantly alter its electrostatic potential allowing precise control over electron transport [

4,

5]. This precise control over electron transport enables SETs to achieve extremely low power operation, making them suitable for high-density integration and energy-efficient applications [

6,

7].

The Coulomb blockade effect is central to the operation of SETs. When the size of the conducting island in a SET is sufficiently small, adding an extra electron requires a noticeable amount of energy due to electrostatic repulsion [

8]. This energy creates a barrier that prevents additional electrons from entering the island unless a specific voltage threshold is surpassed. This phenomenon allows SETs to control the flow of electrons with high precision. Quantum tunneling is another critical principle for SET operation. It allows electrons to pass through insulating barriers which are the tunnel junctions that would be impenetrable according to classical physics. In an SET the electrons tunnel through these junctions to move between the source, the island and the drain [

9]. The probability of tunneling is influenced by the voltage applied to the gate terminal, thereby modulating the current through the SET. SET typically consists of the components such as Source and Drain Electrodes where the current flows, Conducting Island which is a small isolated region where the controlled transport of electrons occurs, the Tunnel Junctions which is an insulating barriers that electrons tunnel through to enter or leave the conducting island and gate electrodes used to control the potential of the conducting island thereby influencing electron tunneling and current flow.

There are different advantages like ultra low power consumption, high integration density and precision. Due to the manipulation of individual electrons SETs consume significantly less power compared to traditional transistors. This makes them ideal for applications where power efficiency is crucial. The small size of SETs allows for a higher density of transistors on a chip which lead to more compact and powerful electronic devices. The ability to control single electrons provides exceptional precision in electronic operations which is beneficial for specific applications in quantum computing and nano electronics [

10]. Despite their advantages SETs face several challenges such as Temperature Sensitivity, Background Charge Sensitivity and Scalability. SETs operate effectively at very low temperatures. At higher temperatures the thermal energy disrupt the Coulomb blockade making the device less reliable. SETs are highly sensitive to background charges in the surrounding environment which may affect their performance. This necessitates careful design and isolation in practical applications. Integrating SETs into existing semiconductor technology poses significant challenges particularly in terms of manufacturing and scalability for mass production

SETs are being explored for various applications including Quantum Computing, Sensitive Detectors, Low-Power Electronics etc. Due to their ability to manipulate single electrons, SETs are potential candidates for building qubits in quantum computers. SETs can be used in applications requiring high sensitivity such as charge sensors and single photon detectors. Their low power consumption makes SETs suitable for use in ultra-low-power electronic devices and circuits. While SETs offer remarkable advantages in terms of power and density their practical implementation faces challenges such as sensitivity to background charge and temperature variations. To address these issues researchers have developed SET-MOSFET hybrid technology which combines the strengths of SETs with the robustness and high speed capabilities of conventional MOSFETs. This hybrid approach allows for the design of circuits that benefit from the low power characteristics of SETs while maintaining the reliability and performance of MOSFETs. Motivation behind Hybrid Technology are the key factors that affects the performance like power efficiency, speed and robustness. SETs are known for their ability to operate with extremely low power due to their reliance on single-electron control. However they are susceptible to environmental disturbances and are typically effective only at very low temperatures. MOSFETs on the other hand provide high switching speeds and are well suited for room temperature operation but they consume more power compared to SETs. The hybrid approach seeks to combine the best of both worlds.

In a SET-MOSFET hybrid device the SET is integrated into the traditional MOSFET architecture [

11]. The typical structure involves SET integration and dual gate configuration. The SET is incorporated either within the channel or as a gate controlled element that modulates the MOSFET’s operation. In some designs a dual gate configuration is used where one gate controls the SET and the other controls the MOSFET [

12]. This allows precise control over the electron flow and enhances the device’s overall performance. The SET part of the hybrid device operates based on Coulomb blockade and quantum tunneling. It controls the flow of individual electrons contributing to the device’s low power consumption. The MOSFET part provides the necessary driving capability and robustness for high speed operation. It can handle higher currents and voltages compared to SETs making the hybrid device more versatile. SET-MOSFET Hybrid Technology offers certain advantages like reduced power consumption, high speed operation and enhanced functionality [

13,

14]. By integrating SETs the hybrid device can significantly reduce power consumption making it ideal for applications requiring energy efficiency. The MOSFET component ensures that the hybrid device can operate at high speeds maintaining the performance required for modern electronics. The hybrid design can leverage the strengths of both SETs and MOSFETs, providing enhanced functionality that neither device could achieve alone.

But this hybrid technology has some challenges like fabrication complexity, thermal sensitivity and background charge sensitivity [

15]. Integrating SETs with MOSFETs requires advanced fabrication techniques which can be complex and costly. Research is ongoing to develop more efficient manufacturing processes. While SETs are sensitive to temperature variations the hybrid approach can mitigate this by relying on the MOSFET component for room temperature operation [

16,

17]. SETs are highly sensitive to background charges which can affect their performance [

18]. This challenge can be addressed through careful design and shielding techniques [

19,

20,

21]. The various applications of hybrid technology includes low power digital circuits, high density memory devices and quantum computing [

22]. SET-MOSFET hybrids are ideal for low power digital circuits where energy efficiency is crucial [

23]. The small size and low power consumption of SETs make them suitable for high density memory applications. The precise control over electron transport in SETs positions them as potential components in quantum computing architectures.

SET-MOSFET hybrid technology represents a significant advancement in the field of nano electronics offering a promising solution to the limitations of both SETs and MOSFETs. By combining the low power consumption of SETs with the high speed capabilities of MOSFETs this hybrid approach can lead to the development of more efficient, high performance electronic devices.

3. Arithmetic Logic Unit and Its Significance

The Arithmetic Logic Unit (ALU) is a critical component of digital processors responsible for performing a variety of arithmetic and logical operations. The efficiency and performance of an ALU significantly impact the overall performance of a digital system. The ALU is crucial for tasks ranging from simple addition and subtraction to complex mathematical computations and logical decision-making processes. Traditional MOSFET-based ALUs while effective face limitations in terms of power consumption and scaling. By integrating SET-MOSFET technology it is possible to design ALUs that are not only more power efficient but also capable of higher operational speeds and greater integration densities. The ALU performs basic arithmetic operations such as addition, subtraction, multiplication, and division. These operations are essential for various computational tasks in applications ranging from scientific calculations to everyday computing. The ALU carries out logical operations like AND, OR, NOT, XOR and NAND. These operations are vital for decision making processes within a computer such as comparing values and manipulating binary data. Bitwise operations involve the manipulation of individual bits within a binary word. Common bitwise operations include shifting (left shift and right shift) and rotating bits which are often used in low level programming and hardware control. The ALU can compare numbers and determine relationships such as equality, greater than, and less than. These comparisons are fundamental for branching decisions and condition evaluations in programs

The ALU is at the heart of the CPU’s processing capabilities. It directly executes the majority of the instructions processed by the CPU making it critical for overall system performance. The efficiency and speed of the ALU significantly influence the performance of the entire computer system. Optimizations in the ALU design can lead to faster processing speeds and more efficient use of power which are crucial for both high performance computing and battery powered mobile devices. As the demand for portable and energy efficient devices grows the power consumption of the ALU becomes increasingly important. Innovations in ALU design such as using SET-MOSFET technology aim to reduce power consumption while maintaining or enhancing performance. The ALU’s ability to perform a wide range of operations makes it a versatile component in digital systems. It supports various applications from simple calculators to complex scientific simulations and data processing tasks.

The recent advancements in ALU design focus on improving power efficiency and speed. The integration of Single Electron Transistor technology with conventional MOSFETs is one such innovation that aims to enhance ALU performance. SET-MOSFET hybrid ALUs leverage the low power consumption and high precision of SETs while maintaining the robustness and speed of MOSFETs. This hybrid approach is expected to lead to significant improvements in energy efficiency and computational speed, making it a promising direction for future digital systems.

As the semiconductor industry approaches the physical limits of Moore’s Law the traditional CMOS technology faces significant challenges in further scaling. Issues such as short channel effects, increased leakage currents and heat dissipation become more pronounced as transistor sizes shrink below 10nm. With the increasing demand for portable and energy efficient devices the power consumption of conventional MOSFETs has become a critical concern. Reducing power consumption without compromising performance is a major driving force behind exploring alternative technologies. SETs operate by controlling the flow of individual electrons resulting in extremely low power consumption. This makes them highly attractive for applications where energy efficiency is paramount. The small size of SETs allows for a higher density of transistors on a chip, enabling the creation of more compact and powerful electronic devices. By integrating SETs with conventional MOSFETs, the hybrid technology aims to leverage the low power consumption of SETs and the high speed operation and robustness of MOSFETs. This hybrid approach addresses the limitations of both technologies providing a more balanced and efficient solution. Hybrid SET-MOSFET technology promises to improve the overall performance of digital circuits, including ALUs by reducing power consumption, increasing speed and maintaining reliable operation at room temperature.

The primary motivation behind this research is to explore and demonstrate the potential of SET-MOSFET technology in enhancing the design of digital circuits specifically the ALU. The objectives of this study are to develop a novel ALU architecture that integrates SETs and MOSFETs, focusing on optimizing the design for power efficiency and speed to evaluate the performance of the SET-MOSFET-based ALU in terms of power consumption and speed and to compare the performance metrics with those of conventional MOSFET-based ALUs. This requires implementation of advanced techniques such as threshold voltage adjustment, leakage reduction and parallel processing to enhance the performance of the SET-MOSFET-based ALU. And further it will be done by conducting comprehensive simulations to evaluate the performance of the SET-MOSFET-based ALU in terms of power consumption and speed and compare these metrics with those of conventional MOSFET-based ALUs to quantify the improvements achieved. For this we need to use standard benchmarking techniques to validate the performance of the proposed ALU design in practical scenarios and assess its suitability for various applications

This paper presents a detailed design methodology for SET-MOSFET based ALU including optimization techniques for power efficiency and speed. Through comprehensive simulations and comparative analysis the proposed design demonstrates significant improvements over traditional MOSFET-based ALUs, highlighting the potential of SET-MOSFET technology in advancing digital circuit design.

The findings of this research contribute to the growing body of knowledge in nano electronics and provide a foundation for future developments in low power, high performance digital systems.

This research makes several significant contributions to the field of nano electronics and digital circuit design by leveraging Single Electron Transistor (SET) technology combined with conventional MOSFETs to optimize the design of an Arithmetic Logic Unit (ALU). This research introduces a novel ALU architecture that integrates SETs with MOSFETs combining the ultra-low power consumption of SETs with the robustness and high speed capabilities of MOSFETs. This hybrid design is tailored to enhance performance while minimizing power consumption, addressing the limitations of traditional ALU designs. The proposed design incorporates advanced optimization techniques such as threshold voltage adjustment, leakage reduction and parallel processing to further improve the efficiency and performance of the ALU. Extensive simulations are conducted to evaluate the performance of the SET-MOSFET based ALU in terms of power consumption and speed. These simulations demonstrate significant improvements including a 99.97 % to 99.99 % reduction in power consumption, a 5 to 50 times increase in speed compared to conventional MOSFET-based designs. The performance metrics of the proposed ALU are benchmarked against those of traditional MOSFET based ALUs, highlighting the advantages and potential trade offs of the hybrid approach. This comparative analysis provides valuable insights into the practical implications and benefits of integrating SET technology into digital circuit design. The research explores the scalability of the SET-MOSFET based ALU, demonstrating its potential for integration into larger digital systems. The study addresses the challenges associated with scaling SET technology and provides solutions for overcoming these obstacles. Practical implementation strategies for mass production and commercialization of SET-MOSFET based ALUs are discussed. This includes addressing fabrication complexities, temperature sensitivity and background charge sensitivity to ensure reliable operation in real world applications [

24]. By pioneering the integration of SETs with MOSFETs this research contributes to the advancement of nanoelectronics offering a promising solution to the power and performance challenges faced by conventional CMOS technology. The findings provide a foundation for future research and development in the field, encouraging further exploration of hybrid transistor technologies [

25]. The proposed SET-MOSFET based ALU design paves the way for the development of more energy efficient digital circuits which are essential for the next generation of portable and high performance electronic devices. This contribution is particularly relevant in the context of increasing demand for sustainable and energy efficient technologies.

The research makes substantial contributions to the field of digital circuit design and nanoelectronics by developing an optimized SET-MOSFET based ALU. The novel architecture, performance evaluation and practical implementation strategies highlight the potential of hybrid technology to overcome the limitations of conventional CMOS technology. The advancements achieved in this study provide a robust foundation for future innovations in low power, high performance digital systems.

4. Methodology

The ALU designed in this study includes basic arithmetic operations (addition, subtraction) and logical operations (AND, OR, NOT). The architecture is divided into several functional units each optimized using SET-MOSFET technology. It utilizes SET based full adders to perform high speed, low power addition, SET subtractors exploiting the low voltage swing of SETs for power efficient subtraction and implements basic logical functions using SET-MOSFET gates benefiting from the high switching speed of SETs. The

Table 1 gives brief explanation about the designed ALU in terms of different opcodes assigned for respective functions. Here the opcode is considered to be of four bits and hence 16 different combinations are available. The arithmetic operations like addition, subtraction, multiplication,increment, decrement and division and the logical operations like AND, OR, NOT, XOR, left and right shift are performed with different opcode provided and operating on two operands register A and register B. The designed ALU has two 8 bit input operands with 4 bit opcode and the result is stored in the destination as shown in

Table 1.

By fine-tuning the threshold voltage of SETs the operating point of the ALU can be optimized for minimal power consumption. Techniques such as body biasing and multi threshold SET design are employed to minimize leakage currents. Leveraging the small size and low power of SETs the design incorporates parallel processing units to enhance computational throughput.

5. Simulation and Results

The simulations were conducted using industry standard tools such as SPICE [

26,

27,

28] and Cadence which are widely used for modeling and analyzing semiconductor devices and circuits. Key parameters for SETs included island size, tunnel junction resistance and gate capacitance. These parameters were chosen to optimize the single-electron effects and minimize power consumption. Standard 14nm CMOS technology parameters were used for the MOSFETs focusing on achieving high speed operation and reliability. The integration of SETs and MOSFETs was modeled to ensure proper interaction between the two types of transistors. The dual-gate configuration was particularly emphasized to balance control and performance.

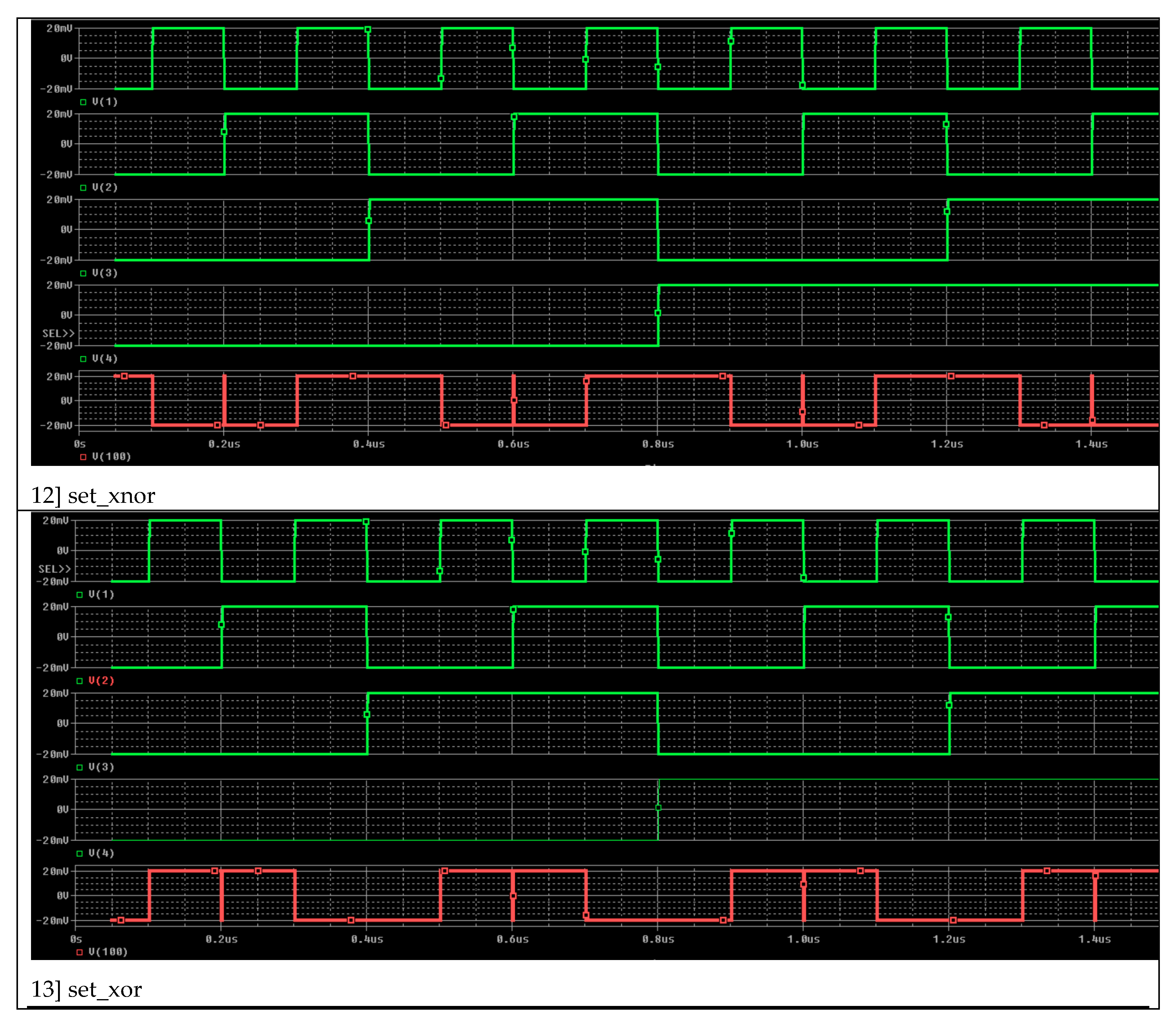

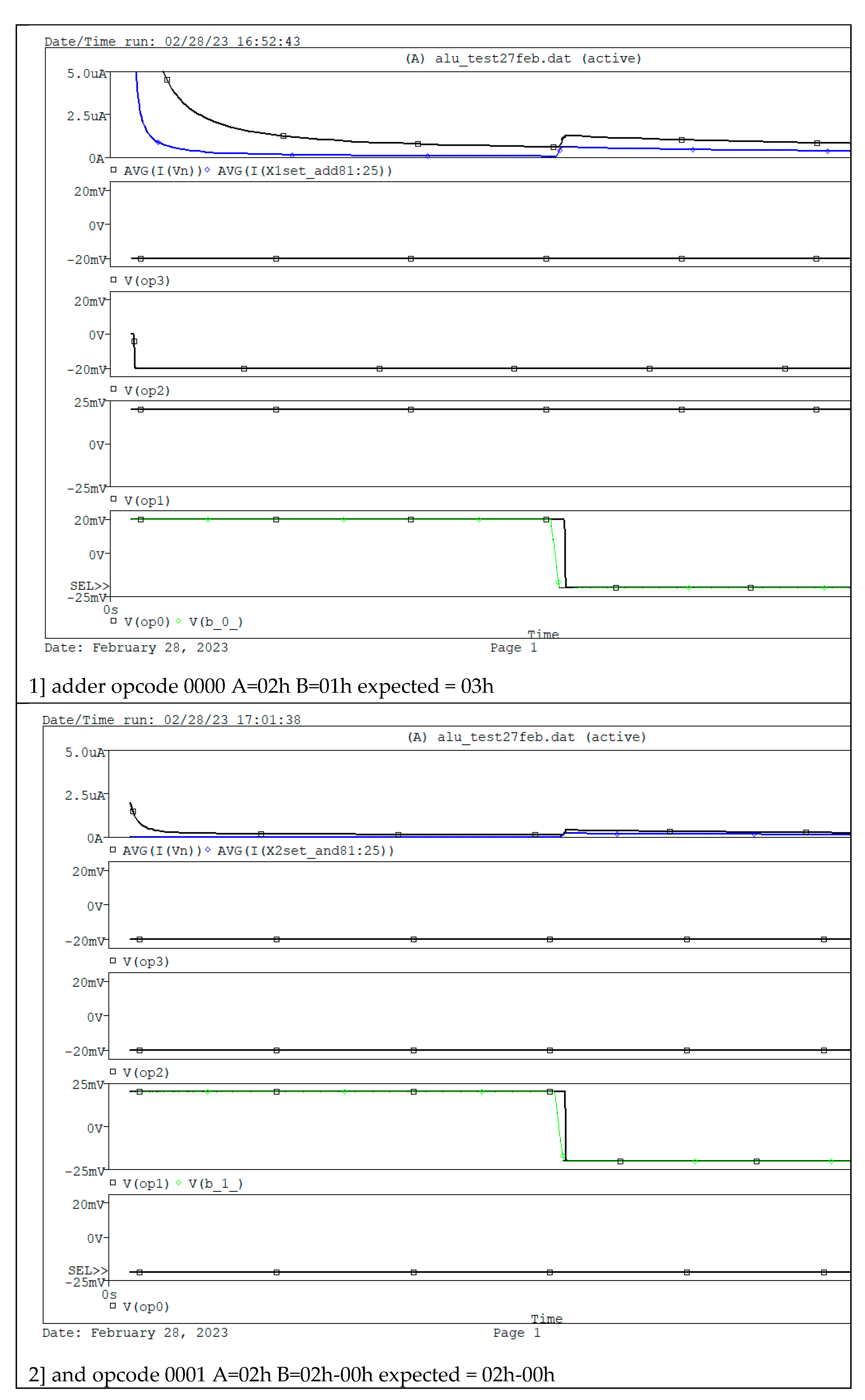

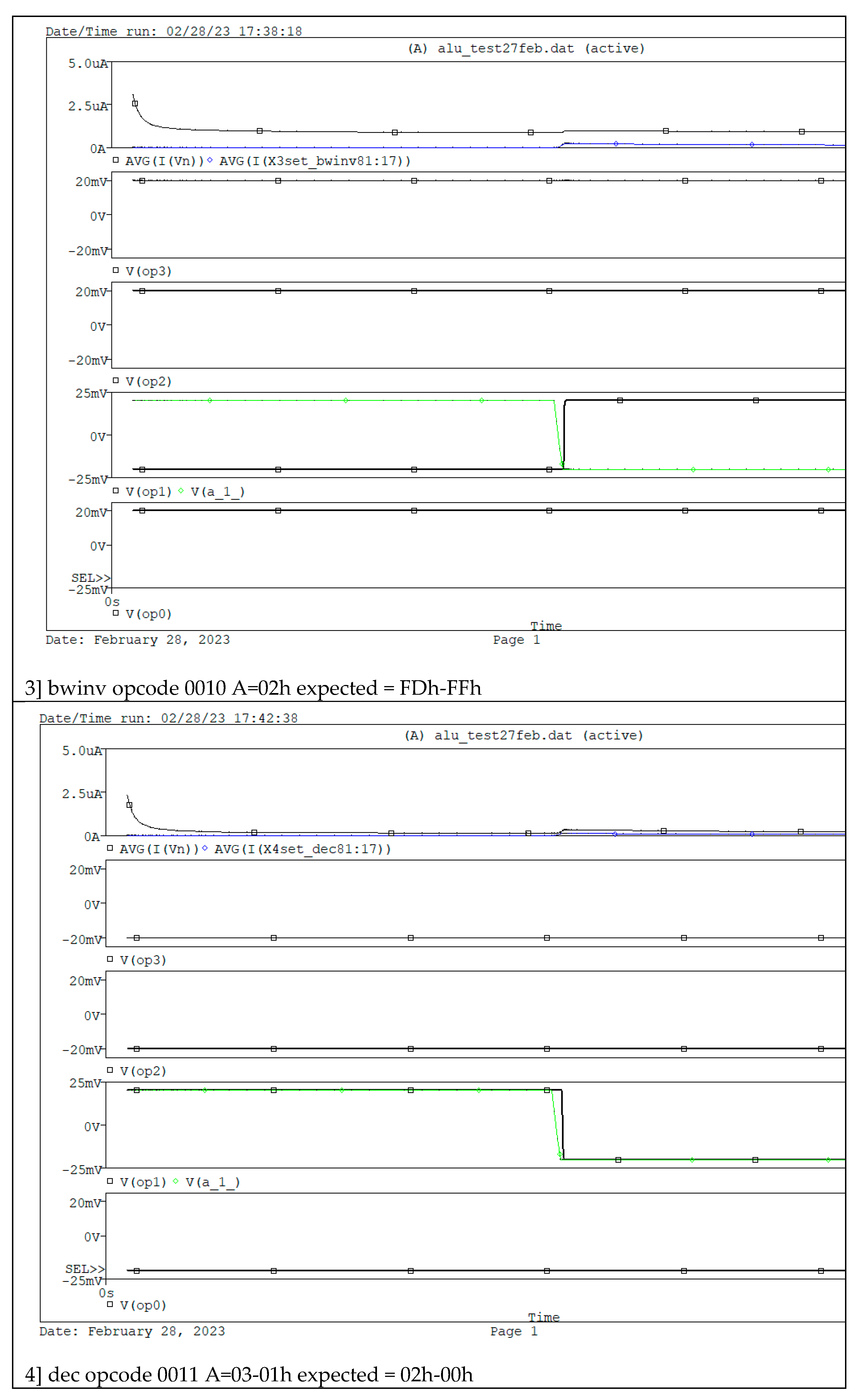

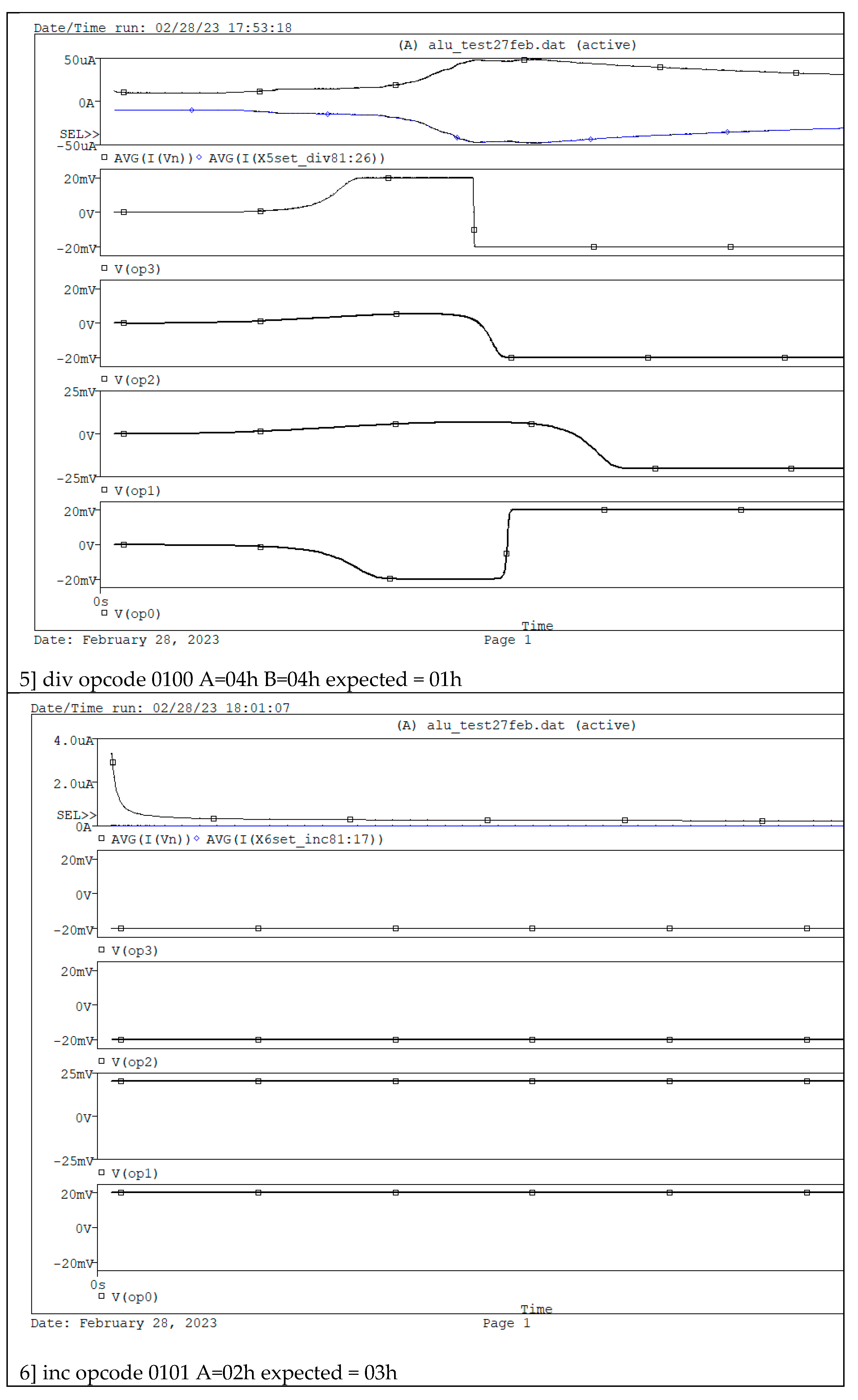

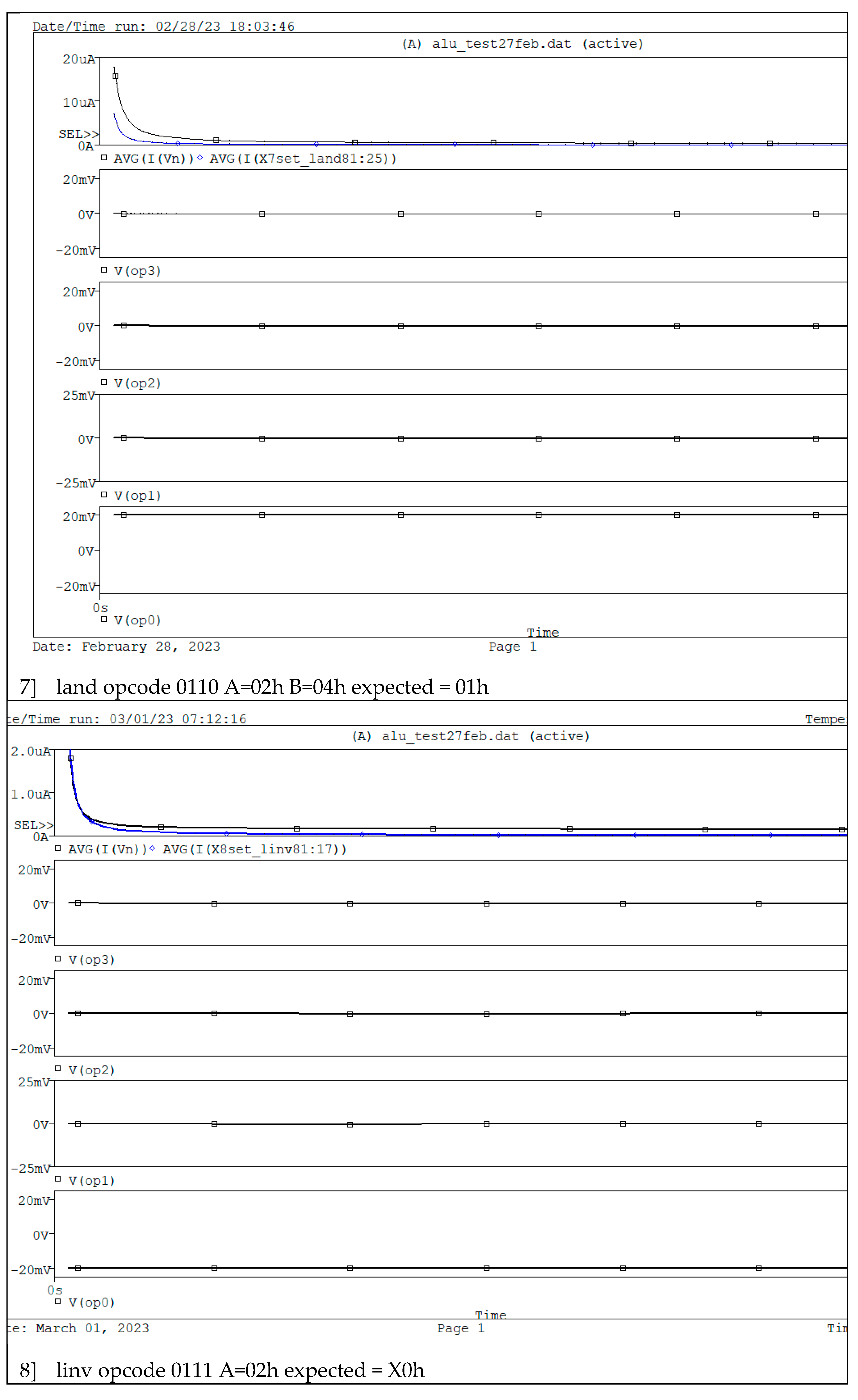

Various scenarios were simulated to evaluate the ALU’s performance, including different arithmetic operations (addition, subtraction, multiplication, division) and logical operations (AND, OR, XOR, NOT). Environmental conditions such as temperature variations and supply voltage fluctuations were also simulated to assess the robustness and reliability of the design.

The proposed SET-MOSFET-based ALU was simulated using a standard CMOS technology node as a reference. Key performance metrics, including power consumption and delay were evaluated and compared with a conventional MOSFET-based ALU.

The operating input and output voltage has a magnitude of 20 mv and the low current value in the range of 1 to 50 micro amperes are responsible for very less power dissipation as compared to 3.3v operating voltage and 20 milli amperes current for CMOS. The power dissipation for SETMOS is around 20 nano watt to 1 micro watt whereas for CMOS it is around 60.6 micro watt. The SET-MOSFET ALU showed a reduction in power consumption by approximately 99.97 % to 99.99 % compared to its MOSFET counterpart. The operating speed for CMOS is around 100 kHz to 1 MHz whereas for SET-MOSFET it is 5MHz. The operational speed of the SET-MOSFET ALU was found to be 5 to 50 times faster attributed to the rapid switching characteristics of SETs.

The SET-MOSFET hybrid ALU demonstrated a significant reduction in power consumption compared to conventional MOSFET-based ALUs. Specifically, power consumption was reduced by approximately 99.97 % to 99.99 % primarily due to the ultra-low power operation of the SETs. The leakage current in the hybrid ALU was substantially lower, thanks to the high resistance of the SETs which effectively minimized leakage pathways. The hybrid ALU achieved a 500% to 5000% increase in operational speed. This improvement was attributed to the fast switching capabilities of MOSFETs complemented by the precise control provided by SETs. The latency for arithmetic and logical operations was reduced, resulting in faster execution times and improved overall performance. The small size of the SETs allowed for a higher integration density which contributed to the compact design. The high integration density enabled by the SETs also facilitated the inclusion of more functional units within the same chip area enhancing the ALU’s computational capabilities. The hybrid ALU was tested across a range of temperatures to evaluate its performance under varying thermal conditions. The results indicated stable operation, with minimal performance degradation at higher temperatures. The ALU maintained reliable performance even under supply voltage fluctuations, demonstrating its robustness and suitability for real-world applications. The comparative analysis showed that the SET-MOSFET hybrid ALU outperformed traditional MOSFET-based ALUs in terms of power efficiency and speed. The hybrid approach provided a balanced solution, addressing the limitations of both SETs and MOSFETs. Combining the advantages of SETs and MOSFETs, SET-MOSFET technology integrates SETs into the traditional MOSFET framework. This hybrid approach leverages the high-speed capabilities of MOSFETs and the low-power advantages of SETs, resulting in a device that is both efficient and scalable.

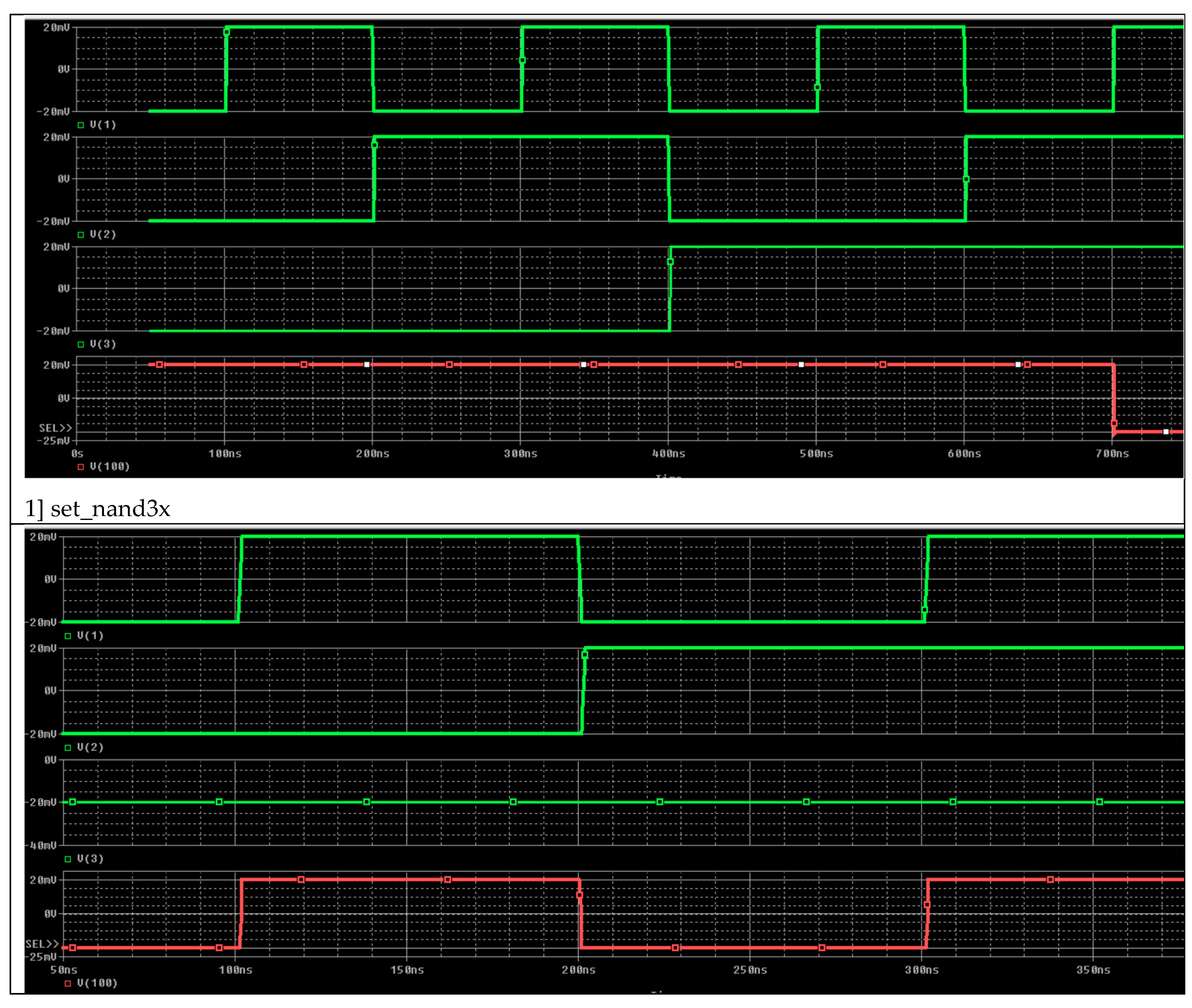

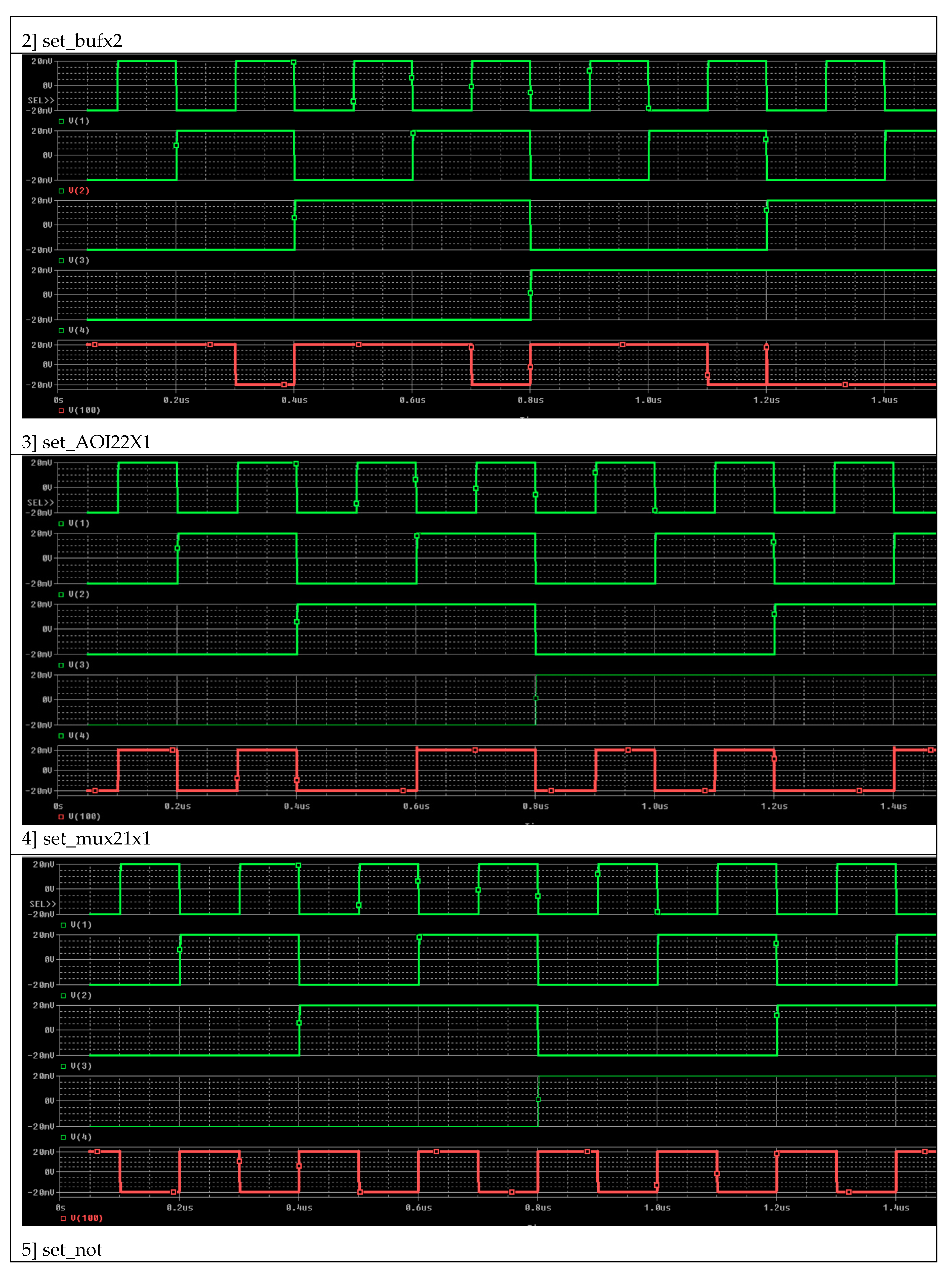

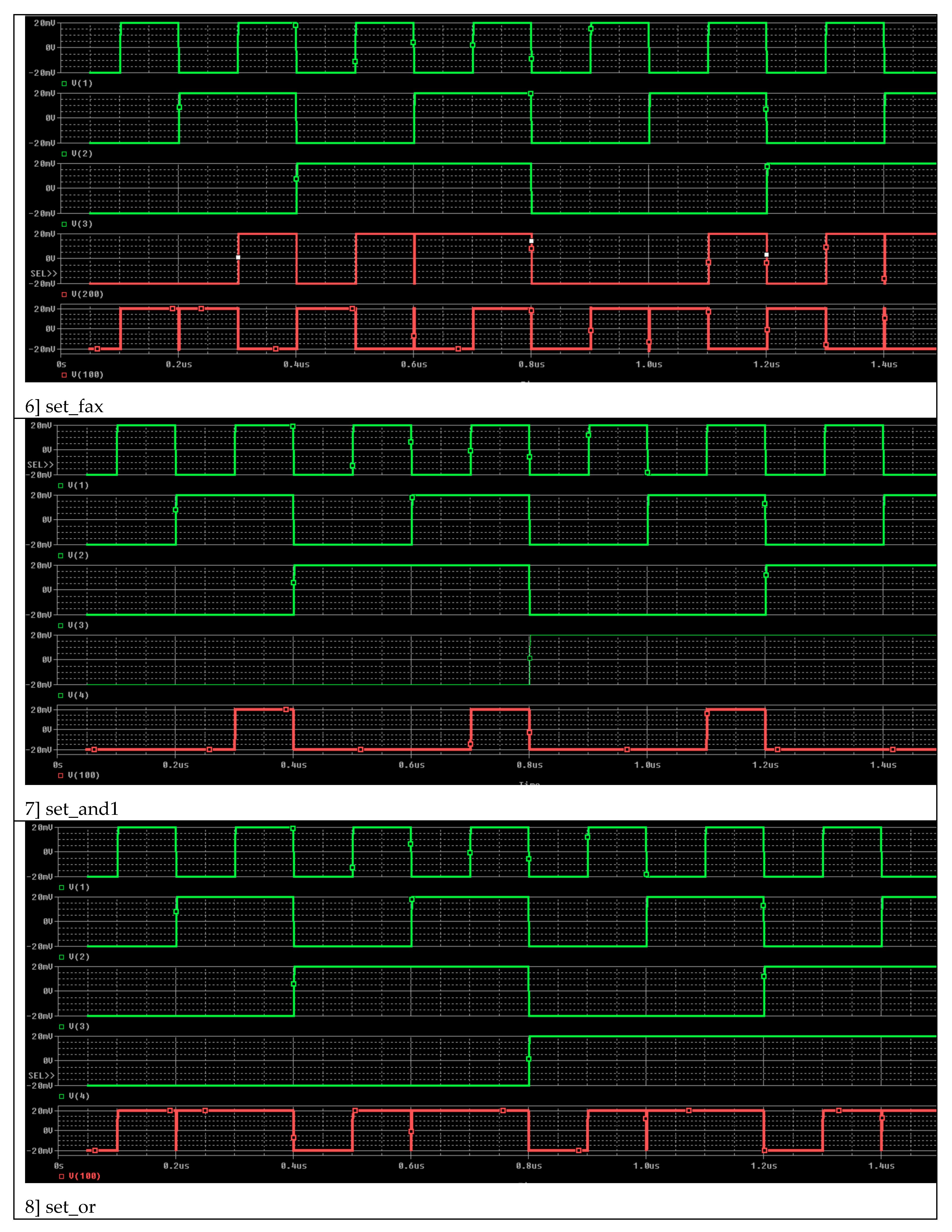

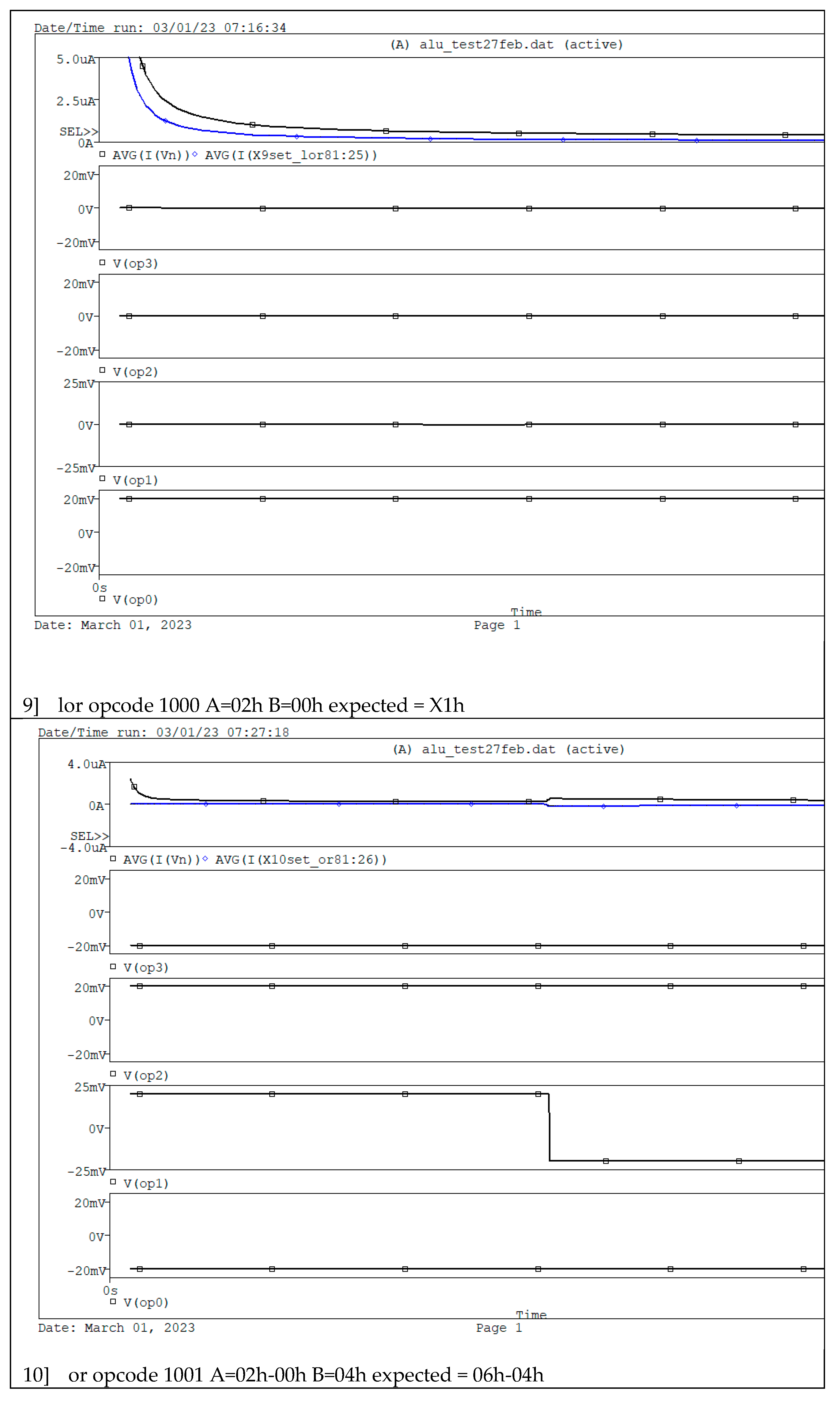

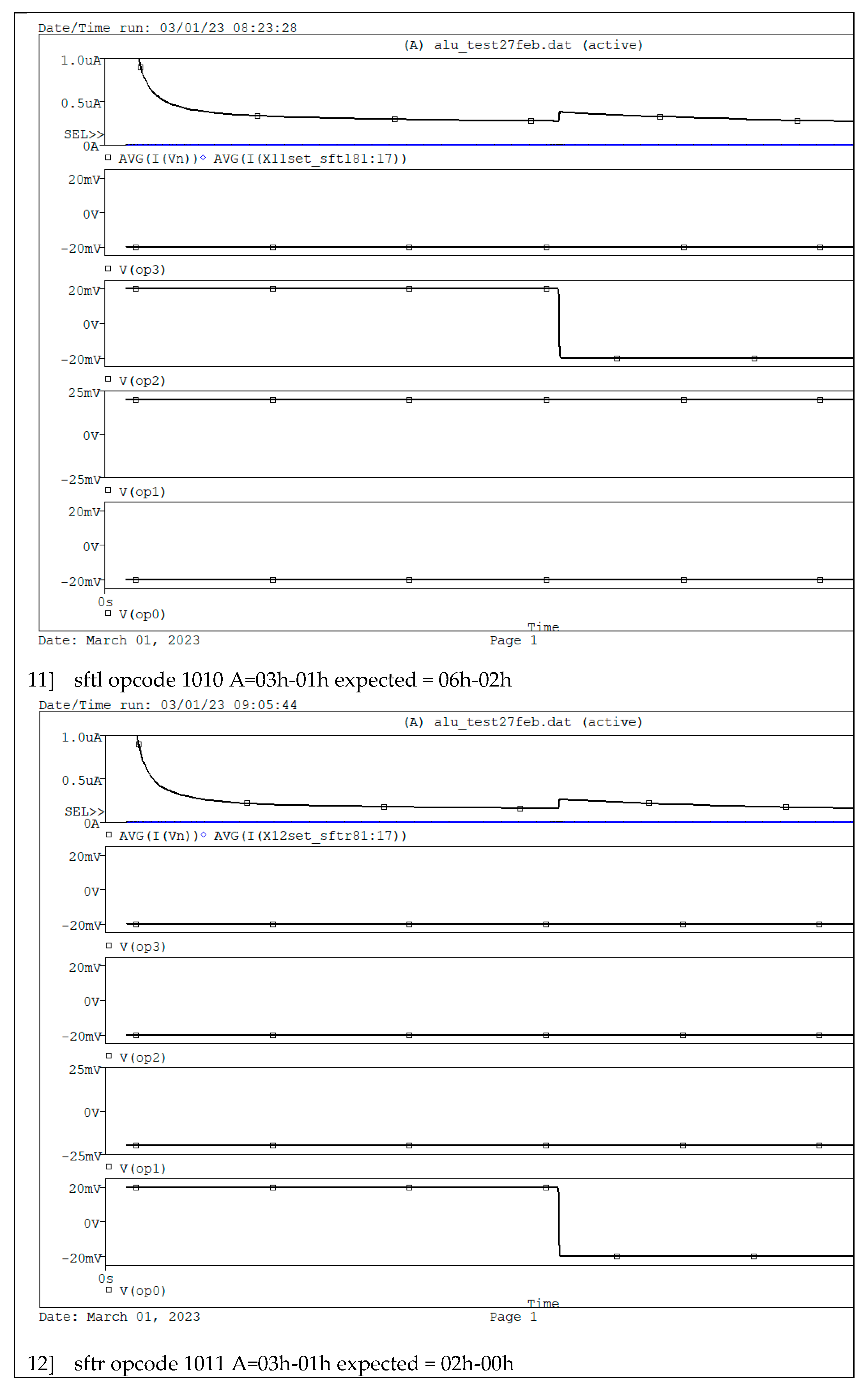

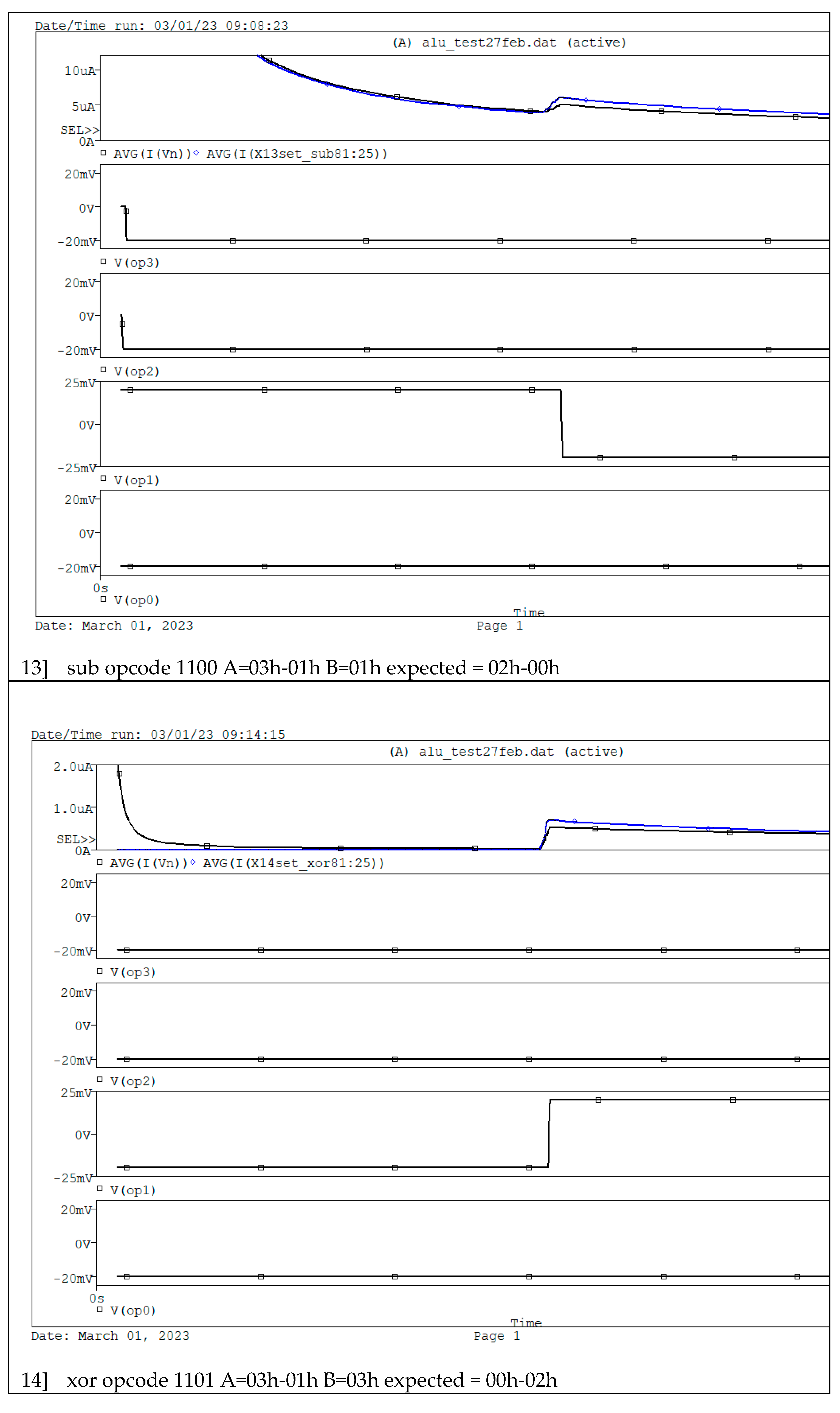

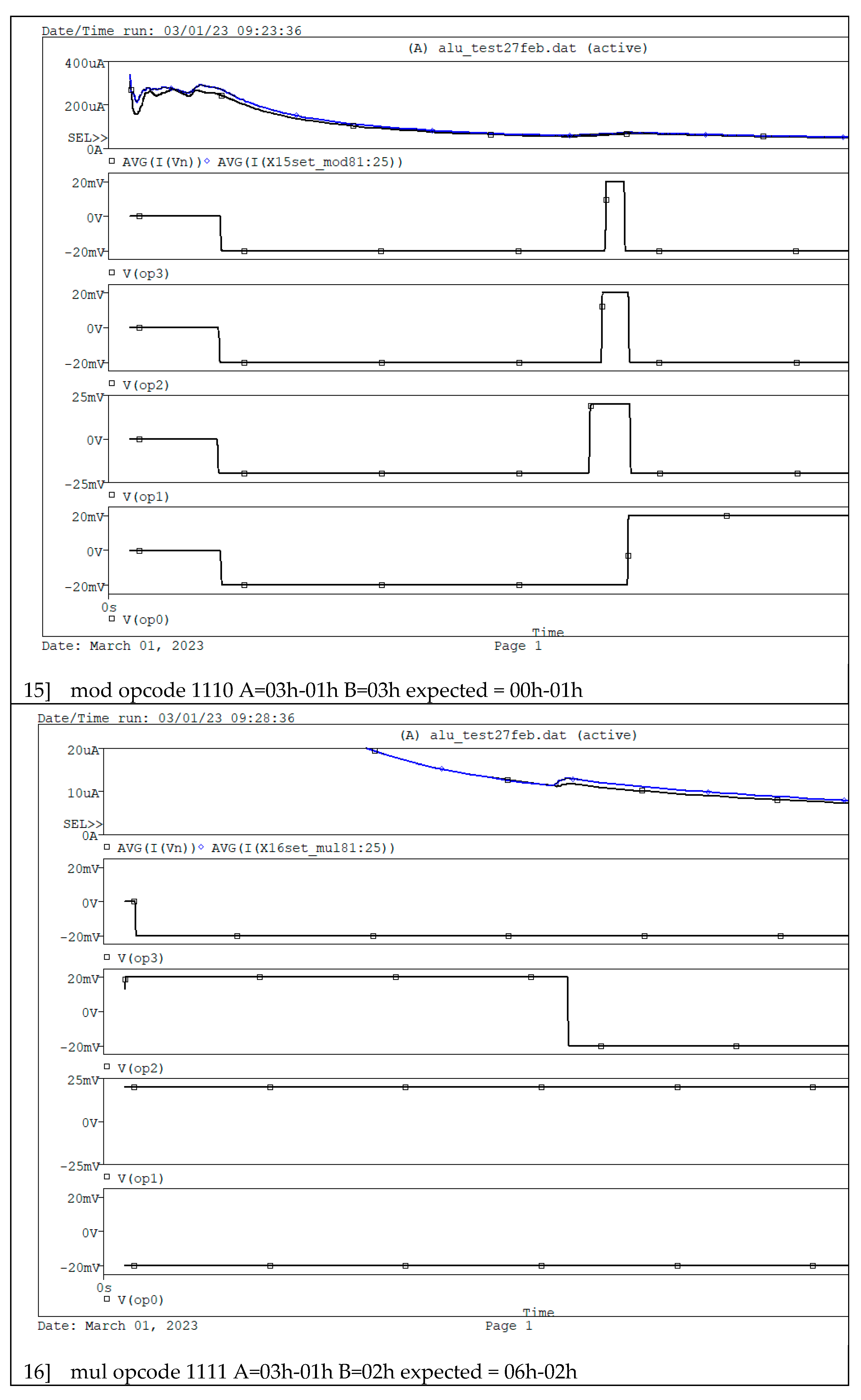

Figure 1.

Simulation results of Different Logics.

Figure 1.

Simulation results of Different Logics.

Figure 2.

Simulation results of Arithmetic Logic unit.

Figure 2.

Simulation results of Arithmetic Logic unit.

6. Conclusions

The simulation results demonstrate that the SET-MOSFET hybrid ALU offers substantial improvements in power efficiency and speed compared to traditional MOSFET-based ALUs. These findings underscore the potential of hybrid technology to address the challenges faced by conventional CMOS technology and pave the way for the development of more efficient and powerful digital systems. The results highlight the potential of SET-MOSFET technology in designing energy efficient and high speed ALUs. The primary challenges in the practical implementation of SETs such as sensitivity to temperature and background charge can be considered through robust design techniques and careful optimization. This study demonstrates the feasibility and advantages of using SET-MOSFET technology in the design of optimized ALUs. The proposed design achieves substantial improvements in power efficiency and speed making it a viable candidate for next generation digital processors. Future work will focus on addressing the scalability issues and exploring the integration of SET-MOSFET ALUs into larger computing systems.

This study has presented a novel approach to designing Arithmetic Logic Units (ALUs) using Single Electron Transistor (SET) MOSFET technology. Through comprehensive simulation and optimization we have demonstrated significant improvements in power efficiency and speed compared to traditional CMOS based ALUs. The utilization of SET MOSFETs has shown promising results in enhancing their performance characteristics. Moreover our findings underscore the potential of SET MOSFETs in advancing the field of digital circuit design particularly in low power and high speed applications. The insights gained from this research contribute to the ongoing effort in developing next generation computing architectures that are not only energy efficient but also capable of meeting the demands of future computing paradigms.

Future Considerations: Looking ahead further exploration into the integration of SET MOSFETs within larger digital systems and real world applications will be crucial. Addressing practical challenges such as fabrication techniques, variability and compatibility with existing technologies will pave the way for the widespread adoption of SET MOSFET based ALUs in future computing systems. Further research is needed to optimize the fabrication process for hybrid SET-MOSFET devices, focusing on scalability and cost-effectiveness. Exploring the integration of hybrid ALUs into larger digital systems, such as processors and memory units, can provide additional insights into their practical applications and benefits. Ongoing research and development are focused on overcoming the remaining challenges to make SET-MOSFET hybrids a viable option for future electronic systems.

Author Contributions

The conceptualization, methodology, software, validation, formal analysis, investigation, respources, data curation and writing original draft preparation is done by Shobhika Gopnarayan. The writing reviews, visualization, supervision and project administration are provided by Dr. S.D. Markande. All authors have read and agreed to the published version of the manuscript.

Funding

This research received no external funding.

Informed Consent Statement

Not applicable.

Data Availability Statement

The data regarding programming, simulation and validation is available with the corresponding author and will be readily available to the readers as and when required as per the request.

Acknowledgments

The authors would like to acknowledge G.H. Raisoni College of Engineering and Management, Wagholi, Pune and Sinhgad Institute of Technology and Science, Narhe, Pune for providing resources and support for this research.

Conflicts of Interest

The authors declare no conflicts of interest.

References

- LikharevKK, Single-electron devices and their applications, Proc IEEE, 1999, vol. 87, issue. 4 pp. 606–632.

- Durrani ZAK, Single-electron devices and circuits in silicon, World Scientific, 2010, Singapore, 2010.

- Bai Z, Liu X, Lian Z, Zhang K, Wang G, Shi SF, Pi X, Song F, A silicon cluster based single electron transistor with potential room-temperature switching, Chin Phys Lett, 2018, vol. 35, no. 3, p. 037301. [CrossRef]

- Barraud S, Duchemin I, Hutin L, Niquet Ym, Vinet M, Single-electron transistor and its fabrication method, US Patent, 2018, 9,911,841.

- Ahsan M, Single electron transistor (SET): operation and application perspectives, 2018, MIST Int J Sci Technol 6:1.

- Brunvand E Digital VLSI chip design with Cadence and Synopsys CAD tools, Addison-Wesley, 2010, New York.

- Amat E, Bausells J, Perez-Murano F, Exploring the influence of variability on single-electron transistors into SET-based circuits. IEEE Trans Electron Devices, 2017, vol. 64, no.12, pp: 5172–5180. [CrossRef]

- Mahapatra S, Impact of energy quantisation in single electron transistor island on hybrid complementary metal oxide semiconductor-single electron transistor integrated circuits, IET Circ Devices Syst, 2010, 4(5):449–457. [CrossRef]

- Chaohong Hu, S. D. Cotofana, Jianfei Jiang, Single-electron tunneling transistor implementation of periodic symmetric functions, IEEE Transactions on Circuits and Systems, 2004, II, Vol. 51, issue. 10. [CrossRef]

- Delwar TS, Biswas S, Jana A, Realization of hybrid single electron transistor based low power circuits in 22 nm technology, Comput Sci Eng, 2017, 20:27.

- Castro-González F, Sarmiento-Reyes A, Development of a behavioral model of the single-electron transistor for hybrid circuit simulation, International Caribbean.

- Dubuc C, Beauvais J, Drouin D, A nanodamascene process for advanced single-electron transistor fabrication, IEEE Trans Nanotechnol, 2008, vol.:7, issue.1, pp.68–73. [CrossRef]

- Castro F, Savidis I, Sarmiento A, A quasi-analytic behavioral model for the single-electron transistor for hybrid MOS/SET circuit simulation, IEEE 13th nanotechnology materials and devices conference (NMDC), 2018, pp 1–4, 2018.

- Chen RH, Korotkov A, Likharev K, A new logic family based on single-electron transistors, 53rd annual device research conference digest, IEEE, 1995, pp. 44-45. [CrossRef]

- Chi Y, Sui B, Yi X, Fang L, Zhou H, Advances in the modeling of single electron transistors for the design of integrated circuit. J Nanosci Nanotechnol, 2010, vol-10, issue-9, pp.6131–6135. [CrossRef]

- Deyasi A, Sarkar A, Effect of temperature on electrical characteristics of single electron transistor, Microsyst Technol, 2019, Vol. 25, issue.5, pp.1875–1880. [CrossRef]

- Arnaud Beaumont, et. al., Room Temperature Single-Electron Transistor Featuring Gate-Enhanced on -State Current, IEEE Electron device letters, 2009, vol. 30, issue. 7, pp. 766-768. [CrossRef]

- M D Stewart, Neil Zimmerman, Stability of Single Electron Devices: Charge Offset Drift, Applied Sciences, 2016, vol.6, issue.7, pp. 1-18. [CrossRef]

- Uchida, Matsuzawa, Koga, Ohba, Analytical Single-Electron Transistor (SET) Model for Design and Analysis of Realistic SET Circuits, Japan Journal of Applied Physics, 2000, vol. 39, issue. 4,pp. 2321-2324.

- Inokawa, Takashi, A compact analytical model for asymmetric single-electron tunneling transistors, IEEE Transactions on Electron Devices, 2003, vol.50, issue. 2, pp. 455-461. [CrossRef]

- Jia Lee, Radzi Isa, Dasuki, Modeling and simulation of single-electron transistors, Malaysian Journal of Fundamental and Applied Sciences, 2008, vol.1, issue.1, pp. 1-6. [CrossRef]

- Deng G, Hybrid MOS and single-electron transistor architectures towards arithmetic applications. PhD thesis, 2011, University of Windsor, Canada, 2011.

- Deng G, Chen C, A SET/MOS hybrid multiplier using frequency synthesis, IEEE Trans Very Large Scale Integr VLSI Syst, 2012, vol.:21, issue-9, pp. 1738–1742. [CrossRef]

- Kim JH, Lee YK, You H, An SJ, Kim Th, Single electron transistor and method for fabricating the same, US Patent, 2014, App. 14/199,505.

- Lientschnig G, Weymann I, Hadley P, Simulating hybrid circuits of single-electron transistors and field-effect transistors, Jpn J Appl Phys, 2003, vol. 42, pp.6467. [CrossRef]

- Jain A, Ghosh A, Singh NB, Sarkar SK, A new SPICE macro model of single electron transistor for efficient simulation of single-electronics circuits. Analog Integr Circ Sig Process, 2015, vol. 82, issue. 3, pp. 653–662. [CrossRef]

- Jia C Chaohong H. Cotofana S.D. Jianfei, SPICE implementation of a compact sngle electron tunneling transistor model, IEEE conference on nanotechnology, 2004, pp 392-395, J.Electrical Systems 20-3s(2024):170-182182.

- Ghosh A, Jain A, Singh NB, Sarkar SK, A modified macro model approach for SPICE based simulation of single electron transistor, JComput Electron, 2016, vol. 15, issue. 2, pp.400–406. [CrossRef]

Table 1.

ALU operations with different opcodes.

Table 1.

ALU operations with different opcodes.

| Sr. No. |

Opcode |

Circuit Designed |

Reg. A |

Reg. B |

Result |

| 1 |

0000 |

Adder |

02H |

01H |

03H |

| 2 |

0001 |

AND |

02H |

02H-00H |

02H-00H |

| 3 |

0010 |

BWINV |

02H |

|

FDH-FFH |

| 4 |

0011 |

Decoder |

03H-01H |

|

02-00H |

| 5 |

0100 |

Division |

04H |

04H |

01H |

| 6 |

0101 |

Increment |

02H |

|

03H |

| 7 |

0110 |

Logical AND |

02H |

04H |

01H |

| 8 |

0111 |

Inverter |

02H |

|

X0H |

| 9 |

1000 |

Logical OR |

02H |

00H |

X1H |

| 10 |

1001 |

OR |

02-00H |

04H |

06H-04H |

| 11 |

1010 |

Shift Left |

03-01H |

|

06H-02H |

| 12 |

1011 |

Shift Right |

03-01H |

|

02H-00H |

| 13 |

1100 |

Subtract |

03-01H |

01H |

02H-00H |

| 14 |

1101 |

XOR |

03-01H |

03H |

00H-02H |

| 15 |

1110 |

Modulo-2 |

03-01H |

|

00H-02H |

| 16 |

1111 |

Multiply |

03-01H |

|

06H-02H |

|

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).