Submitted:

13 January 2026

Posted:

14 January 2026

You are already at the latest version

Abstract

Keywords:

1. Introduction

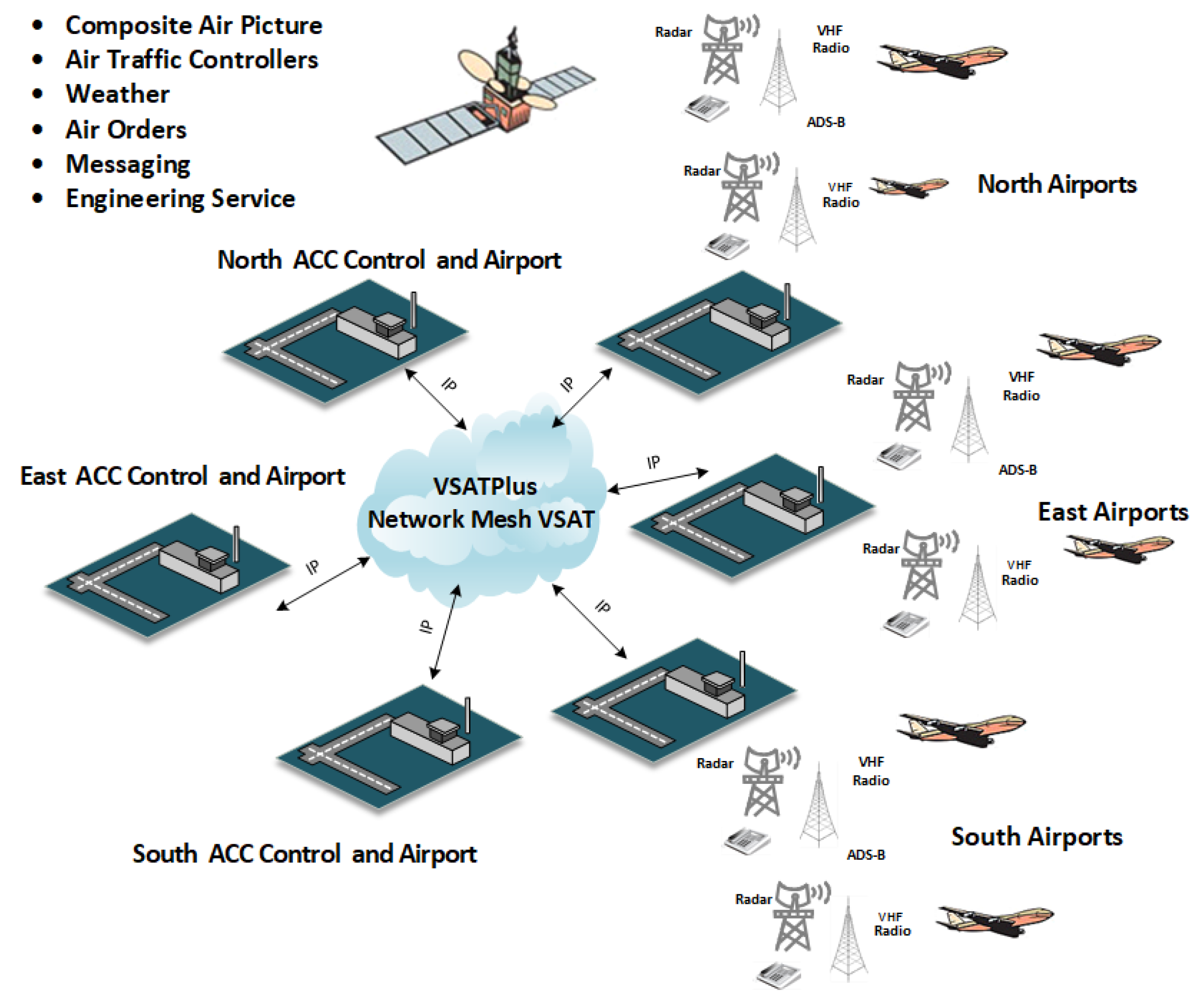

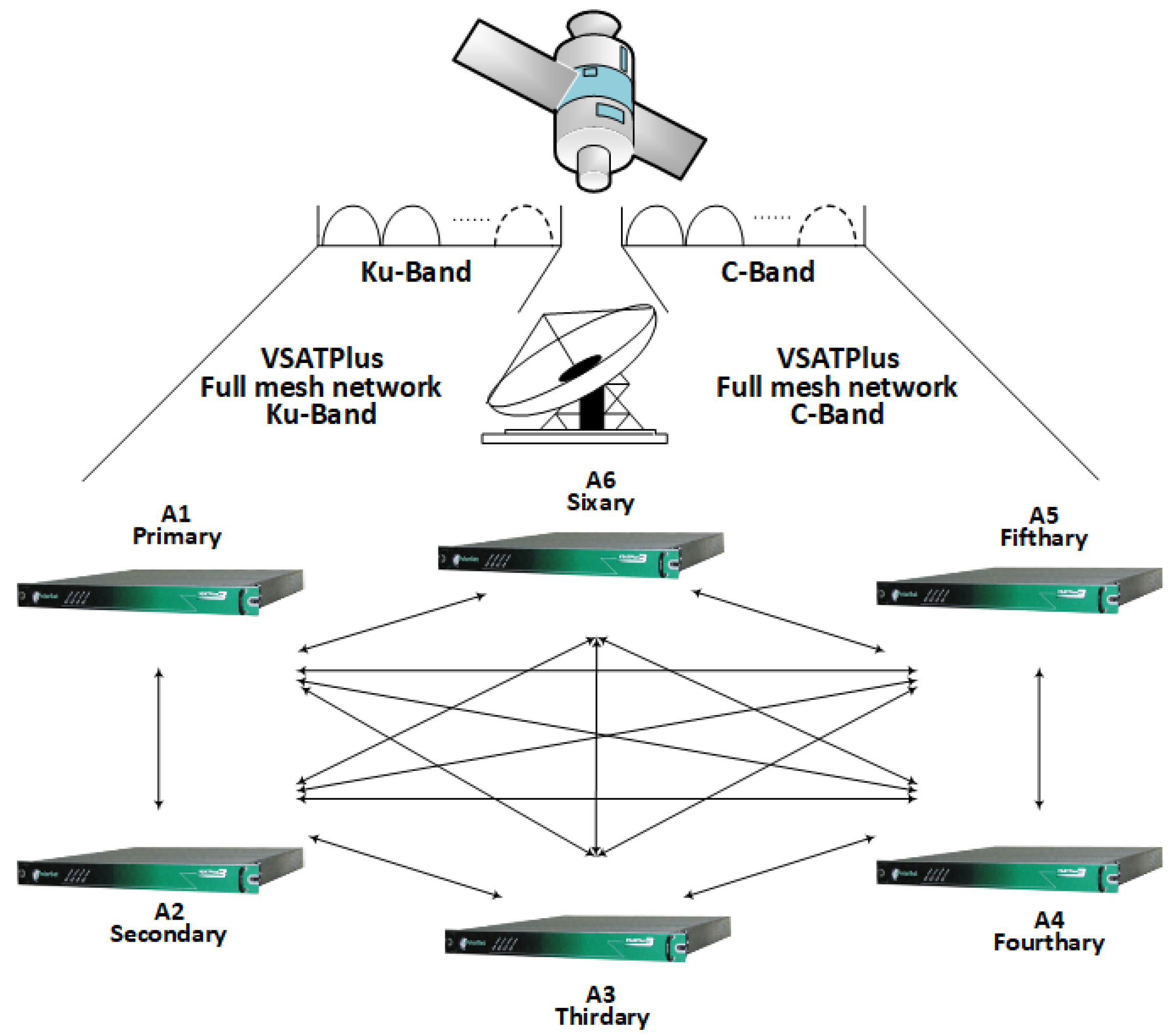

2. VSATPlus System Overview

3. Decoding Algorithmic Principles

3.1. Sum-Product / Belief Propagation

3.2. Min-Sum

3.3. Normalized Min-Sum

3.4. 2-Dimensional Normalized Min-Sum

3.5. 2-Dimensional Min-Sum

4. 2-Dimensional Corrected Normalized Min-Sum

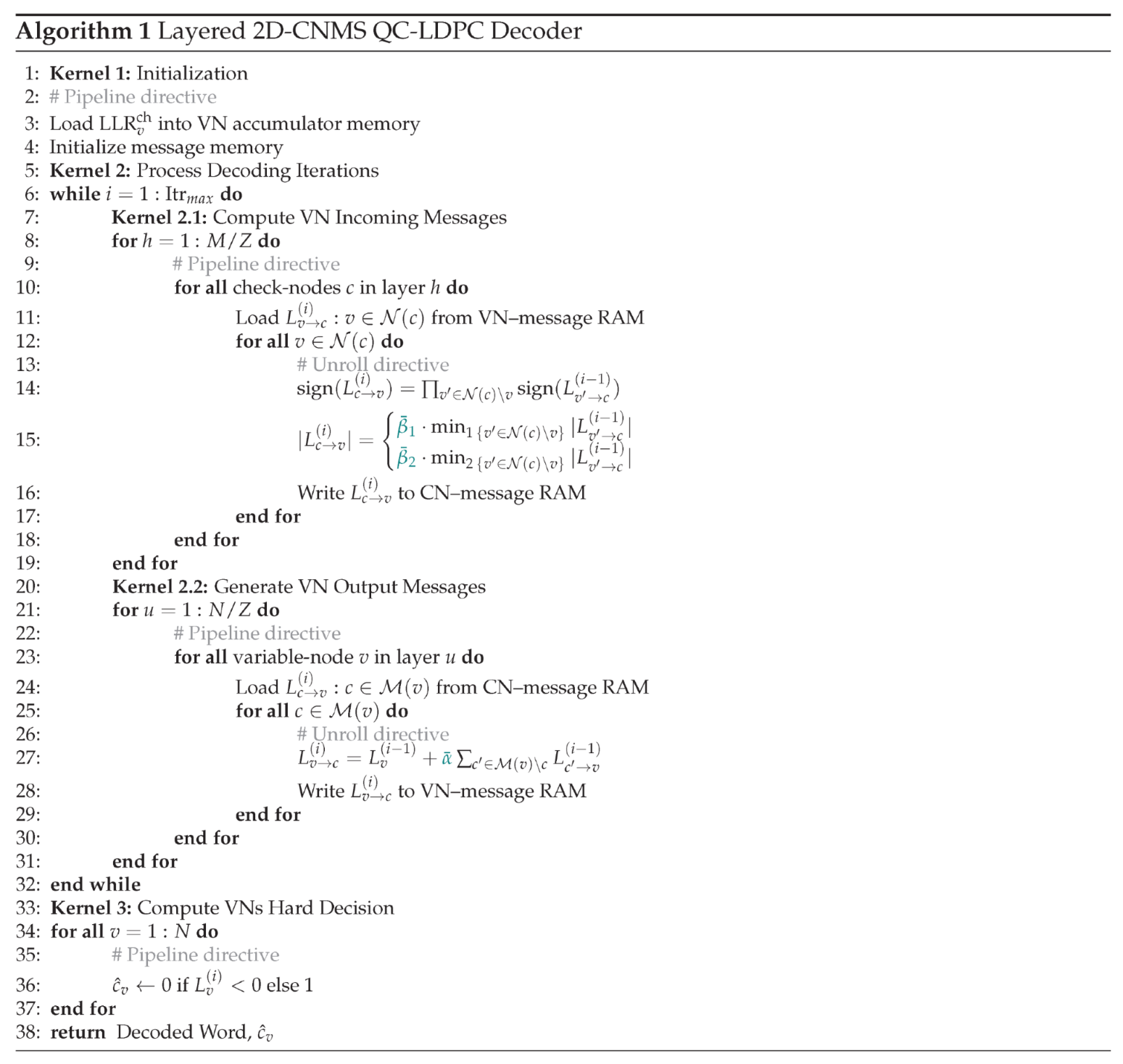

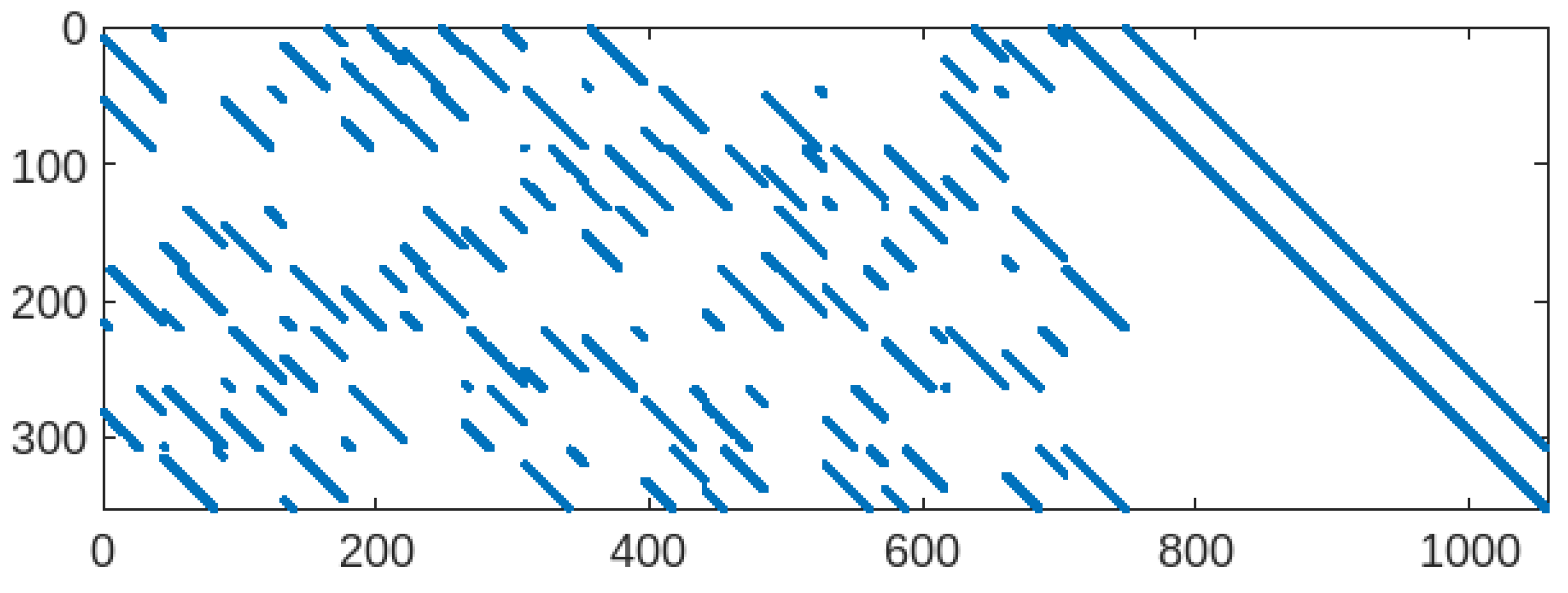

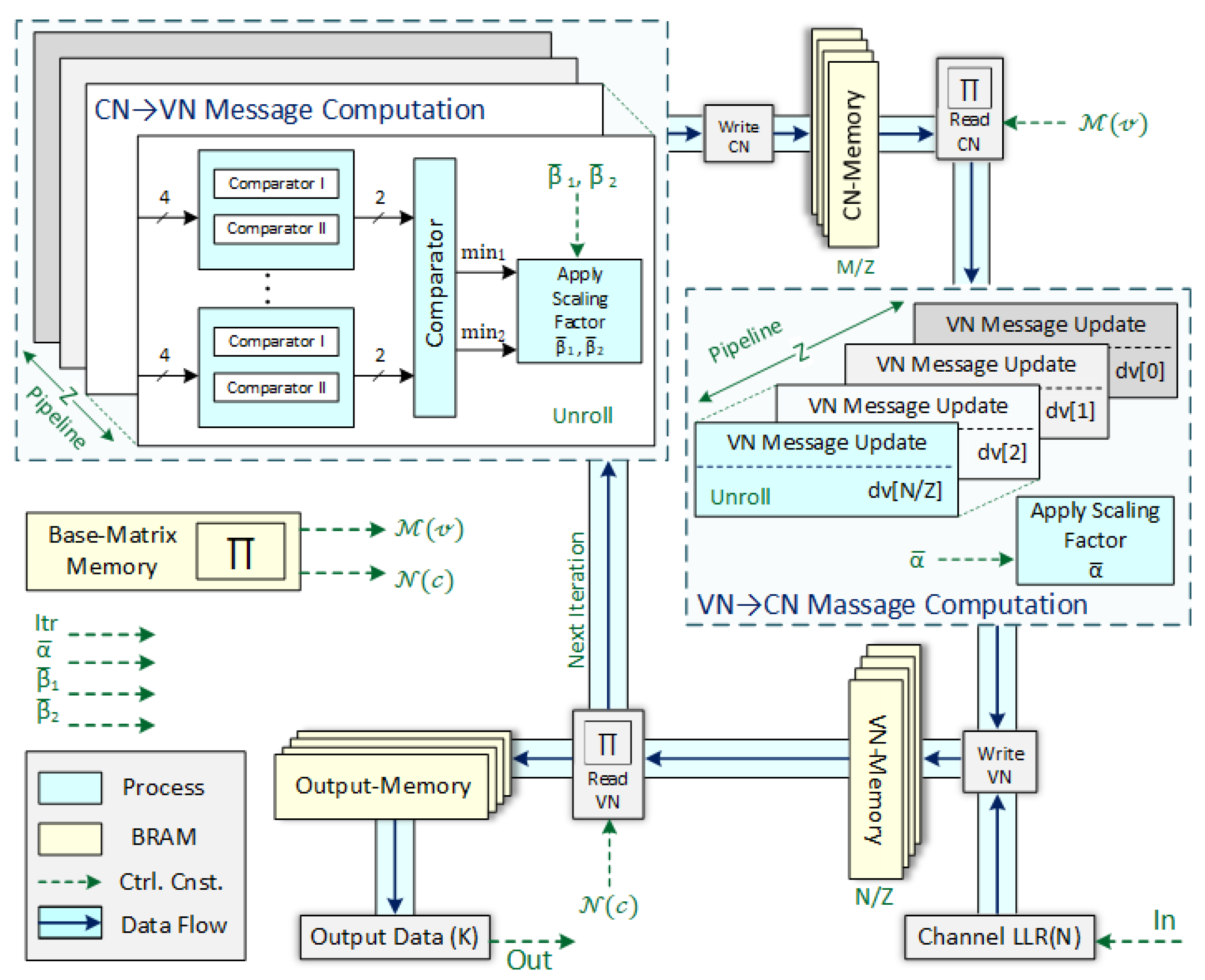

5. 2D-CNMS Hardware Implementation

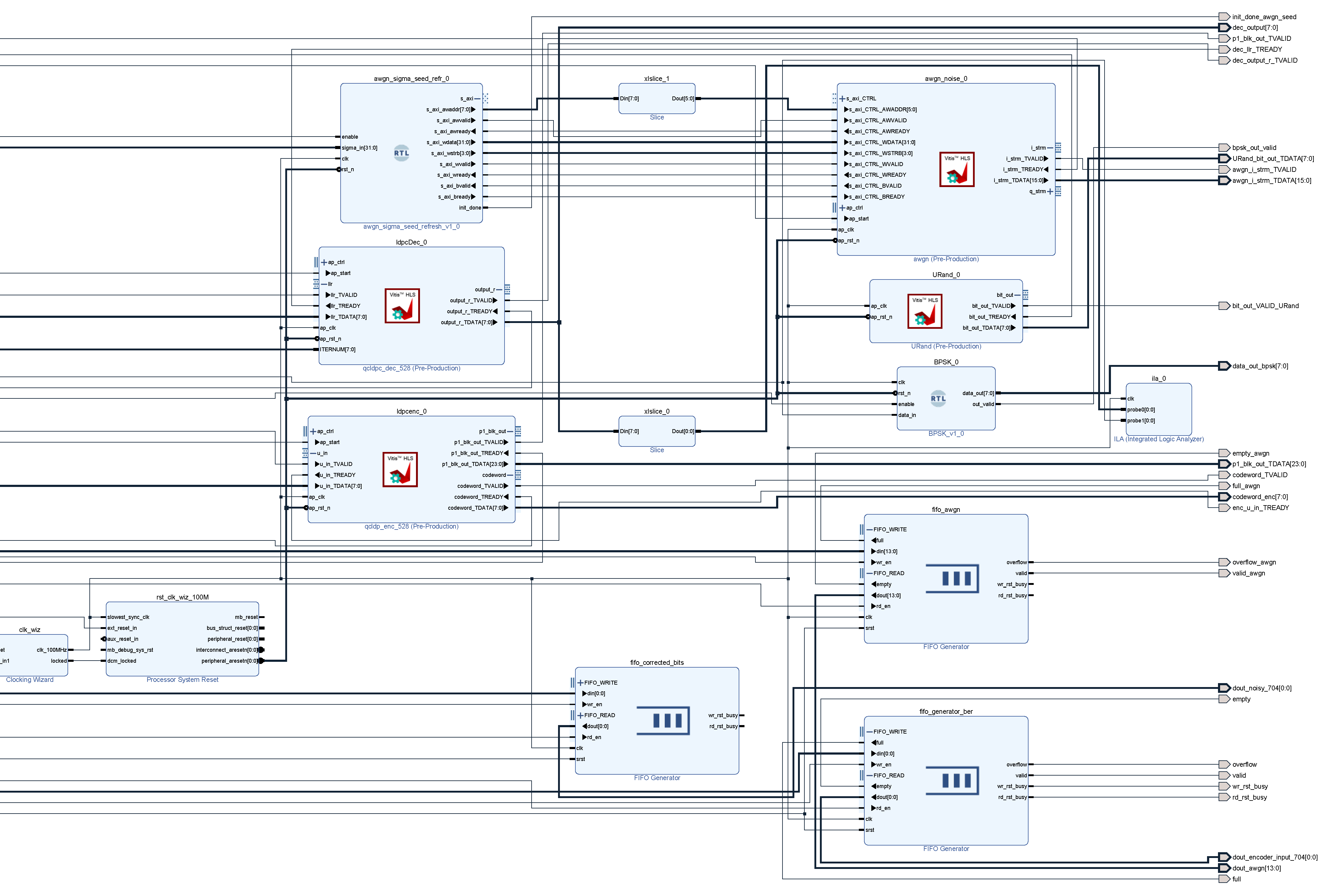

6. End-to-End Vivado Block Design

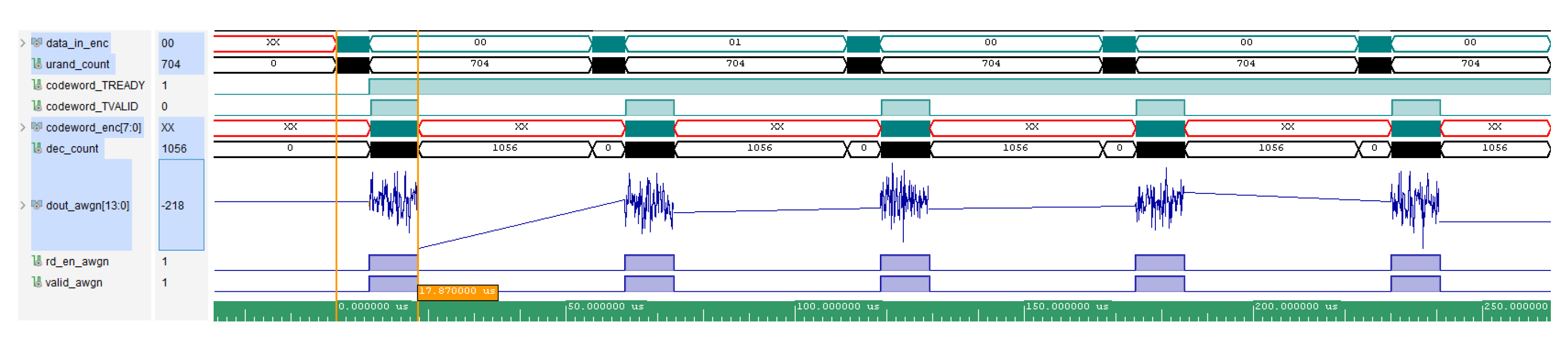

7. Emulation Results

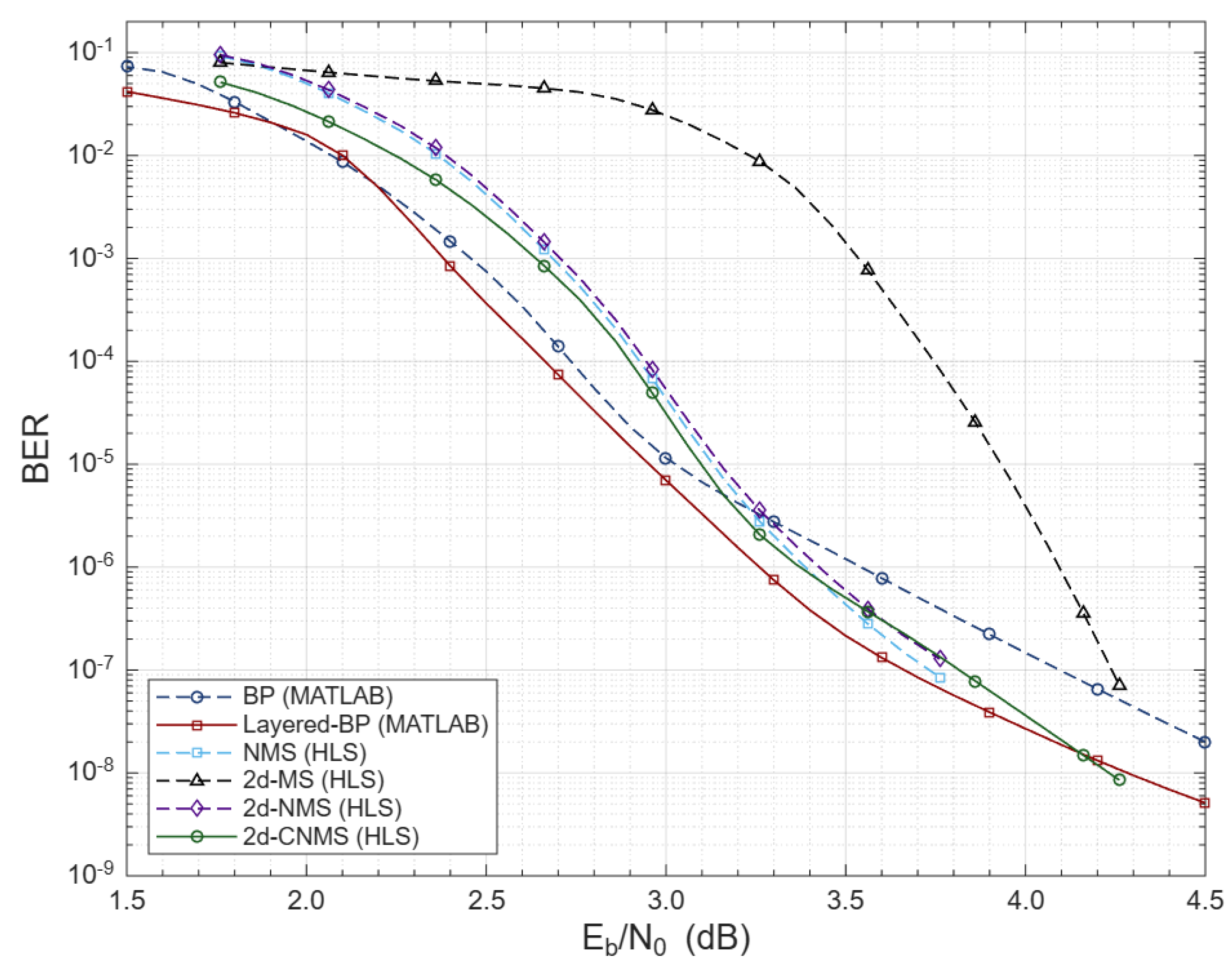

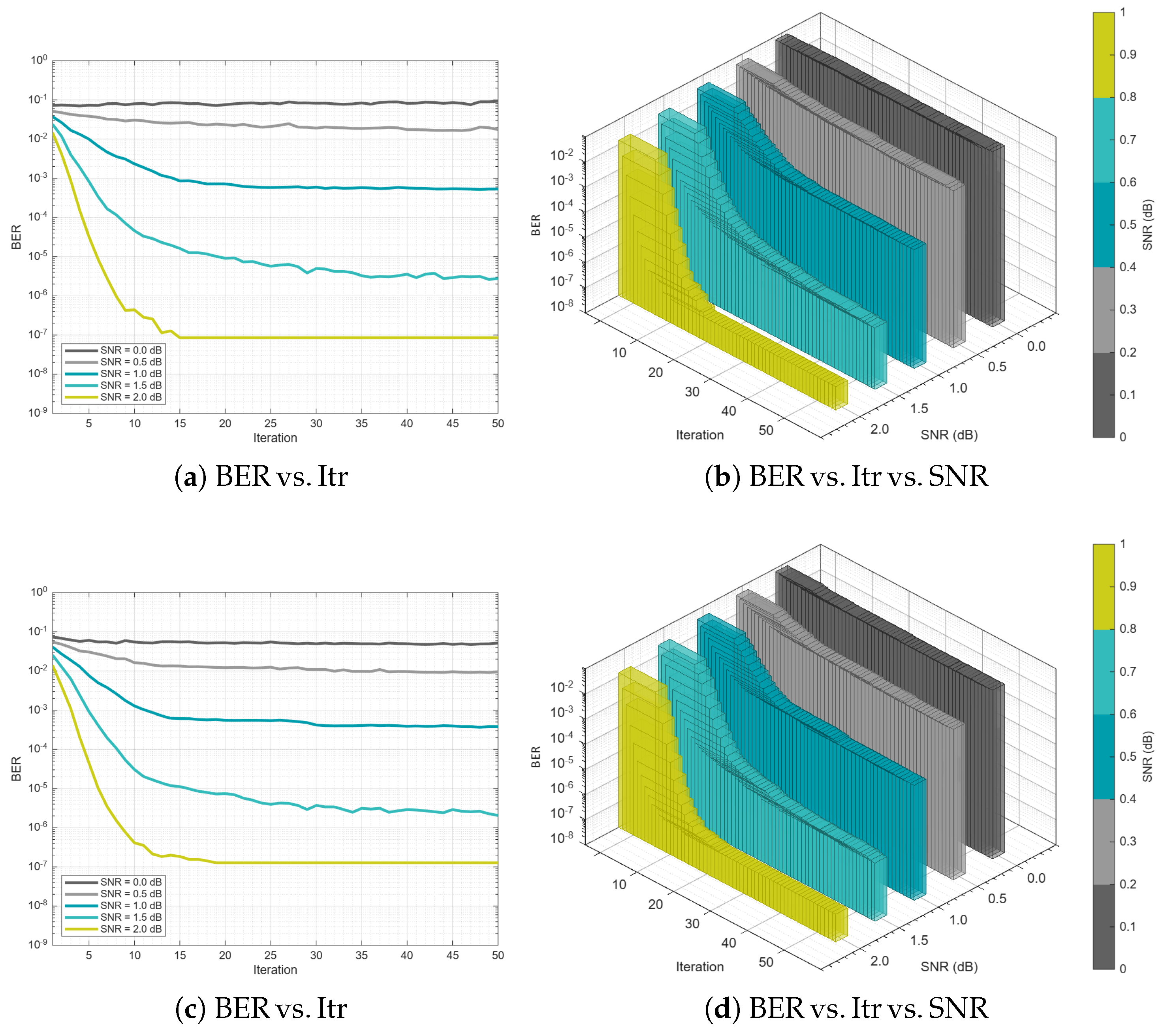

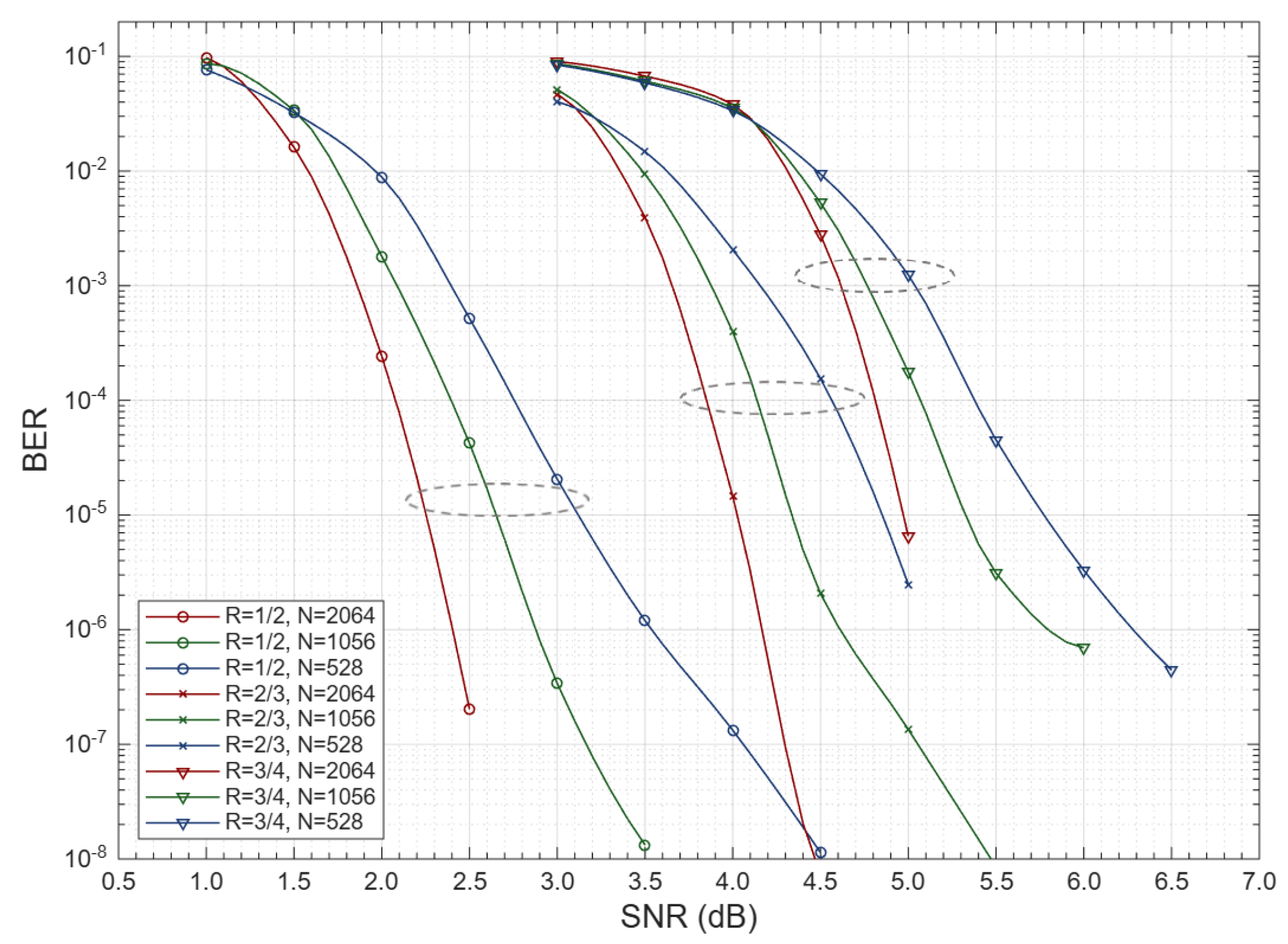

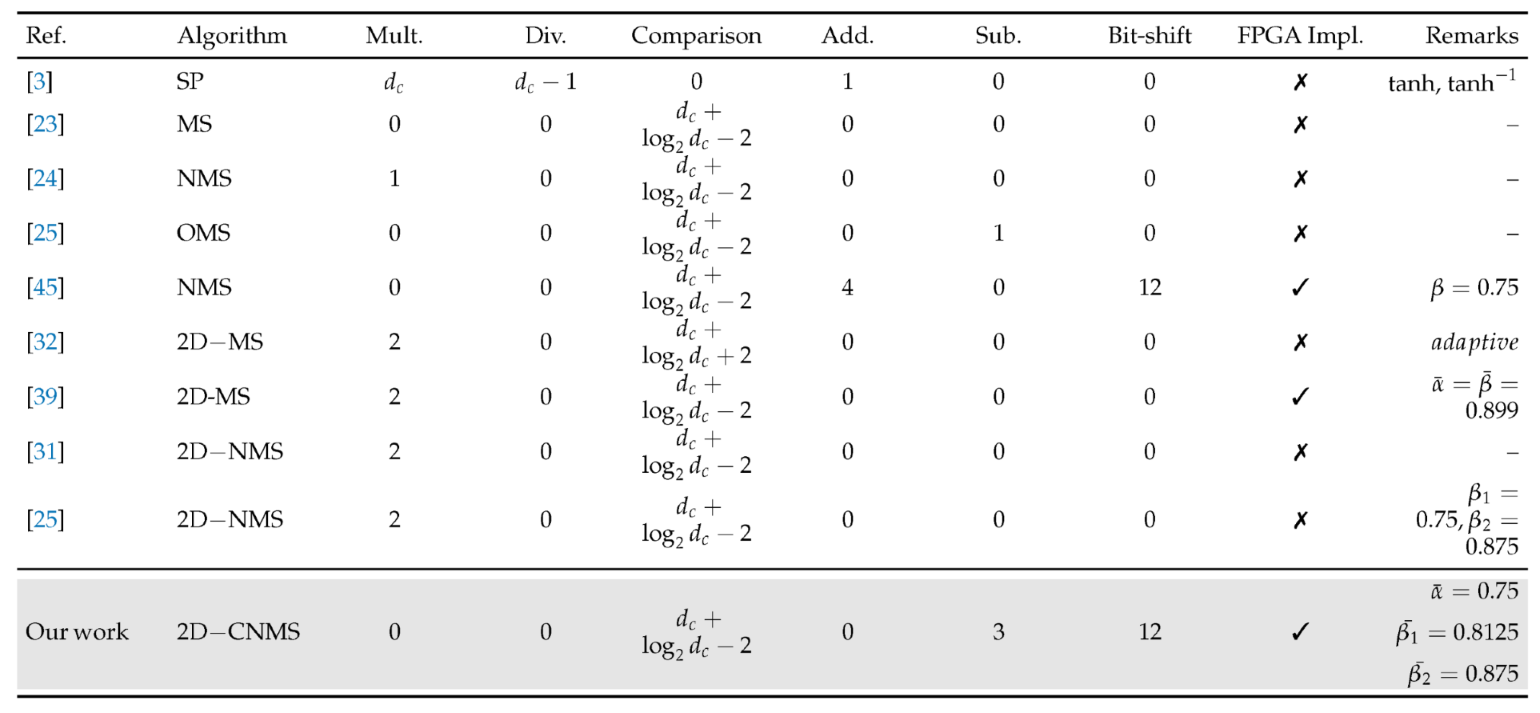

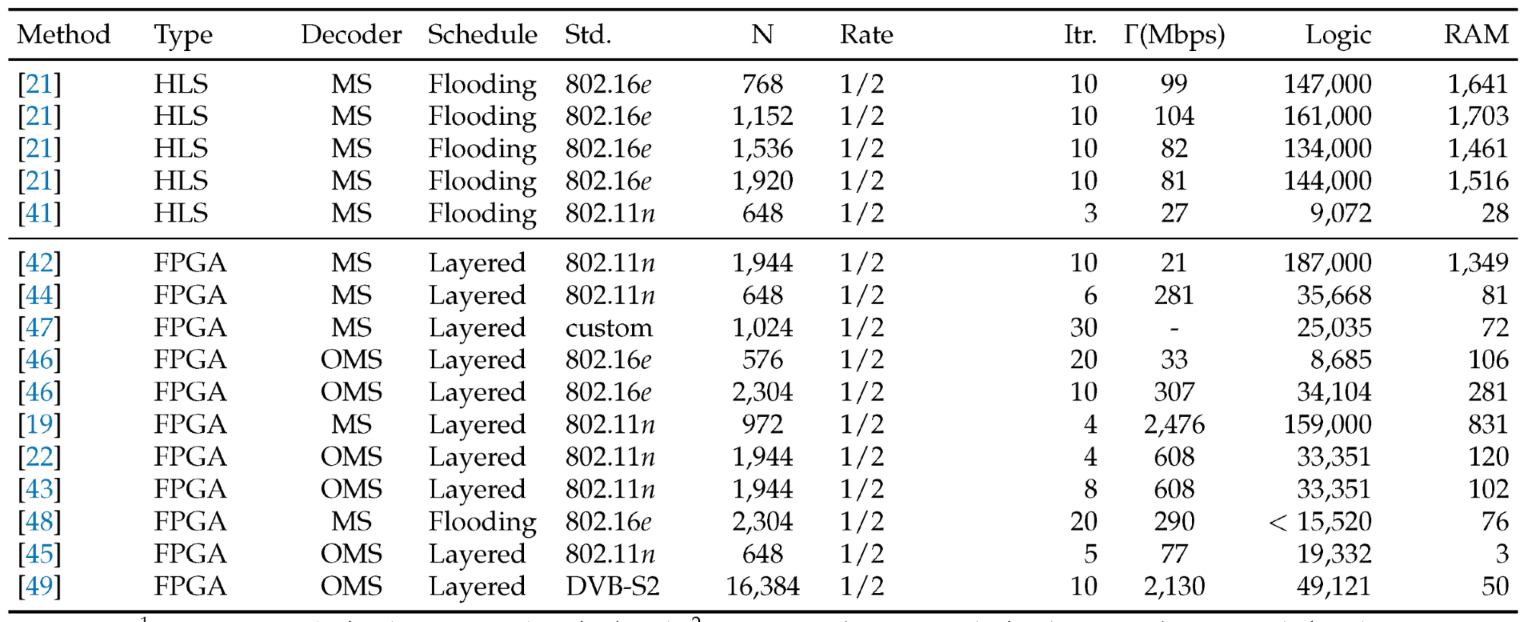

7.1. Performance and Complexity Comparison

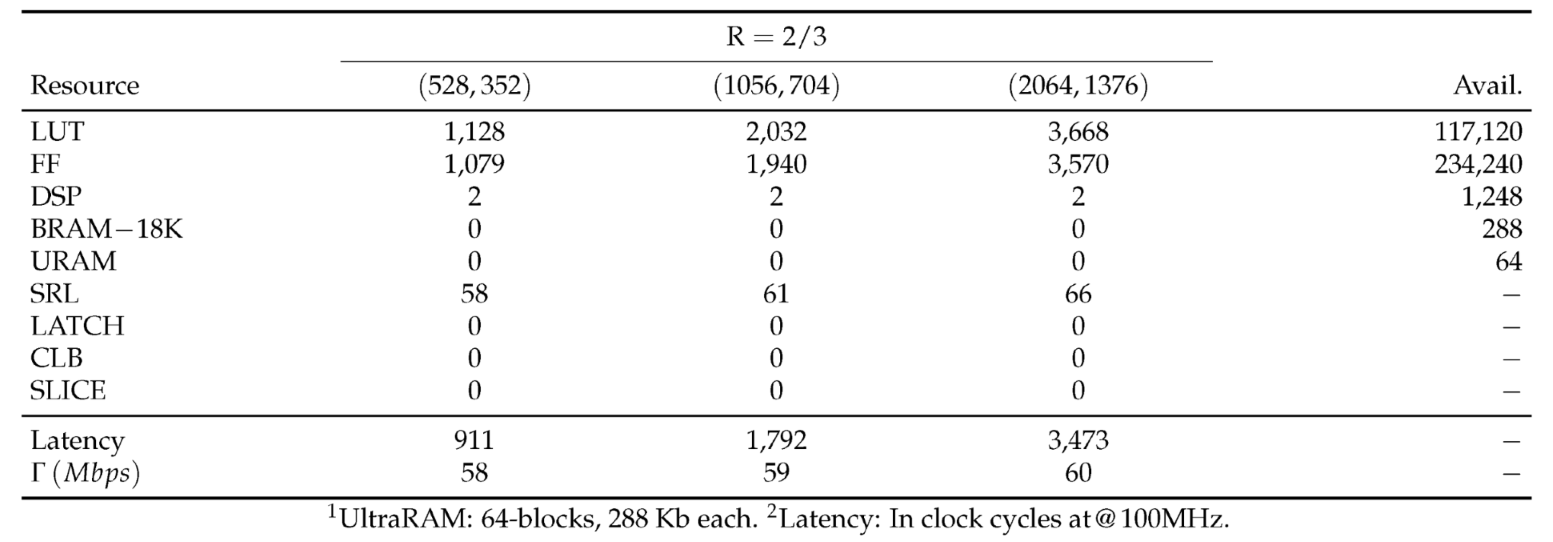

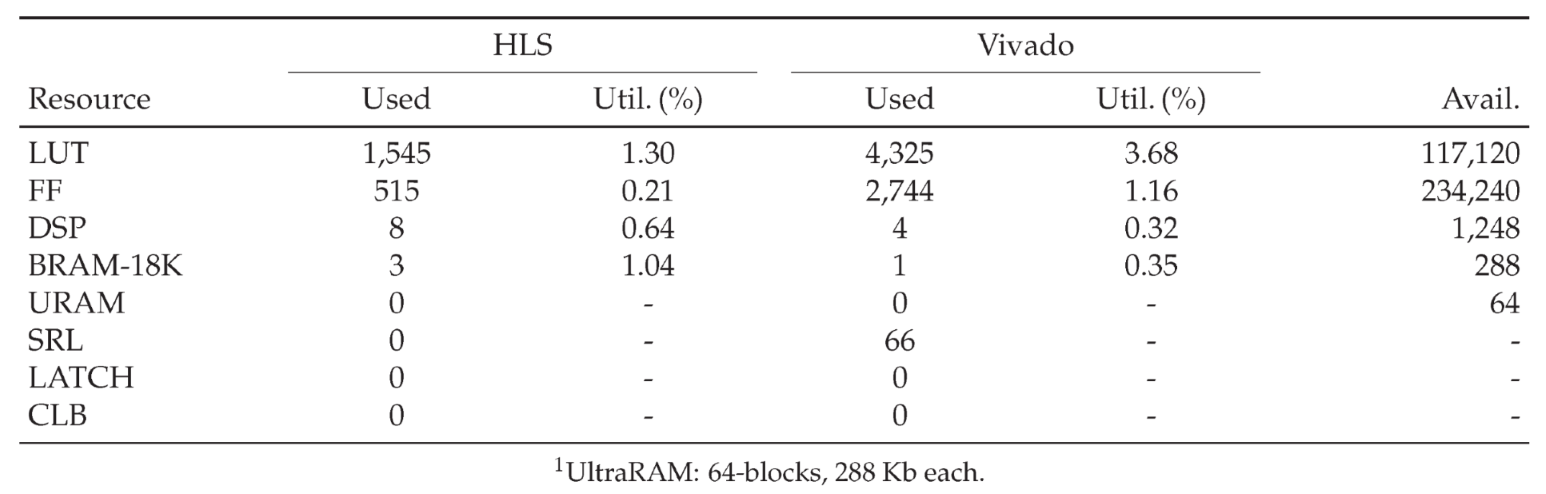

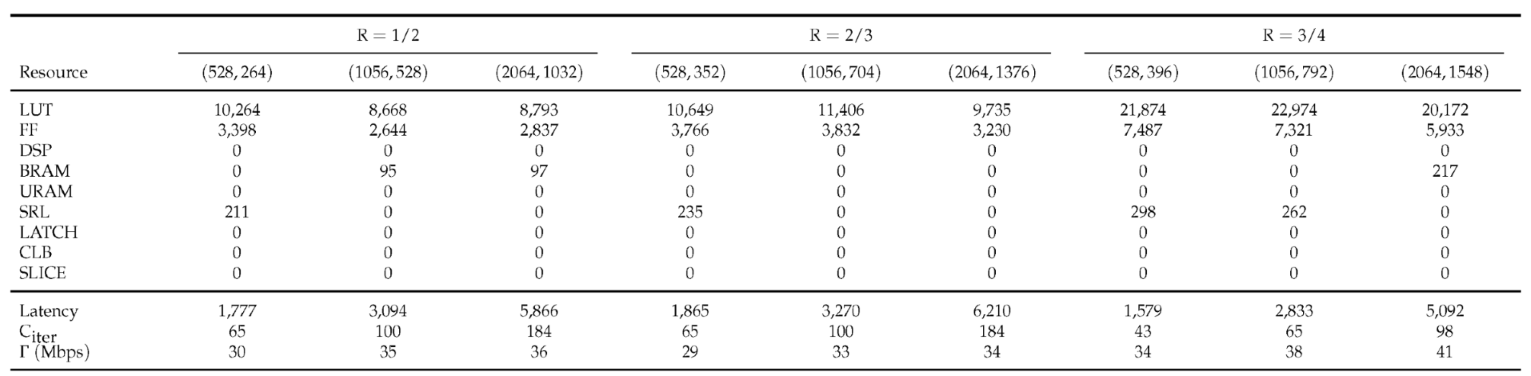

7.2. Resource Utilization

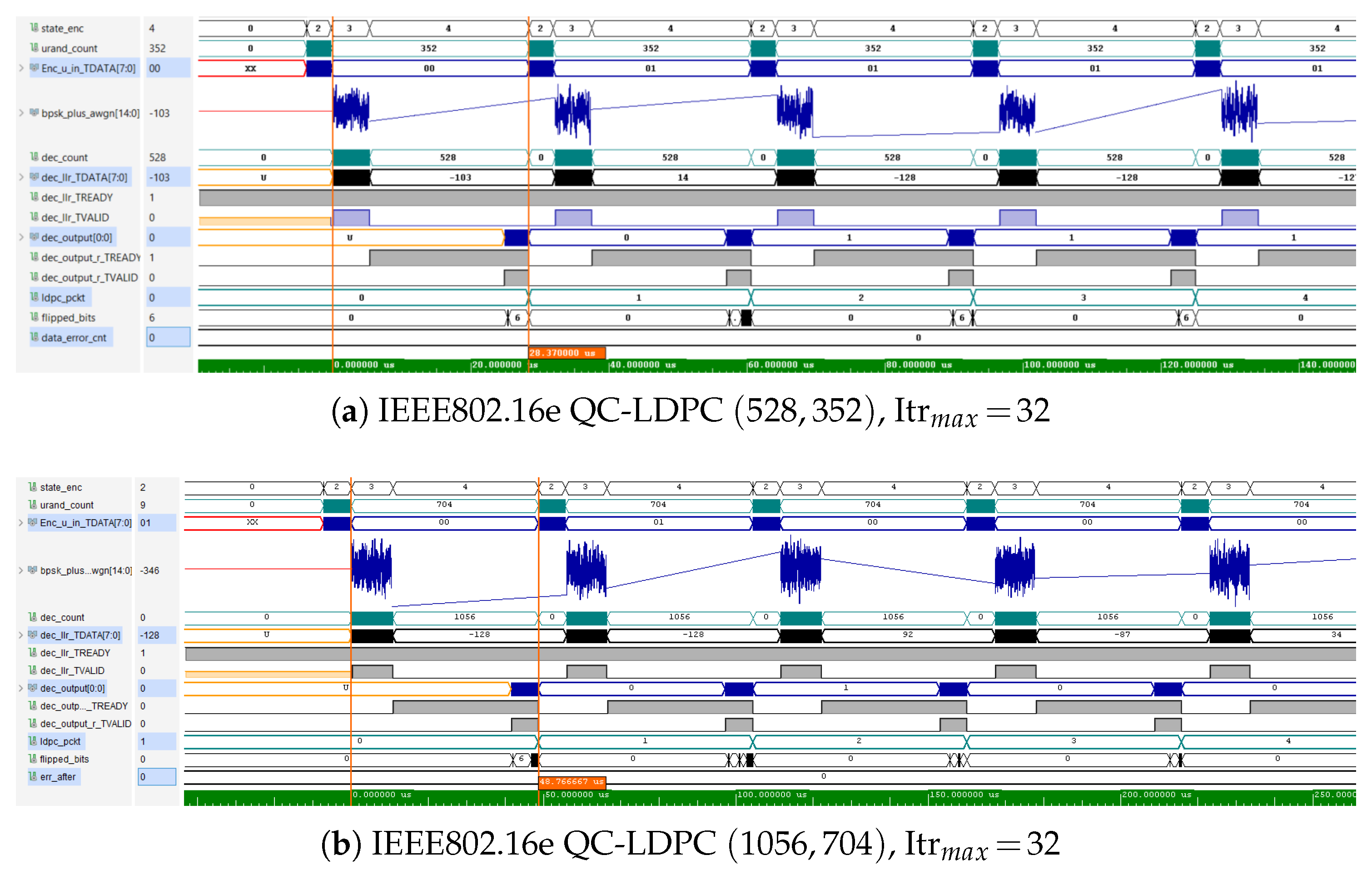

7.3. Decoding Latency Analysis

8. Conclusion

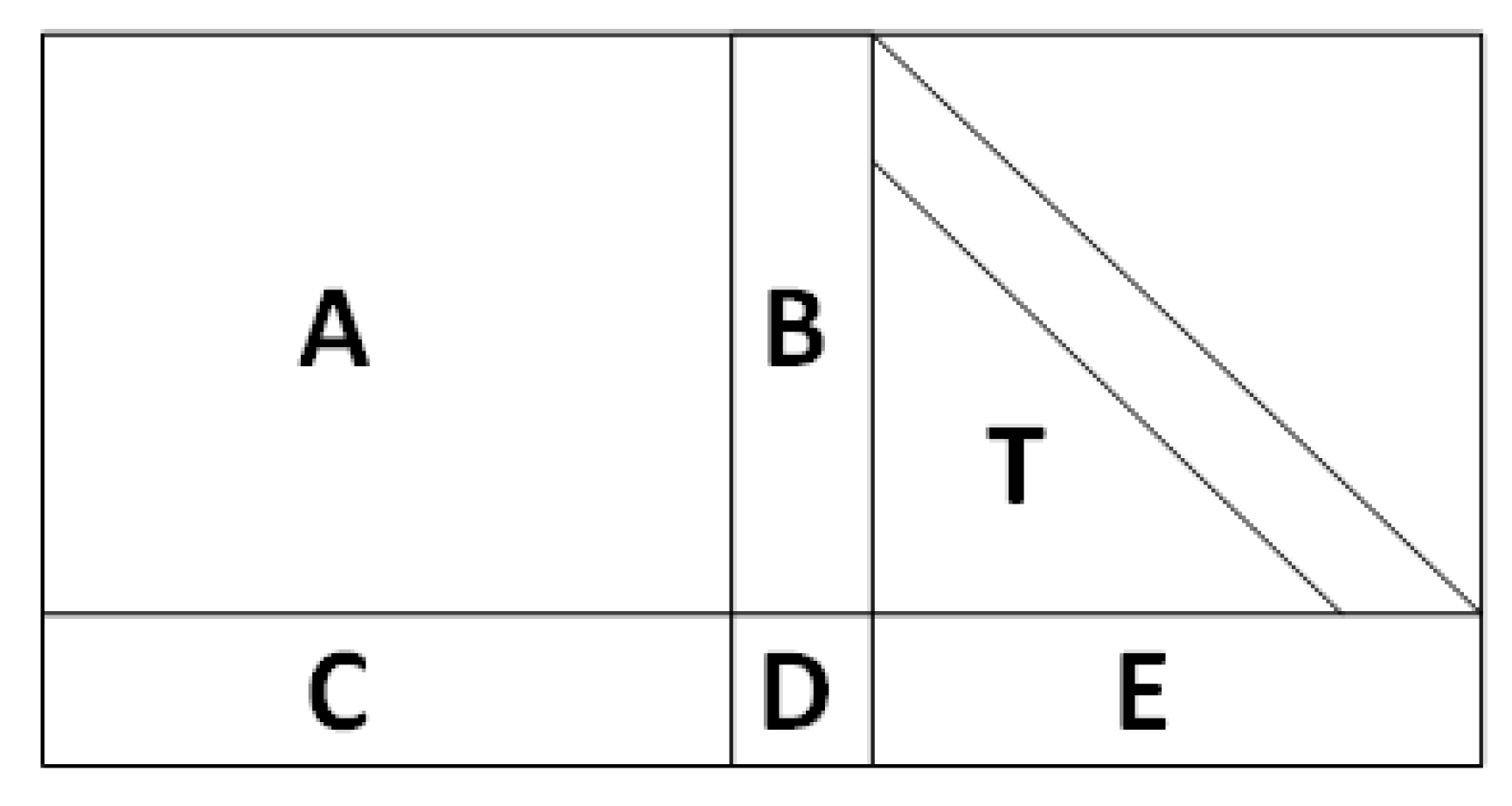

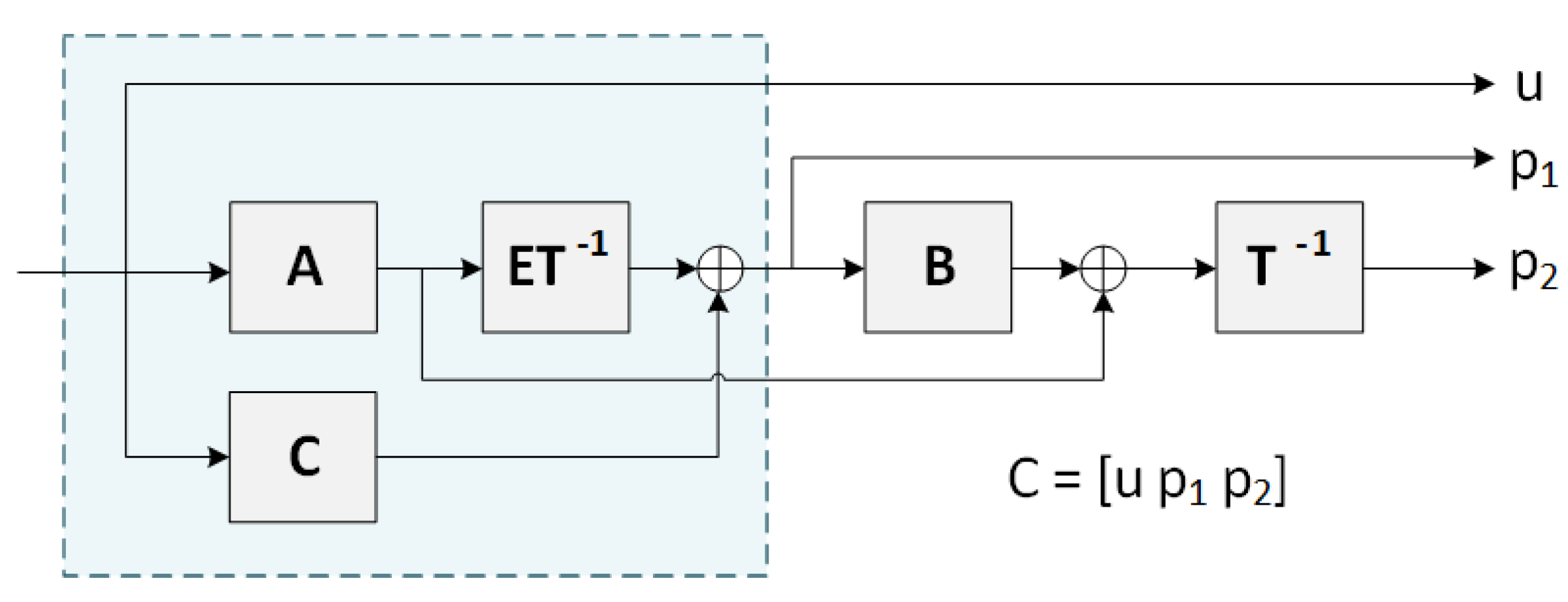

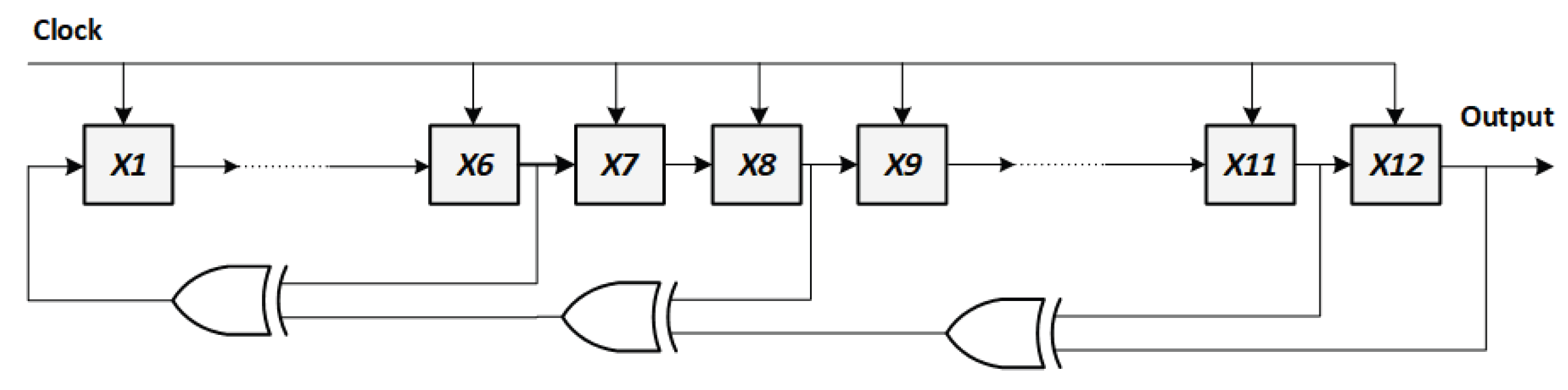

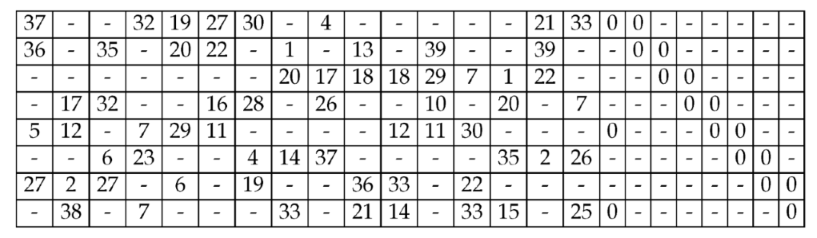

Appendix A. QC-LDPC Encoder

Appendix A.1. VSATPlus Encoder Algorithm

Appendix A.2. FPGA Implementation of VSATPlus Encoder

Appendix B. FPGA Implementation of an AWGN Channel

References

- Li, J.; Zhang, P.; Wang, L.; Wang, G. An FPGA-Based LDPC Decoder with Optimized Scale Factor in NMS Decoding Algorithm. SSRN Electronic Journal 2022. [Google Scholar] [CrossRef]

- Fossorier, M.P.C.; Mihaljevic, M.; Imai, H. Reduced complexity iterative decoding of low-density parity check codes based on belief propagation. IEEE Trans. Communications 1999, 47(5), 673–680. [Google Scholar] [CrossRef]

- MacKay, D.J.C. Good error-correcting codes based on very sparse matrices. IEEE Trans. Information Theory 1999, 45(2), 399–431. [Google Scholar] [CrossRef]

- Wang, Q.; Liu, Q.; Wang, S.; Chen, L.; Fang, H.; Chen, L.; Guo, Y.; Wu, Z. Normalized Min-Sum Neural Network for LDPC Decoding. IEEE Trans. Cognitive Communications and Networking 2023, 9(1), 70–81. [Google Scholar] [CrossRef]

- Oh, D.; Parhi, K.K. Min-Sum Decoder Architectures With Reduced Word Length for LDPC Codes. IEEE Trans. Circuits and Systems I: Regular Papers 2010, 57(1), 105–115. [Google Scholar] [CrossRef]

- Verma, A.; Shrestha, R. Low computational-complexity SOMS-algorithm and high-throughput decoder architecture for QC–LDPC codes. IEEE Trans. Vehicular Technology 2023, 72(1), 66–80. [Google Scholar] [CrossRef]

- Lopez, H.; Chan, H.-W.; Chiu, K.-L.; Tsai, P.-Y.; Jou, S.-J.J. A 75-Gb/s/mm2 and energy-efficient LDPC decoder based on a reduced complexity second minimum approximation min-sum algorithm. IEEE Trans. Very Large Scale Integration (VLSI) Systems 2020, 28(4), 926–939. [Google Scholar] [CrossRef]

- Yun, S.; Kong, B.Y.; Lee, Y. Area- and energy-efficient LDPC decoder using mixed-resolution check-node processing. IEEE Trans. Circuits and Systems II: Express Briefs 2022, vol. 69(no. 3), 999–1003. [Google Scholar] [CrossRef]

- Chen, J.; Dholakia, A.; Eleftheriou, E.; Fossorier, M.P.C.; Hu, X.-Y. Reduced-complexity decoding of LDPC codes. IEEE Trans. Communications 2005, 53(8), 1288–1299. [Google Scholar] [CrossRef]

- Mansour, M.M. A turbo-decoding message-passing algorithm for sparse parity-check matrix codes. IEEE Trans. Signal Processing 2006, vol. 54(no. 11), 4376–4392. [Google Scholar] [CrossRef]

- Richardson, T.J.; Urbanke, R.L. The capacity of low-density parity-check codes under message-passing decoding. IEEE Trans. Information Theory 2001, vol. 47(no. 2), 599–618. [Google Scholar] [CrossRef]

- Zhao, M.; Zhang, X.; Zhao, L.; Lee, C. Design of a high-throughput QC–LDPC decoder with TDMP scheduling. IEEE Trans. Circuits and Systems II: Express Briefs 2015, vol. 62(no. 1), 56–60. [Google Scholar] [CrossRef]

- Zhang, K.; Huang, X.; Wang, Z. A high-throughput LDPC decoder architecture with rate compatibility. IEEE Trans. Circuits and Systems I: Regular Papers 2011, vol. 58(no. 4), 839–847. [Google Scholar] [CrossRef]

- Darabiha, A.; Chan Carusone, A.; Kschischang, F.R. Power reduction techniques for LDPC decoders. IEEE Journal of Solid-State Circuits 2008, vol. 43(no. 8), 1835–1845. [Google Scholar] [CrossRef]

- Delomier, Y.; Le Gal, B.; Crenne, J.; Jego, C. Model-based design of flexible and efficient LDPC decoders on FPGA devices. Journal of Signal Processing Systems 2020, vol. 92(no. 7), 727–745. [Google Scholar] [CrossRef]

- Martin, G.; Smith, G. High-Level Synthesis: Past, Present, and Future. IEEE Design & Test of Computers 2009, vol. 26(no. 4), 18–25. [Google Scholar] [CrossRef]

- Le Gal, B.; Jego, C.; Leroux, C. A flexible NISC-based LDPC decoder. IEEE Trans. Signal Processing 2014, vol. 62(no. 10), 2469–2479. [Google Scholar] [CrossRef]

- Zhang, Y.-F.; Sun, L.; Cao, Q. TLP-LDPC: Three-level parallel FPGA architecture for fast prototyping of LDPC decoder using high-level synthesis. Journal of Computer Science and Technology 2022, vol. 37(no. 6), 1290–1306. [Google Scholar] [CrossRef]

- Mhaske, S.; Kee, H.; Ly, T.; Aziz, A.; Spasojevic, P. FPGA-Based Channel Coding Architectures for 5G Wireless Using High-Level Synthesis. International Journal of Reconfigurable Computing 2017, Article No. 3689308. [Google Scholar] [CrossRef]

- Yuan, J.; Sha, J. 4.7-Gb/s LDPC Decoder on GPU. IEEE Communications Letters 2018, vol. 22(no. 3), 478–481. [Google Scholar] [CrossRef]

- Andrade, J.; Falcão, G.; Silva, V. Flexible design of wide-pipeline-based WiMAX QC-LDPC decoder architectures on FPGAs using high-level synthesis. IET Electronics Letters 2014, vol. 50, 839–840. [Google Scholar] [CrossRef]

- Mhaske, S.; Kee, H.; Ly, T.; Aziz, A.; Spasojevic, P. FPGA-Based Channel Coding Architectures for 5G Wireless Using High-Level Synthesis. Article ID 3689308; International Journal of Reconfigurable Computing. 2017. [Google Scholar] [CrossRef]

- Wey, C.-L.; Shieh, M.-D.; Lin, S.-Y. Algorithms of finding the first two minimum values and their hardware implementation. IEEE Trans. Circuits Syst. I, Reg. Papers 2008, vol. 55(no. 11), 3430–3437. [Google Scholar] [CrossRef]

- Wang, Q.; Liu, Q.; Wang, S.; Chen, L.; Fang, H.; Chen, L.; Guo, Y.; Wu, Z. Normalized min-sum neural network for LDPC decoding. IEEE Trans. Cogn. Commun. Netw. 2023, vol. 9(no. 1), 70–81. [Google Scholar] [CrossRef]

- Oh, D.; Parhi, K.K. Min-sum decoder architectures with reduced word length for LDPC codes. IEEE Trans. Circuits Syst. I, Reg. Papers 2010, vol. 57(no. 1), 105–115. [Google Scholar] [CrossRef]

- Fossorier, M.P.C.; Mihaljević, M.; Imai, H. Reduced complexity iterative decoding of low-density parity-check codes based on belief propagation. IEEE Trans. Commun. 1999, vol. 47(no. 5), 673–680. [Google Scholar] [CrossRef]

- Tanner, R.M. A recursive approach to low complexity codes. IEEE Trans. Inf. Theory 1981, vol. 27(no. 5), 533–547. [Google Scholar] [CrossRef]

- Cai, Y.; Jeon, S.; Mai, K.; Vijaya Kumar, B.V.K. Highly parallel FPGA emulation for LDPC error floor characterization in perpendicular magnetic recording channel. IEEE Trans. Magn. 2009, 45(10), 3761–3764. [Google Scholar] [CrossRef]

- Fossorier , M.P.C. Quasicyclic low-density parity-check codes from circulant permutation matrices. IEEE Trans. Inf. Theory 2004, 50(8), 1788–1793. [Google Scholar] [CrossRef]

- Chung, K.; Cho, K.; Lee, W.-H. Simplified 2-dimensional scaled min-sum algorithm for LDPC decoder J. Electr. Eng. Technol. 2017, 12(no. 3), 1262–1270. [Google Scholar] [CrossRef]

- Zhong, Z.; Guo, S.; Xu, X.; Bai, H. A classified normalized BP-based algorithm with 2-dimensional correction for LDPC codes. J. Commun. 2013, vol. 8(no. 5), 315–321. [Google Scholar] [CrossRef]

- Hamad, A. Estimation of two-dimensional correction factors for min-sum decoding of regular LDPC code. Wireless Eng. Technol. 2013, 4(4), 181–187. [Google Scholar] [CrossRef]

- Roberts, M.K.; Jayabalan, R. An improved low-complexity sum-product decoding algorithm for low-density parity-check codes. Frontiers of Information Technology & Electronic Engineering 2015, 16(6), 511–518. [Google Scholar]

- Le Gal, B.; Jego, C. Low-latency software LDPC decoders for x86 multi-core devices. Proc. the 2017 IEEE International Workshop on Signal Processing Systems (SiPS), 2017; pp. 1–6. [Google Scholar] [CrossRef]

- Wiberg, N.; Loeliger, H.-A.; Kotter, R. Codes and iterative decoding on general graphs. In Proc. 1995 IEEE International Symposium on Information Theory (ISIT); IEEE: Whistler, BC, Canada, 1995; p. pp. 468. [Google Scholar] [CrossRef]

- Boncalo, O.; Amaricai, A. Ultra high throughput unrolled layered architecture for QC-LDPC decoders. Proc. the 2017 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Bochum, Germany, 2017; pp. 225–230. [Google Scholar] [CrossRef]

- Yang, N.; Jing, S.; Yu, A.; Liang, X.; Zhang, Z.; You, X.; Zhang, C. Reconfigurable decoder for LDPC and polar codes. Proc. 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 2018; pp. 1–5. [Google Scholar] [CrossRef]

- Bhatt, T.; Sundaramurthy, V.; Stolpman, V.; McCain, D. Pipelined block-serial decoder architecture for structured LDPC codes. Proc. 2006 IEEE International Conference on Acoustics Speech and Signal Processing Proceedings (ICASSP), Toulouse, France, 2006; vol. 4, p. IV. [Google Scholar] [CrossRef]

- Tamkeen, S.A.; Hamad, A.A. FPGA implementation of scaled “Quasi-Cyclic LDPC” decoder using high-level synthesis. First International Conference on Mathematical Modeling and Computational Science: ICMMCS 2020, Pattaya, Thailand, 2021; pp. 131–142. [Google Scholar] [CrossRef]

- Wen, X.; Jiao, X.; Jääskeläinen, P.; Kultala, H.; Chen, C.; Berg, H.; Bie, Z. A high throughput LDPC decoder using a mid-range GPU. Proc. 2014 IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP), Florence, Italy, 2014; IEEE; pp. 7515–7519. [Google Scholar] [CrossRef]

- Scheiber, E.; Bruck, G.H.; Jung, P. Implementation of an LDPC decoder for IEEE 802.11n using Vivado™ High-Level Synthesis. Proc. 2013 IEEE International Conference on Electronics, Signal Processing and Communication Systems, 2013; no. 4. [Google Scholar]

- Andrade, J.; Pratas, F.; Falcao, G.; Silva, V.; Sousa, L. Combining flexibility with low power: Dataflow and wide-pipeline LDPC decoding engines in the Gbit/s era. Proc. 2014 IEEE 25th International Conference on Application-Specific Systems, Architectures and Processors (ASAP), 2014; pp. 264–269. [Google Scholar] [CrossRef]

- Mhaske, S.; Kee, H.; Ly, T.; Aziz, A.; Spasojevic, P. High-Throughput FPGA-Based QC-LDPC Decoder Architecture. Proc. 2015 IEEE 82nd Vehicular Technology Conference (VTC2015-Fall), 2015; pp. 1–5. [Google Scholar] [CrossRef]

- Zied, S.A.; Sayed, A.T.; Guindi, R. Configurable low complexity decoder architecture for Quasi-Cyclic LDPC codes. Proc. 2013 21st International Conference on Software, Telecommunications and Computer Networks (SoftCOM), 2013; pp. 1–5. [Google Scholar] [CrossRef]

- Tanyanon, I.; Choomchuay, S. A hardware design of MS/MMS-based LDPC decoder. Proc. 2012 IEEE International Conference on Electron Devices and Solid State Circuits (EDSSC), 2012; pp. 1–4. [Google Scholar] [CrossRef]

- Le Gal, B.; Jego, C. Design of an ASIP LDPC Decoder Compliant with Digital Communication Standards. Proc. 2012 IEEE Workshop on Signal Processing Systems (SiPS), 2012; pp. 19–24. [Google Scholar] [CrossRef]

- Zhao, W.H.; Long, J.P. Implementing the NASA Deep Space LDPC Codes for Defense Applications. Proc. 2013 IEEE Military Communications Conference (MILCOM), 2013; pp. 803–808. [Google Scholar] [CrossRef]

- Amaricai, A.; Boncalo, O.; Mot, I. Memory efficient FPGA implementation for flooded LDPC decoder. Proc. 2015 23rd Telecommunications Forum (TELFOR), Belgrade, Serbia, 2015; pp. 500–503. [Google Scholar] [CrossRef]

- Pignoly, V.; Le Gal, B.; Jego, C.; Gadat, B. High data rate and flexible hardware QC-LDPC decoder for satellite optical communications. Proc. 2018 IEEE 10th International Symposium on Turbo Codes & Iterative Information Processing (ISTC), 2018; pp. 1–5. [Google Scholar] [CrossRef]

- Khosroshahi, N.; Gulliver, T.A. Quasi-cyclic low density parity check (LDPC) codes for dedicated short range communication (DSRC) systems. Proc. 2010 IEEE Canadian Conference on Electrical and Computer Engineering (CCECE), Calgary, AB, Canada, 2010; IEEE; pp. 1–5. [Google Scholar] [CrossRef]

- Çağlan, A.; İnceöz, E.; Balcısöy, E.; Özbek, M.; Çavuş, E. FPGA implementation of AWGN noise generator using Box–Muller method. Proc. IEEE SIU, May 2016; pp. 1813–1816. [Google Scholar] [CrossRef]

- Cross, M.A.; Fleetwood, T. Hubless VSAT networks. IEE Colloquium on VSATs—Trends and Technologies, 1989; pp. 5/1–5/13. [Google Scholar]

- Khosroshahi, N.; Mankarious, R.; Soleymani, M.R. CNN-Based LDPC Decoder for Hubless Full-Mesh VSATPlus® System. Proc. IEEE/AIAA Digital Avionics Systems Conference (DASC) to be published, 2025. [Google Scholar]

- IEEE Std 802.16TM; IEEE Standard for Local and metropolitan area networks - Part 16: Air Interface for Broadband Wireless Access Systems. 2009.

- IEEE Std 802.11n; IEEE Standard for Local and metropolitan area networks - Specific requirements - Part 11: Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) Specifications. 2009.

- IEEE Std 802.11ad; IEEE Standard for Local and metropolitan area networks - Specific requirements - Part 11: Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) Specifications. 2007.

- TS V5G.212 V1.2; Verizon 5G Technical Forum; Air Interface Working Group; Verizon 5th Generation Radio Access; Multiplexing and channel coding (Release 1). 2016.

- 3GPP TS 38.212 V15.2.0; 3rd Generation Partnership Project; Technical Specification; 5G; NR; Multiplexing and channel coding. 2018.

- ETSI EN 302 307 V1.4.1; Digital Video Broadcasting (DVB); Second generation framing structure, channel coding and modulation systems for Broadcasting, Interactive Services, News Gathering and other broadband satellite applications (DVB-S2). 2009.

- ETSI EN 302 769 V1.3.1; Digital Video Broadcasting (DVB); Frame structure, channel coding and modulation for a second generation digital transmission system for cable systems (DVB-C2). 2009.

- ETSI EN 300 744 V1.6.1; Digital Video Broadcasting (DVB); Framing structure, channel coding and modulation for digital terrestrial television (DVB-T). 2009.

- ETSI ES 300 401 V1.4.1; Radio Broadcast systems; Digital Audio Broadcasting (DAB) to mobile, portable and fixed receivers. 1995.

- ETSI GSM 05.05; Digital cellular telecommunications system (Phase 2+); Radio transmission and reception (GSM). 1996.

- ETSI TS 136 201 V15.2.0; Evolved Universal Terrestrial Radio Access (E-UTRA); LTE physical layer—General description. 2017.

- IEEE 802.16 Working Group LDPC coding for OFDMA PHY Contribution to IEEE 802.16e, Aug. 2004. Available online: http://ieee802.org/16/tge/contrib/C80216e-04_373r1.pdf.

- PolarSat Inc. VSATPlus3® Overview 2003. Available online: https://www.polarsat.com/vsatplus-3.

- AMD Xilinx. Vivado Design Suite User Guide: High-Level Synthesis UG902 V2020.1 . May 2021. Available online: https://docs.amd.com/v/u/en-US/ug902-vivado-high-level-synthesis.

- Wiberg, N. Codes and decoding on general graphs. Ph.D. dissertation, Dept. Elect. Eng., Linköping Univ., Sweden, 1996. [Google Scholar]

Short Biography of Authors

|

Najmeh Khosroshahi (Member, IEEE) received the B.Sc. degree in electrical and computer engineering from the University of Tehran, Tehran, Iran, in 2007, and the M.Sc. degree in electrical and computer engineering from the University of Victoria, Victoria, BC, Canada, in 2011. She is currently pursuing the Ph.D. degree in electrical and computer engineering at Concordia University, Montréal, QC, Canada. She is a Digital Communication Systems Engineer with PolarSat Inc., Montréal, QC, Canada, developing and verifying FPGA-centric signal-processing for VSAT platforms. Her current research interests include error-correcting codes, artificial intelligence (AI), quantum/learning-assisted decoding, and satellite communications. She is the author of Inter-Vehicle Communication Systems Improvement (LAP LAMBERT Academic Publishing, 2014). |

|

Ron Mankarious (Member, IEEE) received the B.Sc. degree in electrical engineering and the B.A. degree in economics from the University of California, Los Angeles (UCLA), Los Angeles, CA, USA, in 1985. He is currently the Executive Vice President of Sales and Marketing with PolarSat Inc., Montreal, QC, Canada, which he co-founded in 2003. Previously, he held management and engineering positions with NSI Communications, ComStream Corporation, Interstate Electronics, and Hughes Aircraft Company, all in California, USA. He has more than 40 years of experience in wireless and satellite communications and has authored IEEE papers on wireless adaptive routing and error-correction coding, as well as articles on satellite communications in leading industry publications. His current professional interests include satellite networking, adaptive routing, and forward error correction for MF–TDMA systems. |

|

M. Reza Soleymani (Senior Member, IEEE) received the B.S. degree in electrical engineering from the University of Tehran, Tehran, Iran, in 1976, the M.S. degree in electrical engineering from San Jose State University, San Jose, CA, USA, in 1977, and the Ph.D. degree in electrical engineering from Concordia University, Montréal, QC, Canada, in 1987. From 1987 to 1990, he was an Assistant Professor in the Department of Electrical Engineering at McGill University, Montréal, QC, Canada. From 1990 to 1998, he was with EMS Technologies Ltd. (formerly Spar Aerospace Ltd.), where he had a leading role in the design and development of several satellite communications systems. In 1998, he joined the Department of Electrical and Computer Engineering at Concordia University, Montréal, QC, Canada, where he is presently a Professor. His current research interests include digital communications, satellite communications, communications networks, information theory and coding, and data compression and source coding. He holds several patents and has coauthored a book, Turbo Coding for Satellite and Wireless Communications (Kluwer Academic Publishers, 2002), as well as a number of book chapters in the field. |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2026 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license.